目录

1. FPGA实现串行CRC(以CRC 16/XMODEM为例)

2. FPGA实现单个并行CRC(以CRC 16/XMODEM为例)

3. FPGA实现连续并行CRC(以CRC 16/XMODEM为例)

上一篇文章已经介绍了CRC的原理和手推方法,此处不再赘述,如有需要,可上翻哦。

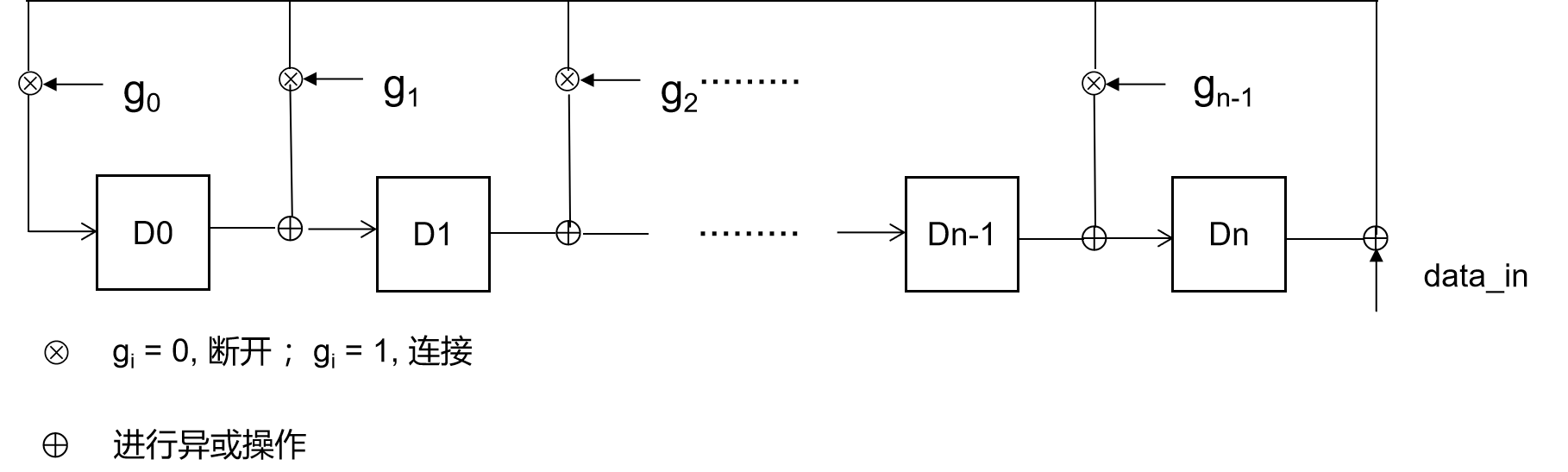

在进行CRC 16 FPGA实现之前,需要理解如何用电路实现CRC算法,一个通用的CRC生成多项式表示为:

根据教材介绍,CRC通用电路可表示如下,因为CRC是除余数算法,所以从右边(高位)输入数据,相当于把信息位data向低位移动。而gn的通断由生成多项式的系数决定,具体可参考接下来介绍的crc_16的生成多项式和电路图。

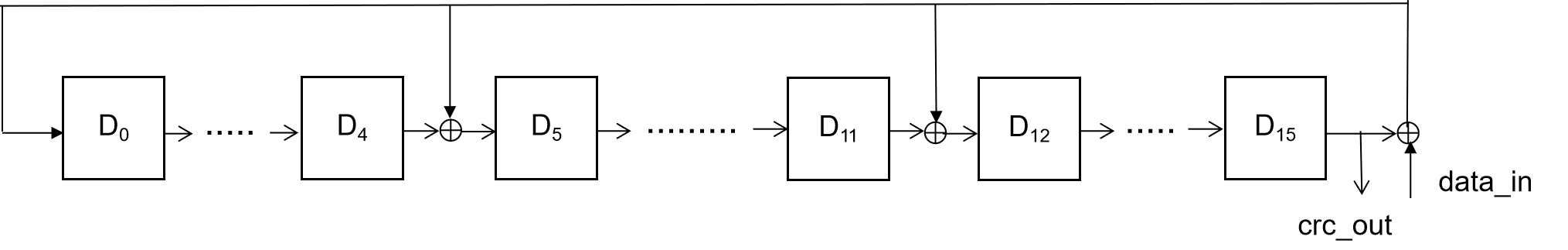

本文重点介绍如何用FPGA实现串行和并行CRC计算,以CRC 16为例展开介绍。CRC 16的生成多项式如下,由多项式可知对应的系数为10001000000100001,故1的数据位表示gn连通,如图中第12、5和第0位处,该比特位的值是由前一比特位和数据位、最高比特位异或后的结果。接下来将以电路图为理解基础,进行Verilog的逻辑实现。

1. FPGA实现串行CRC(以CRC 16/XMODEM为例)

串行CRC是指在进行数据处理时,每个时钟周期只输入一比特的数据,逐比特处理。当所有比特处理完毕后,将处理后的CRC结果输出。

输入的10比特串行测试数据流:10'b1101001110;即10‘h34e;

实现代码、测试脚本和结果展示如下。

module crc_serial_16(

input wire clk , //74.25M时钟

input wire rst ,//高有效复位

input wire i_data , //输入的串行数据

input wire i_data_vld , //串行数据有效标志

output reg [15:0] o_crc_data , //输出的CRC数据

output reg o_crc_vld //CRC数据有效标志

);

//crc_16 = X16 + X12 + X5 + 1

//parameter crc_16_coefficient = 17'b10001000000100001;

reg [15:0] crc_reg;

reg [3:0] data_cnt;

always @(posedge clk) begin

if(rst)

data_cnt <= 4'd0;

else if(i_data_vld)

data_cnt <= data_cnt + 4'h1;

else

data_cnt <= 4'd0;

end

always @(posedge clk) begin

if(rst)

crc_reg <= 16'h0;

else if(i_data_vld) begin

crc_reg [15:13] <= crc_reg[14:12];

crc_reg [12] <= crc_reg [15]^crc_reg [11] ^ i_data;

crc_reg [11:6] <= crc_reg [10:5];

crc_reg [5] <= crc_reg [15]^crc_reg [4] ^ i_data;

crc_reg [4:1] <= crc_reg [3:0];

crc_reg [0] <= crc_reg [15] ^ i_data;

end

else

crc_reg <= crc_reg;

end

always @(posedge clk) begin

if(rst)

o_crc_data <= 16'd0;

else if(data_cnt ==4'd10)

o_crc_data <= crc_reg;

else

o_crc_data <= 16'd0;

end

always @(posedge clk) begin

if(rst)

o_crc_vld <= 1'd0;

else if(data_cnt ==4'd10)

o_crc_vld <= 1'd1;

else

o_crc_vld <= 1'd0;

end

endmodulemodule crc_serial_tb();

reg clk ;

reg rst ;

reg [15:0] i_data ;

reg i_data_vld ;

wire [5:0] o_crc_data ;

wire o_crc_vld ;

parameter CLK_74_25 = 6.734;

initial begin

clk = 1'b0;

forever begin

#CLK_74_25 clk = ~clk;

end

end

//生成数据时钟和传入模块的时钟反相

wire clk_data_gen;

assign clk_data_gen = ~clk;

initial begin

rst = 1'b1;

i_data = 10'b0;

i_data_vld = 1'b0;

#1000

rst = 1'b0;

@(posedge clk_data_gen) begin //9

//i_data = 10'b11_0100_1110; 10'h34e

i_data = 1'b1;

i_data_vld = 1'b1;end

@(posedge clk_data_gen) begin //8

i_data = 1'b1;

i_data_vld = 1'b1; end

@(posedge clk_data_gen) begin //7

i_data = 1'b0;

i_data_vld = 1'b1; end

@(posedge clk_data_gen) begin //6

i_data = 1'b1;

i_data_vld = 1'b1; end

@(posedge clk_data_gen) begin //5

i_data = 1'b0;

i_data_vld = 1'b1; end

@(posedge clk_data_gen) begin //4

i_data = 1'b0;

i_data_vld = 1'b1; end

@(posedge clk_data_gen) begin //3

i_data = 1'b1;

i_data_vld = 1'b1; end

@(posedge clk_data_gen) begin //2

i_data = 1'b1;

i_data_vld = 1'b1; end

@(posedge clk_data_gen) begin //1

i_data = 1'b1;

i_data_vld = 1'b1; end

@(posedge clk_data_gen) begin //0

i_data = 1'b0;

i_data_vld = 1'b1;end

@(posedge clk_data_gen) begin

i_data = 10'b0;

i_data_vld = 1'b0;

end

end

crc_serial_16 crc_serial_test(

.clk (clk) ,

.rst (rst) ,

.i_data (i_data ) ,

.i_data_vld (i_data_vld) ,

.o_crc_data (o_crc_data) ,

.o_crc_vld (o_crc_vld)

);

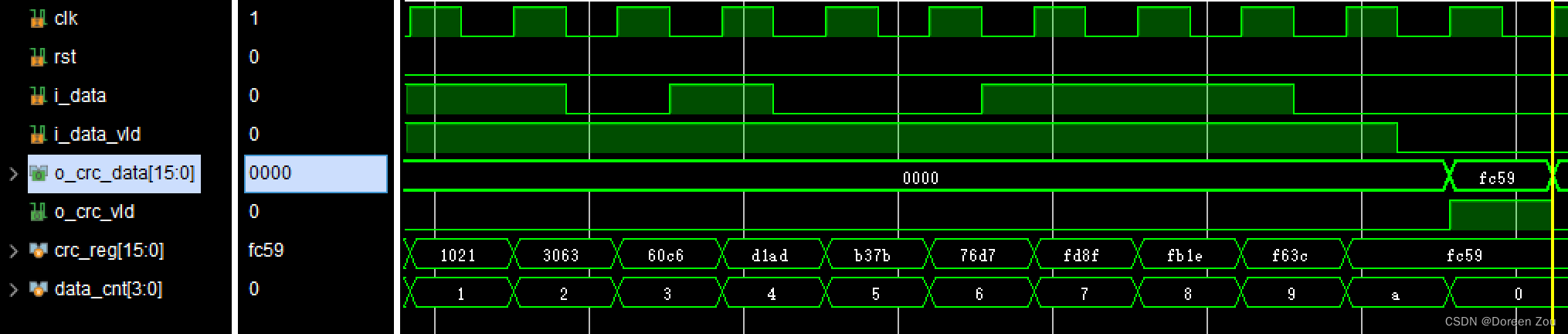

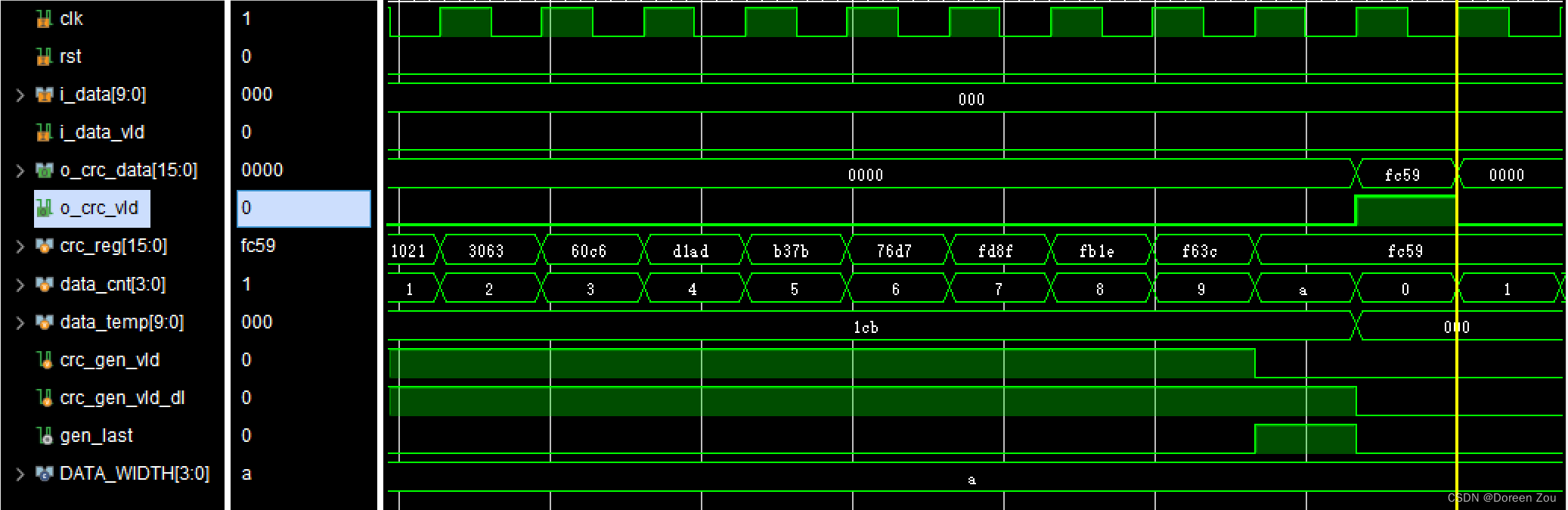

endmodule时序图如下,计算后的CRC_16的结果为"fc59", 符合CRC计算网站中CRC16/XMODEM的计算结果,网站网址和配置项说明见第4节。

2. FPGA实现单个并行CRC(以CRC 16/XMODEM为例)

并行CRC是指在进行数据处理时,每个时钟周期输入大于1比特位宽的数据,但是本人能力有限,仍需 “位宽” 个时钟周期去处理一个并行CRC数据的计算,处理所用的资源及思路与串行CRC类似,并没有实现时间上的节约,整个处理思路请参考程序中的注释。

所以,读者若有其他不借助生成器,可以实现一个时钟周期内处理完成一个并行CRC数据的方法,欢迎留言交流讨论。

module crc_parallel(

input wire clk ,

input wire rst ,

input wire [9:0] i_data , //输入的10比特数据

input wire i_data_vld , //输入数据有效标志

output reg [15:0] o_crc_data , //输出的16比特CRC校验结果

output reg o_crc_vld //输出数据有效标志

);

parameter DATA_WIDTH = 4'd10; //数据位宽

reg [15:0] crc_reg; //CRC计算结果暂存寄存器

reg [3:0] data_cnt;

reg [9:0] data_temp;

reg data_vld_dl;

reg crc_gen_vld;

reg crc_gen_vld_dl;

wire gen_last;

always @(posedge clk) begin //按照数据位宽进行计数

if(rst || (data_cnt > (DATA_WIDTH-1))||i_data_vld)

data_cnt <= 4'd0;

else

data_cnt <= data_cnt + 4'd1;

end

always@(posedge clk) begin //生成CRC运算使能,即数据有多少比特,计算多少个时钟周期

if(rst)

crc_gen_vld <= 1'b0;

else if(i_data_vld)

crc_gen_vld <= 1'b1;

else if(data_cnt==(DATA_WIDTH-1))

crc_gen_vld <= 1'b0;

else

crc_gen_vld <= crc_gen_vld;

end

always@(posedge clk) begin //对CRC运算使能延迟,以生成CRC计算结束标志

crc_gen_vld_dl <= crc_gen_vld;

end

assign gen_last = crc_gen_vld_dl & ~crc_gen_vld;

always@(posedge clk) begin //使输入的数据在运算使能的时钟周期内,保持不变

if(rst)

data_temp <= 10'h0;

else if(i_data_vld)

data_temp <= i_data;

else if(gen_last)

data_temp <= 10'h0;

else

data_temp <= data_temp;

end

always @(posedge clk) begin //根据CRC_16的电路图开始计算

if(rst) begin

crc_reg <= 16'h0;

end

else if(crc_gen_vld) begin

crc_reg [15:13] <= crc_reg[14:12];

crc_reg [12] <= crc_reg [15]^crc_reg [11] ^ data_temp[data_cnt];

crc_reg [11:6] <= crc_reg [10:5];

crc_reg [5] <= crc_reg [15]^crc_reg [4] ^ data_temp[data_cnt];

crc_reg [4:1] <= crc_reg [3:0];

crc_reg [0] <= crc_reg [15] ^ data_temp[data_cnt];

end

else

crc_reg <= crc_reg;

end

always @(posedge clk) begin//输出CRC计算结果

if(rst)

o_crc_data <= 16'd0;

else if((data_cnt ==4'd10) && gen_last)

o_crc_data <= crc_reg;

else

o_crc_data <= 16'd0;

end

always @(posedge clk) begin //输出CRC输出使能

if(rst)

o_crc_vld <= 1'd0;

else if((data_cnt ==4'd10) && gen_last)

o_crc_vld <= 1'd1;

else

o_crc_vld <= 1'd0;

end

endmodulemodule crc_parallel_tb( );

reg clk ;

reg rst ;

reg [9:0] i_data ;

reg i_data_vld ;

wire [5:0] o_crc_data ;

wire o_crc_vld ;

parameter CLK_74_25 = 6.734;

initial begin

clk = 1'b0;

forever begin

#CLK_74_25 clk = ~clk;

end

end

//生成数据时钟和传入模块的时钟反相

wire clk_data_gen;

assign clk_data_gen = ~clk;

initial begin

rst = 1'b1;

i_data = 10'b0;

i_data_vld = 1'b0;

#500

rst = 1'b0;

@(posedge clk_data_gen) begin //0

i_data = 10'b11_0100_1110; 10'h34e

i_data = 10'b0111001011;//做了比特翻转,取数时从比特0(高位)先取,实现高位在前、低位在后

i_data_vld = 1'b1;

end

@(posedge clk_data_gen) begin

i_data = 10'b0;

i_data_vld = 1'b0;

end

end

crc_parallel crc_parallel_test(

.clk (clk) ,

.rst (rst) ,

.i_data (i_data ) ,

.i_data_vld (i_data_vld) ,

.o_crc_data (o_crc_data) ,

.o_crc_vld (o_crc_vld)

);

endmodule

3. FPGA实现连续并行CRC(以CRC 16/XMODEM为例)

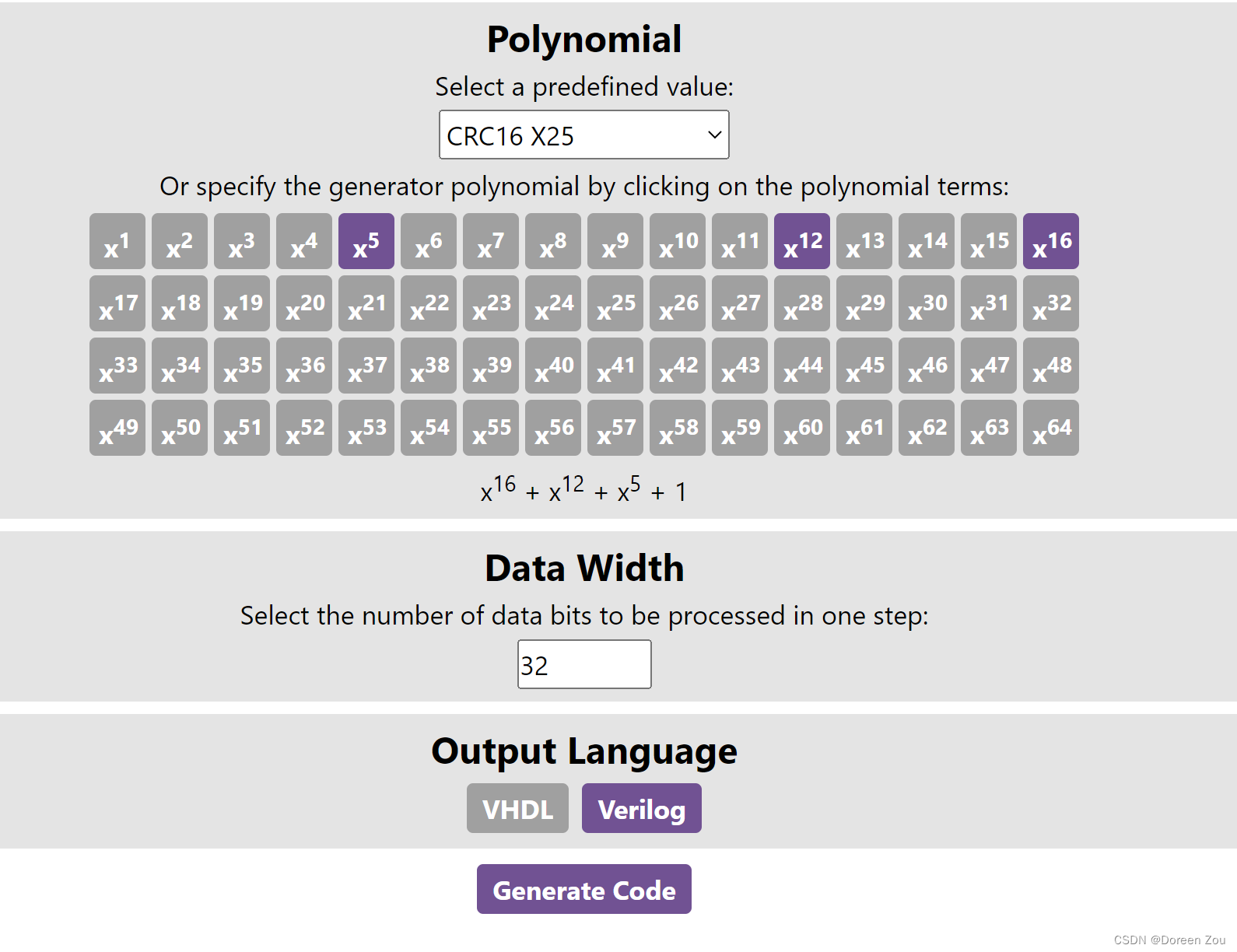

在实际应用中,通常需要对连续数据流做CRC校验,因此学会如何实现连续数据流的CRC实现更加有实际意义。而在处理连续数据流时,若仍然使用以上方法,会浪费大量的时间,为解决以上问题,需要用到一些CRC 代码生成器。

生成器界面如下,可以选择列表中已经存在的公式,也可以根据生成多项式自由选择公式,选择好生成多项式后输入数据位宽,点击生成后,会自动下载一个基于Verilog的CRC逻辑文件,见下文。

注意:文档中标注的convention: the first serial bit is D[9],表示此代码会把高位作为异或位输出,若需求与此相反,只需将代码中的d[0]改为d[15]、d[1]改为d[14]以此类推。

module CRC16_D10;

// polynomial: x^16 + x^12 + x^5 + 1

// data width: 10

// convention: the first serial bit is D[9]

function [15:0] nextCRC16_D10;

input [9:0] Data;

input [15:0] crc;

reg [9:0] d;

reg [15:0] c;

reg [15:0] newcrc;

begin

d = Data;

c = crc;

newcrc[0] = d[8] ^ d[4] ^ d[0] ^ c[6] ^ c[10] ^ c[14];

newcrc[1] = d[9] ^ d[5] ^ d[1] ^ c[7] ^ c[11] ^ c[15];

newcrc[2] = d[6] ^ d[2] ^ c[8] ^ c[12];

newcrc[3] = d[7] ^ d[3] ^ c[9] ^ c[13];

newcrc[4] = d[8] ^ d[4] ^ c[10] ^ c[14];

newcrc[5] = d[9] ^ d[8] ^ d[5] ^ d[4] ^ d[0] ^ c[6] ^ c[10] ^ c[11] ^ c[14] ^ c[15];

newcrc[6] = d[9] ^ d[6] ^ d[5] ^ d[1] ^ c[7] ^ c[11] ^ c[12] ^ c[15];

newcrc[7] = d[7] ^ d[6] ^ d[2] ^ c[8] ^ c[12] ^ c[13];

newcrc[8] = d[8] ^ d[7] ^ d[3] ^ c[9] ^ c[13] ^ c[14];

newcrc[9] = d[9] ^ d[8] ^ d[4] ^ c[10] ^ c[14] ^ c[15];

newcrc[10] = d[9] ^ d[5] ^ c[0] ^ c[11] ^ c[15];

newcrc[11] = d[6] ^ c[1] ^ c[12];

newcrc[12] = d[8] ^ d[7] ^ d[4] ^ d[0] ^ c[2] ^ c[6] ^ c[10] ^ c[13] ^ c[14];

newcrc[13] = d[9] ^ d[8] ^ d[5] ^ d[1] ^ c[3] ^ c[7] ^ c[11] ^ c[14] ^ c[15];

newcrc[14] = d[9] ^ d[6] ^ d[2] ^ c[4] ^ c[8] ^ c[12] ^ c[15];

newcrc[15] = d[7] ^ d[3] ^ c[5] ^ c[9] ^ c[13];

nextCRC16_D10 = newcrc;

end

endfunction

endmodule基于Verilog的CRC逻辑生成器网址如下:

Easics CRC Tool http://crctool.easics.be/

http://crctool.easics.be/

4. CRC计算网站

实践中常用的CRC公式有很多种,若有某个数据CRC验证需求,可到以下网站验证,网址:

CRC(循环冗余校验)在线计算_ip33.com http://www.ip33.com/crc.html

http://www.ip33.com/crc.html

网站中涉及的x16+x12+x5+1(0x1021)相关多项式,计算差异点如下,供参考。

CRC16_CCITT:初始值0x0000,低位在前,高位在后,结果与0x0000异或;

CRC16_CCITT-FALSE:初始值0xffff,低位在后,高位在前,结果与0x0000异或;

CRC16_XMODEM:初始值0x0000,低位在后,高位在前,结果与0x0000异或;

CRC16_X25:初始值0x0000,低位在前,高位在后,结果与0xffff异或;

验证

以上为个人对CRC的理解和学习笔记,如有考虑不足之处,欢迎沟通交流!

本文详细介绍FPGA中CRC16的串行、并行及连续并行实现方法,包括Verilog代码示例及测试过程,同时提供CRC计算网站验证结果。

本文详细介绍FPGA中CRC16的串行、并行及连续并行实现方法,包括Verilog代码示例及测试过程,同时提供CRC计算网站验证结果。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?