SD和MMC接口有许多不同的方面,要充分利用这项技术的优势并将其正确地应用于新设计和应用中,必须了解这些接口的不同特性。

SD存储接口

Secure Digital(SD)存储卡首次亮相于2000年CES贸易展览会。十年之内,它已成为消费类应用中最流行的非易失性可移动数据存储介质。SD存储属于可移动数据存储设备的同一类别,其中包括PC卡、PCMCIA卡、CompactFlash、SmartMedia、多媒体卡(MMC)、记忆棒(Memory Stick)和xD卡。这类可移动数据存储设备并非旨在取代硬盘,它们的容量和速度性能仅为硬盘的一小部分,但其体积更小,单价也更低。SD设备通常可见于数码相机、摄像机、手机、打印机、笔记本电脑、汽车导航和其他应用中。

什么促成了SD卡的成功

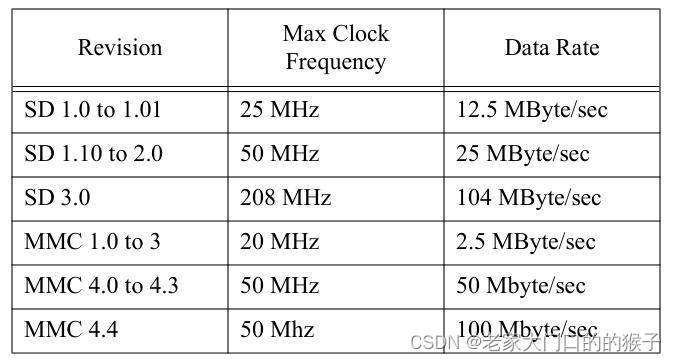

虽然PCMCIA主要为笔记本电脑开发,但SD卡及其其他竞争设备则面向消费类电子产品,如相机和手机。与早期的PCMCIA和CompactFlash卡相比,SD卡的物理引脚相对较少(5个信号引脚加上时钟和电源)。数据传输速率从25 MHz(早期版本)到208 MHz(最新版本),使得它可以通过成熟的技术以较低成本制造。同时,同步数据传输协议非常高效,使SD卡能够满足大多数数字和视频应用的足够数据带宽需求。小尺寸、低成本、良好性能以及由多个主要制造商支持作为开放标准的结合,使得SD卡成为消费类电子产品数据存储的事实标准。

多媒体卡 (MMC)

MMC(多媒体卡)与SD卡密切相关。MMC标准比SD标准早出台几年。两个标准共享许多共同特性,具有相同的物理和电气规范。它们之间的差异主要体现在软件层面的命令上。由于相似性,许多主机可以在同一个插槽中同时接受MMC和SD卡。

基本的SD协议

SD总线通过双向的CMD和DATA引脚以串行方式传输信息。每个命令包包含48位的信息通过CMD引脚发送。命令包包括命令索引、参数和CRC校验位。命令总是由主机发送,响应则由卡通过CMD引脚发送。大多数响应包也是48位长。主机总是命令的发起者,卡总是命令的目标。并非所有命令都有数据传输,只有读写命令才伴随数据传输。数据包的单位称为块。不同的块大小可以由主机定义,大多数数据块大小为512字节。数据可以通过1根或全部4根数据引脚传输。每个数据包后面跟着16位的CRC数据。SD命令处理高度依赖于状态,卡在任何给定时间总是处于特定的操作状态。在特定状态下,只有某些命令是有效的。主机通过初始化命令序列改变卡的操作状态,直到卡准备好传输数据。命令和数据传输通过主机生成的时钟信号进行同步。复位后的初始阶段,主机使用最低的时钟频率400 KHz与卡通信。卡内部寄存器提供与卡能力相关的信息给主机。通过了解最大操作频率、数据总线宽度及其他能力信息,主机会提高时钟频率以实现最佳性能。

SD和MMC规格的不同版本有哪些

SD规范由SD协会发布。SD协会的创始成员是松下、闪迪和东芝。目前,SD协会有约1000家会员公司。第一个版本,1.0版,于2000年3月发布。这个基础版本支持25 MHz的总线频率和最大2 GB的卡容量。数据可以通过SD模式(1-bit和4-bit数据选择)和向下兼容的SPI模式(仅1-bit)进行传输。SD接口的第二次主要修订版于2006年5月发布,增加了高容量SD(SDHC)规范,将最大卡容量提高到32 GB。虽然这一修订版的更改不多,但SDHC为未来的修订奠定了基础。新增的卡容量(4 GB、8 GB和16 GB)适用于大多数照片和视频应用。即使在3.0版本引入了更大容量后,SDHC仍然是市场上主要的卡容量。

SD规范的3.0版本增加了新的容量标准SDXC,支持每张卡最高2 TB,并通过引入超高速(UHS-I)规范提高了数据带宽。使用相同的4引脚接口,UHS-I支持最高208 MHz的单数据速率,提供104 MByte/sec的数据速率,并支持最高50 MHz的双数据速率,提供50 MByte/sec的数据速率。版本4.0正在由SD协会审查,预计将在2011年发布。版本4.0增加了UHS-II速度版本,将数据速率提高到比3.0版本更高的水平。

MMC规范最初由西门子和闪迪于1996年开发。该规范由MMC协会控制,直到2008年。从2008年起,规范和新版本由JEDEC控制。版本2.0于1999年发布,随后在2001年发布了版本3.0。SD 1.0规范与MMC版本2.11正式兼容。版本4.0于2003年引入了4-bit和8-bit数据宽度。8-bit数据宽度使MMC在相同速度下的数据带宽是SD的两倍。然而,许多主机不支持8-bit数据宽度,4-bit数据宽度仍然是与可移动卡进行通信时最广泛使用的数据宽度。在JEDEC接管MMC规范后,嵌入式MMC(eMMC)作为版本4.3推出。eMMC用于板载应用,其中eMMC设备安装在印刷电路板(PCB)上。除了机械形态之外,eMMC和MMC共享相同的特性和功能。最新的eMMC规范是版本4.41。自版本4.4起,支持引导模式,使设备可以用作引导ROM。还引入了DDR数据速率。最高带宽为50 MHz运行的8-bit DDR,提供100 MByte/sec的数据速率,相当于SD卡在4倍时钟速率下的数据速率。以下表格总结了不同版本的总线的数据速率。

性能:带宽与速度等级

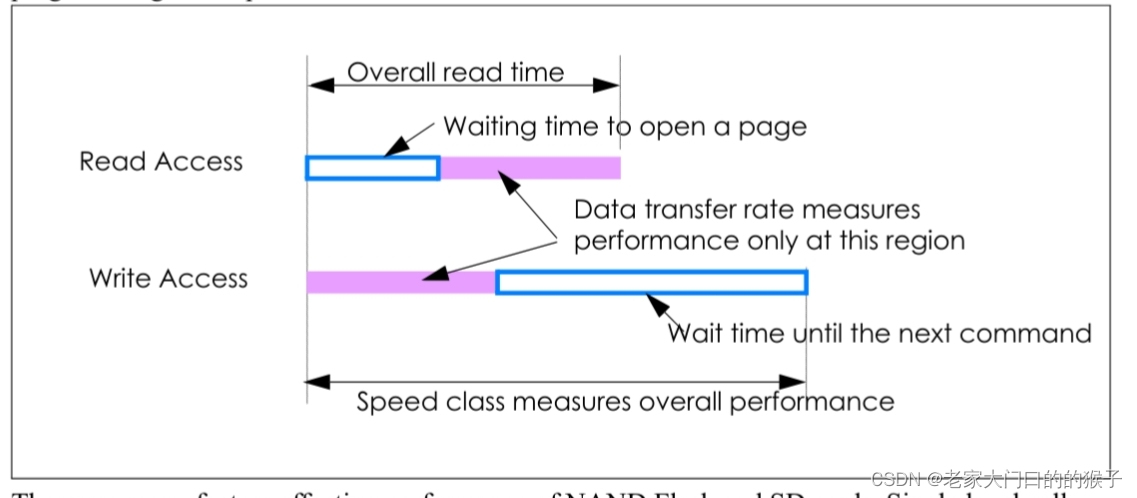

最大数据传输速率(SD为104 MByte/sec,eMMC为100 MByte/sec)并不总是设备性能的真实衡量标准。数据速率仅指在传输数据时的性能,并不能显示在发出命令后,主机需要等待多长时间才能开始初始数据传输。等待时间越长,可用带宽越低。对于持续的数据传输,减少响应时间与提高时钟速率同样重要。

由于卡中的数据存储是由NAND闪存单元实现的,因此最终性能受限于内存技术以及内存架构。读取NAND闪存中的数据时,需要先打开页,这个过程需要几微秒的等待时间。在页面打开之前,无法读取数据。对于NAND闪存的写入,页面传输到设备后,编程数据到NAND闪存中需要几百微秒到几毫秒的时间。编程完成之前,可能不允许进行新的操作。

有许多因素影响NAND闪存和SD卡的性能。单层单元(SLC)NAND闪存相比于多层单元(MLC)NAND闪存具有更短的页打开时间和编程时间,但MLC提供更大的容量和更低的每比特价格。多通道架构通过重叠一个通道的页打开和编程时间与另一个通道的数据传输时间,从而提高性能,减少整体停机时间。其他因素,如控制器效率和错误修正算法,也会影响性能。

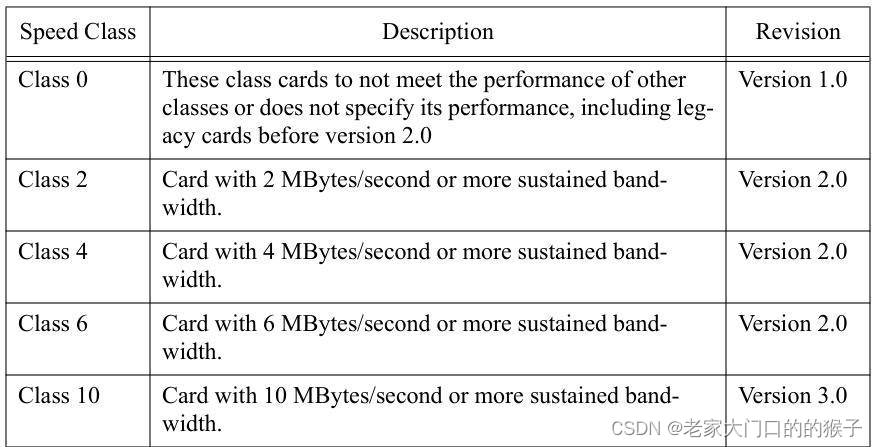

为了给用户提供SD卡实际可用性能的真实衡量标准,自2.0版本以来,SD规范定义了几个速度等级,每张卡必须属于其中一个等级。

可以看到,由时钟频率定义的数据传输速率与由速度等级定义的持续带宽之间存在较大差异。这些差异反映了NAND闪存存储技术的性能,而不是SD总线协议的限制。同样,通过改进内存设计而不是使用SD总线的最高时钟频率,可以提高SD卡设计的性能。

SDIO和SD组合

SD总线规范定义了三种卡类型:仅内存卡、IO卡(SDIO)和结合内存与IO功能的卡(SD组合)。SDIO是SD规范的扩展,专为仅IO设备设计。在SDIO规范中定义了新的命令,同时移除了一些仅内存的功能。例如,SD内存卡有一个编程状态,用于表示NAND闪存设备的编程状态(除了读取和写入)。而SDIO设备没有编程状态。不同的IO功能,如SDIO Wi-Fi或蓝牙控制器,可以在SDIO卡格式中实现。SDIO规范支持多功能架构,每个功能可以独立操作并拥有自己的内存空间。最小功能数为1,最大为8。典型的SDIO卡有两个功能:功能0是系统功能,功能1是用户功能。SD组合卡顾名思义,包含了SD内存和SDIO功能。它不如仅SD内存卡或仅SDIO设备那样常用。

SD总线架构

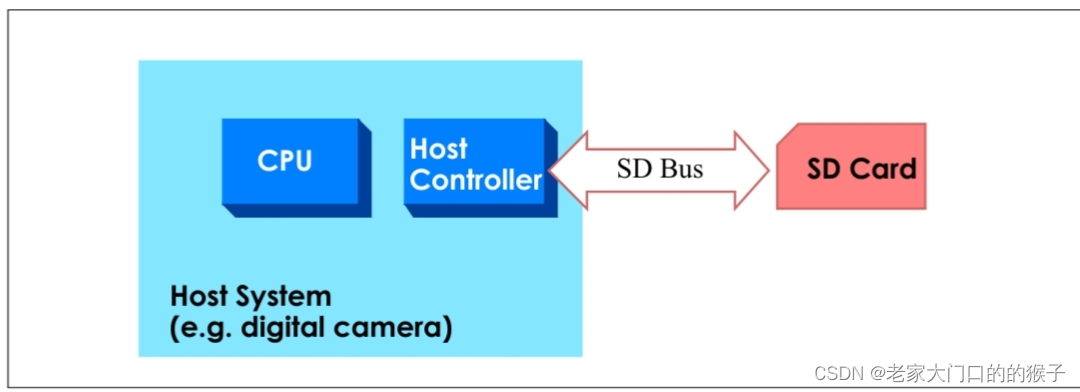

上述图示展示了一个典型的SD总线系统,包括主机控制器和SD卡。尽管SD规范允许将多个SD卡连接到同一个SD总线,但在实际应用中,大多数系统设计仅使用单个卡。可以合理假设,大多数SD总线系统只有一个主机(发起者)和一个卡(从属设备)。SD总线上的信号包括由主机生成的时钟引脚、一个双向的CMD(命令)引脚和1或4个双向的DT(数据)引脚。

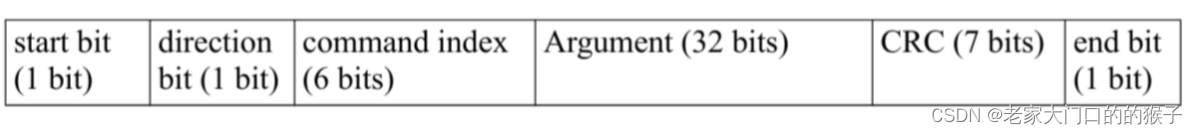

所有SD总线事务都由主机通过CMD引脚发起。所有CMD和DT信号都与时钟信号同步。每个命令是一个48位的数据包,由主机通过CMD引脚串行输出。以下是命令数据包的格式。

某些命令需要SD卡的响应,而有些则不需要。有些命令需要在DT引脚上传输数据,而有些则不需要。如果命令需要响应,SD卡会在接收到命令后的64个时钟周期内通过CMD引脚串行输出响应数据包。每个命令的响应数据包格式都是预定义的。大多数响应为48位,而某些响应为136位。

如果命令涉及数据传输,数据将在DT引脚上串行传输。写入数据从主机传输到卡,而读取数据从卡传输到主机。每个数据包由一个起始位、数据位、16位的CRC和一个结束位组成。数据位的大小要么由命令隐含决定,要么由主机通过先前的命令定义。

SD总线规范规定了SD总线上的物理信号接口、每个命令和响应的定义、SD卡内的一组标准寄存器、卡的内部状态和状态信息以及初始化和启用总线上数据传输的命令序列。

SD总线规范并未定义SD或SDIO卡内存或IO设备的类型。尽管SD内存基于NAND闪存技术,但只要遵循命令协议,规范中并没有阻止使用其他类型的非易失性存储器。同样,SDIO规范也不限制在SDIO卡中实现的IO设备类型。

SD主机控制器

SD主机控制器是连接主机CPU和SD总线的硬件逻辑桥梁。SD总线规范的主机规范部分对主机控制器设计进行了非常严格的定义。该规范确保了CPU对主机控制器的统一软件视图,使得相同的驱动程序软件可以用于不同的主机控制器硬件。

从CPU的角度来看,主机控制器由一个映射到系统内存或IO空间的256字节寄存器集组成。SD总线上的事务由软件通过读取或写入该寄存器集发起。通过这个寄存器集,主机驱动软件可以执行以下操作:

- 检测SD卡的插入或移除

- 打开和关闭SD卡的电源

- 启用、禁用并控制SD时钟速度

- 定义命令参数并向SD卡发送命令

- 接收来自SD卡的命令响应

- 从SD卡读取数据并向SD卡写入数据

- 暂停、恢复和终止数据事务

- 在不同类型的事件(如命令完成、CRC错误)时中断CPU。

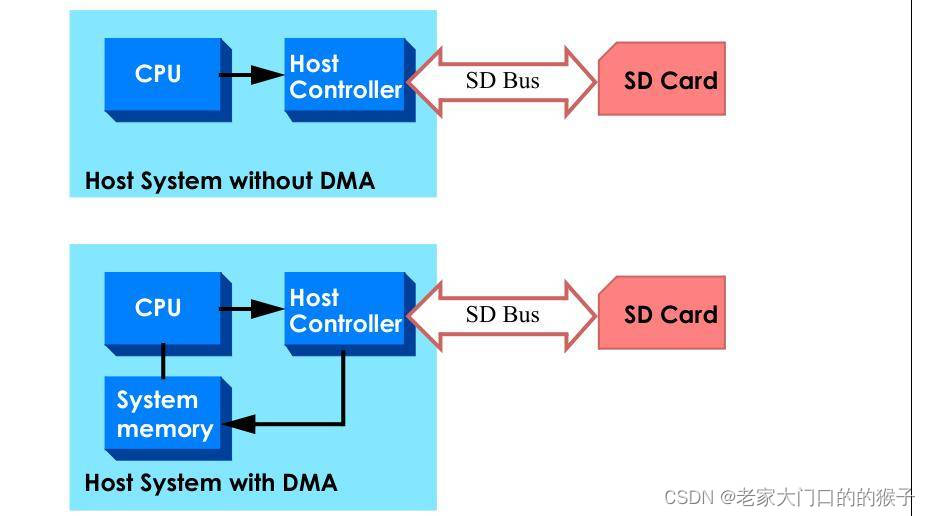

主机控制器还可以包括DMA支持。没有DMA时,主机CPU必须读取或写入与SD卡传输的每一个数据字,这会占用CPU大量的处理能力。而当主机控制器中包含DMA引擎时,CPU只需要设置数据传输。一旦数据传输开始,DMA引擎将负责在SD总线与系统内存之间读取/写入每一个数据字,从而释放CPU用于系统中的其他任务。DMA完成时可以向CPU发送中断。DMA是一种非常高效的数据传输方式,但它要求主机控制器能够访问系统内存。下图展示了带有和不带有DMA支持的两种主机设计的比较。

电气和时序控制

主机系统负责为SD卡提供电源和时钟信号。SD规范中定义了几种卡检测机制,允许SD卡的热插拔。在插入卡时可以生成中断。收到卡插入中断后,CPU可以通过主控制器中的电源控制寄存器为SD卡启用电源。在典型设计中,电源控制信息从控制器逻辑转发到系统的电源控制单元。SD卡的默认电源供应为3.3V。

主控制器还负责为SD卡生成时钟信号。启用电源后,系统软件可以以默认的400 KHz频率为SD卡启用时钟信号。初始化序列在此频率下运行,直到软件通过卡的控制寄存器检测到卡的频率和总线宽度能力。

主机CPU可以在没有操作时停止时钟信号和/或断开卡的电源以节省能源。SD卡无法对其时钟信号使用锁相环(PLL)。

SD卡设计包含的内容

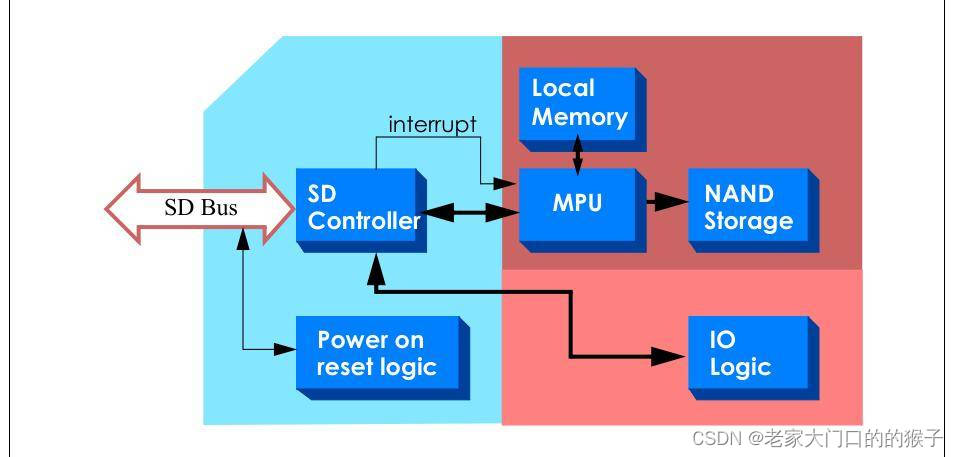

上述图示展示了典型的SD卡设计,包括SD内存和SDIO功能。对于SD内存的实现,它包含基于NAND闪存的存储,通常由带有本地内存的MPU管理,用于程序执行。典型的SDIO实现包括SD接口和IO功能逻辑块。IO逻辑块中可能也包含MPU。

图中的SD控制器处理所有物理和数据链路层功能,如命令解码、响应生成、CRC、状态管理和预定义的SD寄存器集。许多SD命令可以直接由SD控制器模块处理。对内存空间的访问会从SD控制器转发到卡中的其他模块。

在大多数NAND闪存设计中,对NAND闪存的访问需要通过本地处理器,该处理器处理磨损均衡和坏块管理。SD控制器不会直接访问NAND闪存芯片。它要么访问本地系统中的影像内存进行数据传输,要么中断本地处理器,由其处理必要的数据传输。当MPU接收到中断时,它会查询SD控制器模块以了解来自SD总线的数据请求。如果是读取请求,它会从NAND闪存中检索数据并将读取数据存储到SD控制器模块。如果是写入请求,它会从SD控制器模块中检索数据并将其写入NAND闪存。

对于SDIO设备,根据实现的IO逻辑的性质,SD控制器核心可以直接访问IO逻辑,当SD总线有用户数据传输请求时,或者使用与SD内存相同的中断方法请求IO逻辑服务。SD规范并未规定SD卡的内部架构。设计师可以自由选择最适合应用的架构。然而,合理预期的是,中断方法在SD内存卡设计中更为常用,而直接访问方法在SDIO卡设计中更为常见。

尽管SD规范针对NAND闪存存储技术,但许多NAND闪存特定的特性在SD规范中并未定义。例如,NAND闪存内存所必需的错误校正码(ECC)在SD规范中没有定义。磨损均衡和坏块管理也没有定义。SD内存卡的设计者应遵循NAND闪存制造商的要求来实现这些设计。

什么是SPI,它与SD和MMC有什么关系?

串行外设接口(SPI)在SD和MMC出现之前已经存在很多年。它最初出现在摩托罗拉和其他公司开发的微处理器中。该硬件接口非常简单,与SD总线有些类似,只是信号是单向的,并且仅支持1位数据。

SD和MMC总线最初都支持SPI模式,这样配备了SPI端口的微处理器可以通过添加软件驱动程序与SD卡进行通信。

对于SD主机,SPI模式不是必需的,因为任何设计用于SD总线的主机都应该实现SD总线协议,而不是性能较低的SPI协议。从MMC版本4.3开始,不再需要SPI支持。然而,SD卡仍然要求支持SPI模式。

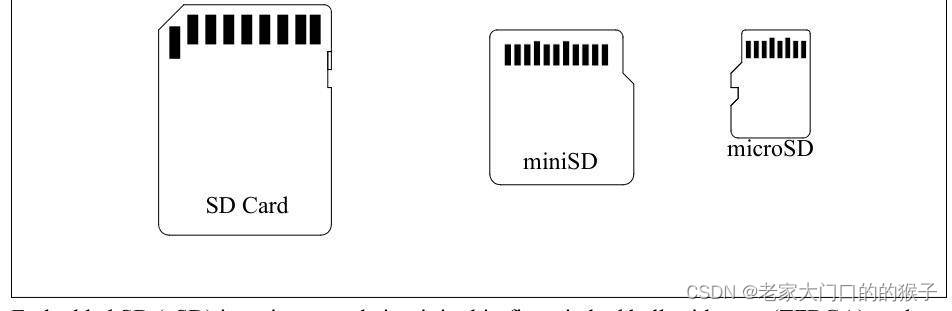

SD卡与miniSD、microSD和嵌入式SD有什么区别?

SD规范允许三种物理尺寸的SD卡:常规尺寸、miniSD和microSD。这三种尺寸在逻辑和功能定义上都是相同的,区别仅在于卡的物理尺寸。常规尺寸的SD卡为24mm x 32mm x 1.4mm,通常用于数字相机应用。miniSD卡为20mm x 21.5mm x 1.4mm。microSD卡是三者中最小的,为11mm x 15mm x 0.7mm,通常用于手机中。由于microSD卡在所有三个维度上都比其他两种格式小,因此许多制造商提供microSD转miniSD和microSD转SD的适配器,以便在所有三种格式的设备中使用microSD卡。

嵌入式SD(eSD)是一种集成电路,采用薄型细间距球栅阵列(TFBGA)封装。它设计为焊接在印刷电路板(PCB)上,不可拆卸。eSD是SD规范的扩展,eSD设备在功能和电气特性上与SD设备在嵌入式环境中有一些区别。

MMC的嵌入式版本是eMMC。从版本4.3开始,eMMC与MMC共享相同的规范。MMC规范中有一些特性,如启动模式,增强了设备在嵌入式应用中的功能。

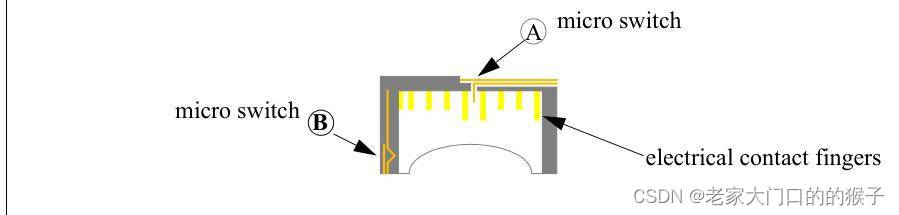

如何处理卡的插入、移除和写保护?

SD规范支持热插拔和写保护。系统可以通过几种方式检测卡片的插入和移除。最常见的方法是使用SD插槽中的机械开关。大多数SD插槽除了用于信号引脚的电气接触外,还包含两个微型开关。在下图中,微型开关A在卡片移除时是打开的,插入卡片时是关闭的。微型开关B与卡片上的写保护开关对齐。如果卡片上的开关处于读写位置,则微型开关B在卡片插入时是关闭的。如果卡片上的开关处于写保护位置,则微型开关B在卡片插入时是打开的。插槽中有九个电气接触点与卡片匹配。中间的两个较长的触点用于电源和接地,以确保电源和接地信号首先与卡片连接,最后断开。

SD卡上的写保护开关只是一个机械开关。它可以在正常和写保护位置之间滑动,但没有电气连接。写保护仅通过上述微型开关被主机检测,主机软件有责任防止对写保护卡的写入。

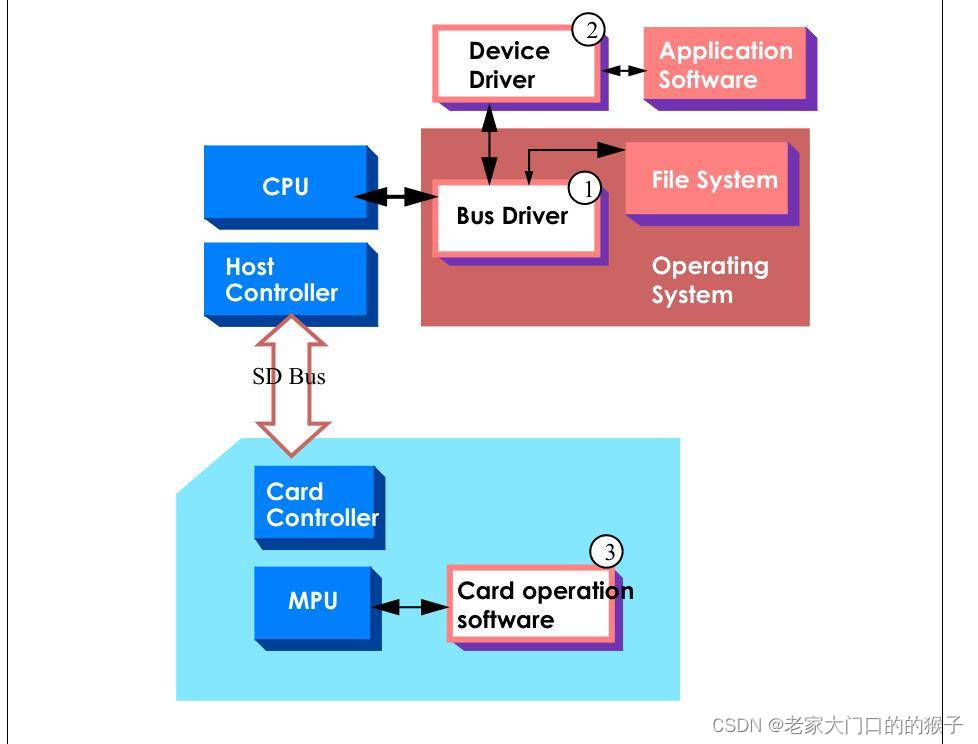

软件要求是什么?

根据讨论的上下文,SD软件可能指三种不同的内容。如上图所示,它可以指:(1) 操作系统模块,该模块处理SD设备的初始化和低级信号传输;(2) 运行在操作系统上的设备驱动程序,用于执行设备的特定应用功能;或 (3) 在SD卡内部的本地微处理器上运行的软件。

为了在系统中启用SD总线,操作系统必须支持SD,因此模块1必须存在于系统中。大多数操作系统都具有此类支持。像Windows和Linux这样的操作系统不仅具备基本的模块1功能,还将其连接到文件系统中。当插入SD存储卡时,操作系统会自动为该卡分配一个驱动器号,可以像磁盘驱动器一样用于文件传输。在这种应用中,系统开发人员不需要为主机开发任何软件。

如果SD卡未配置为标准SD存储设备,或者操作系统未将SD设备连接到文件系统中,则需要软件模块2。例如,如果它是具有用户特定功能的SDIO卡,操作系统只能检测卡的存在并完成初始化序列。特定的应用软件和设备驱动程序将需要与该卡通信,以执行所需的功能。

软件模块3通常存在于SD存储卡中,它是卡开发者的关注点,与主机开发者无关。这是由本地处理器运行的软件,用于提供卡的功能。如果卡是SD存储卡,这个软件包括中断服务程序,用于处理卡控制器的中断请求,以及用于NAND Flash设备的磨损均衡和坏块管理软件。如果它是SDIO设备,则软件可能是提供特定IO功能所需的内容。卡内部的架构和软件不由SD规范定义,因此没有标准可遵循,除了内部模块施加的要求外。通常,这个软件模块是为每个设计定制的。

文件系统在哪里

严格来说,SD存储卡设备并不具备文件系统。SD存储卡向主机呈现的是一个扁平的存储空间。然而,SD规范为主机系统定义了文件系统。在这个扁平的存储空间上构建文件系统是主机系统的责任。SD存储卡对文件系统是无感知的。SD存储卡的文件系统基于微软的FAT和exFAT文件系统规范。该文件系统规范允许不同的主机设备通过SD存储卡交换数据。

由于文件系统仅存在于主机系统中,主机可以完全绕过文件系统,按照它选择的任何自定义数据格式来访问SD存储空间。在这种情况下,除非其他主机了解这种自定义数据格式,否则它们将无法访问该SD存储卡。

720

720

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?