CPU Handling

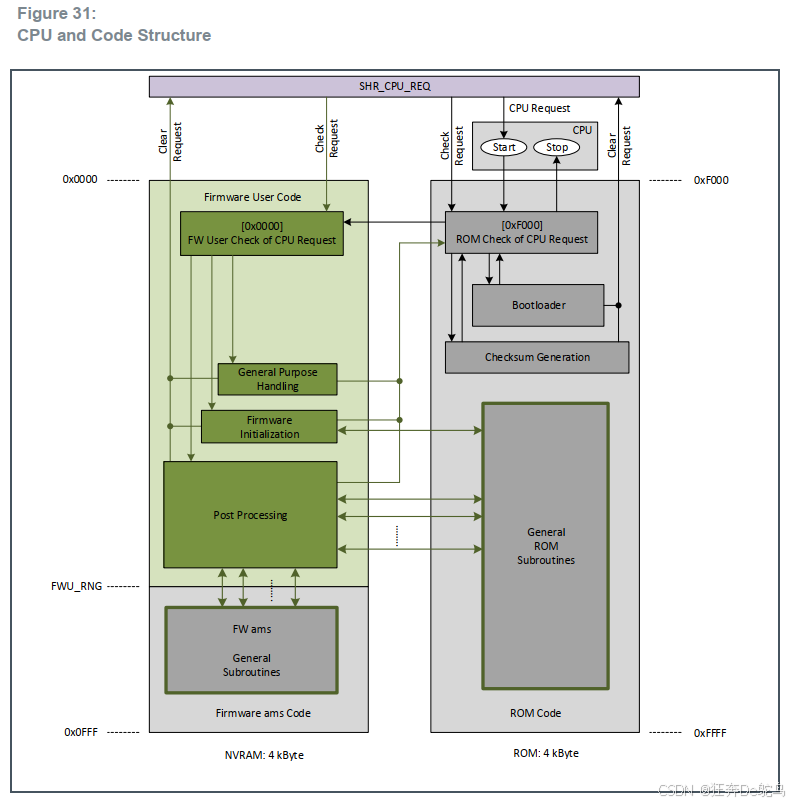

CPU处理通过寄存器SHR_CPU_REQ执行。在那里,以下请求可以开始在CPU中执行程序代码:

- Bootloader

- Checksum Generation(生成校验和请求)

- Firmware Initialization(固件初始化)

- Post Processing(后置处理请求)

- General Purpose Handling(通用处理请求)

通常,通过在SHR_CPU_REQ中设置相应的位来发送这些请求中的任何一个,可以让芯片在任务定序器周期内的适当位置启动CPU。然后,通过检查请求,固件操作总是在ROM代码内开始。

引导加载程(Bootloader)序和校验和生成请求(Checksum Generation)直接在ROM事务中处理,而对于固件初始化、后处理(Post Processing)和通用处理(Post Processing),固件用户代码始终在程序启动时启动。

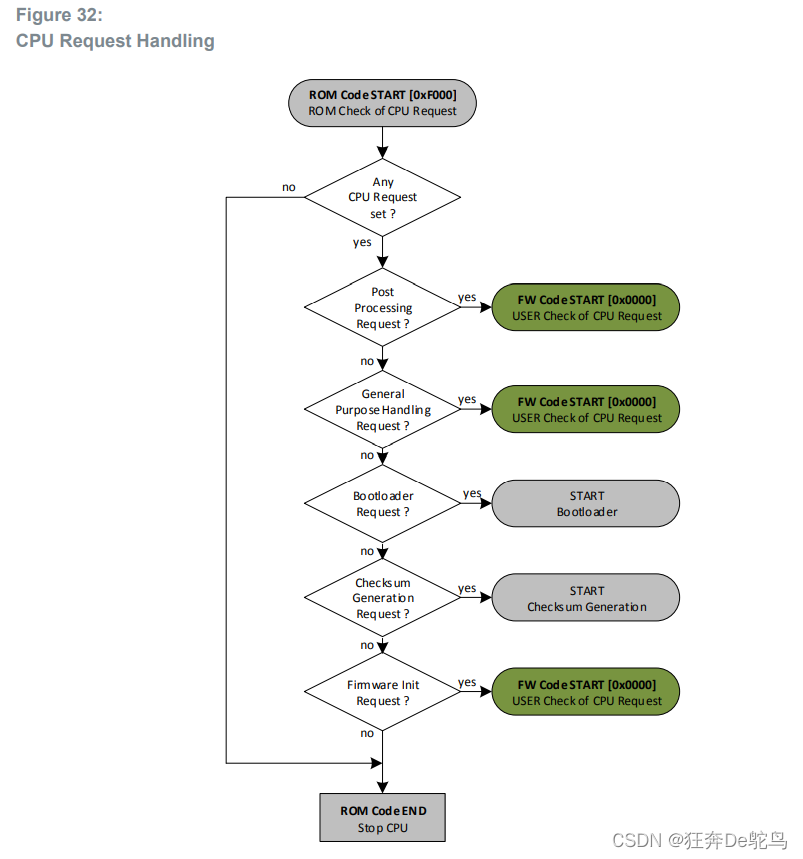

以下图示展示了可能由CPU请求触发的不同序列。这些序列将在后续章节中做更详细的说明。如需了解更多关于CPU和ams固件的信息,请参阅手册GP30_Vol2和GP30_Vol4。

绿色显示的程序代码可由客户定义和编程,同时客户也可以使用ams固件代码中的一些公共子程序或部分ROM代码。如果使用未经修改的ams固件,则客户无需进行任何编程。

Check of CPU Request

如果在SHR_CPU_REQ中设置了任何请求,CPU首先在ROM代码中启动,并检查请求类型。

如果设置了引导加载程序或校验和生成请求,则这些请求将直接在ROM代码中提供

对于其他3个CPU请求,必须在固件代码中处理检查,用户可以在其中定义应在哪个固件代码位置处理请求。

有关固件开发的更多信息,请参阅“Firmware User Guide GP30_Vol4”

| Register | Address | Parameter |

| SHR_CPU_REQ | 0x0DC | CPU Requests |

Bootloader介绍

系统重置或系统INIT发生后,总是请求引

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

725

725

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?