1. ECC

MIPI CSI-2 采用 24-bit 的 ECC 方案。输入24bit数据,进行ECC编码,得到8bit ECC结果。

注意:ECC 字节的第 7 和第 6 位必须为 0。

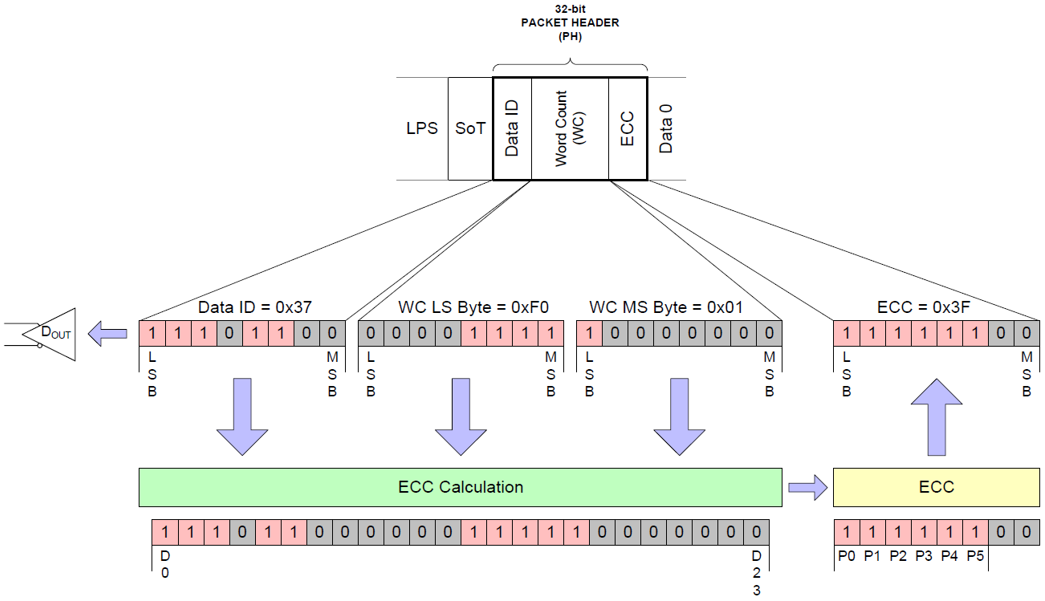

数据映射关系:

包头的数据标识符 DI[7:0] → 对应 ECC 输入的 D[7:0]

包头的字计数低字节 WC[7:0] → 对应 ECC 输入的 D[15:8]

包头的字计数高字节 WC[15:8] → 对应 ECC 输入的 D[23:16]

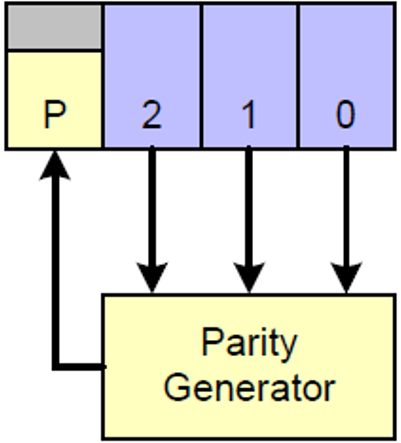

下图的ECC计算实例,展示了数据映射关系:

Figure.1 24-bit ECC Generation Example

1.1 Hamming Code

采用Hamming Code汉明码进行ECC计算。

汉明码(Hamming Code)是一种用于错误检测和纠正的编码技术,它可以自动修正1bit 错误,并检测2bit及以上的错误。

编码规则:

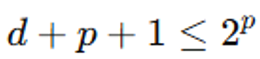

汉明码中,所需校验位(Parity Bits)数量遵守规则如下:

其中,d表示数据数量,p表示检验位数量。

计算出的校验位附加到数据后,其结果称为汉明码字,码字的总长为c=d+p,码字可以表示为(c, d)。

1.2 Haming-Modified Code

Hamming码通过奇偶校验(Parity)来修正1bit错误或检测2bit错误,但它无法同时进行这两种操作。因此,我们需要额外增加1位奇偶校验位。

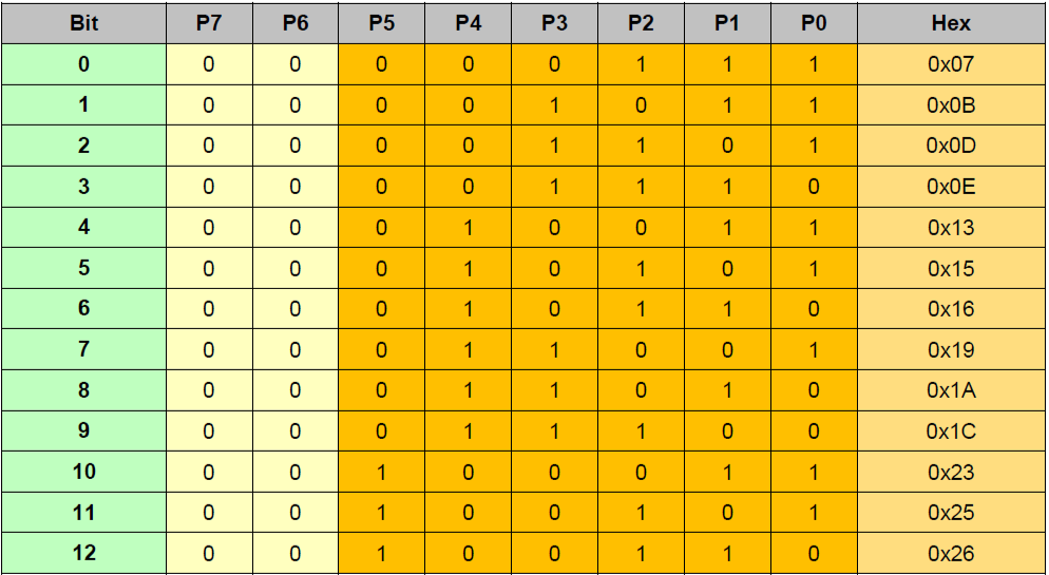

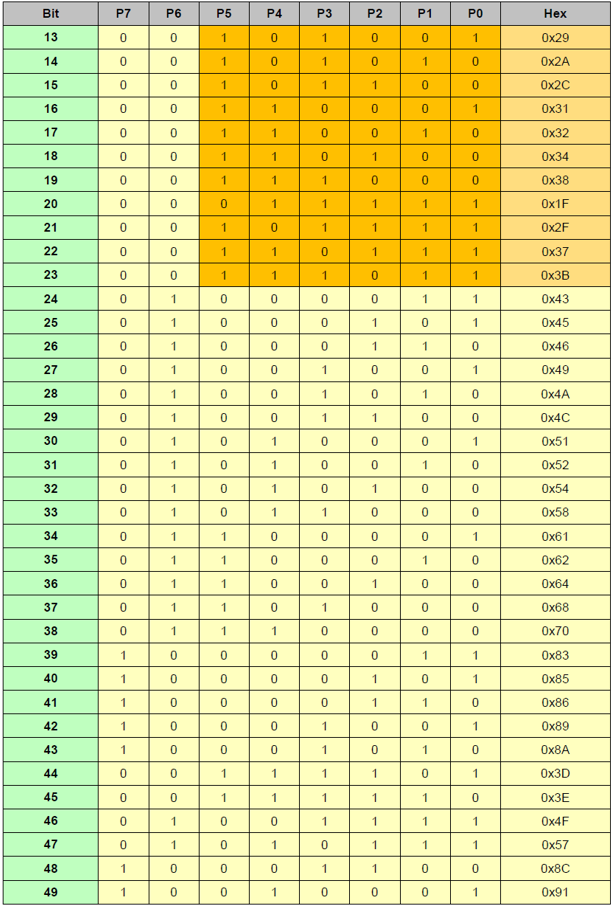

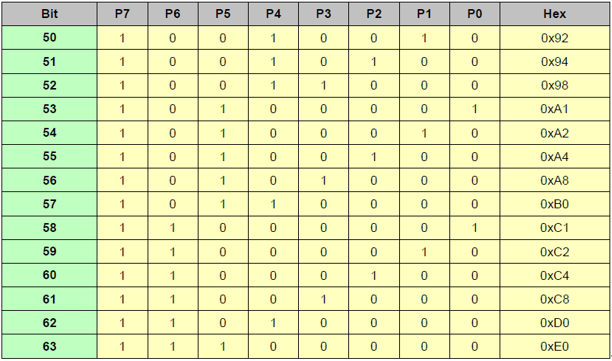

这个编码方案的6bit综合码(syndrome)能够校正64bit序列中的前24bit。

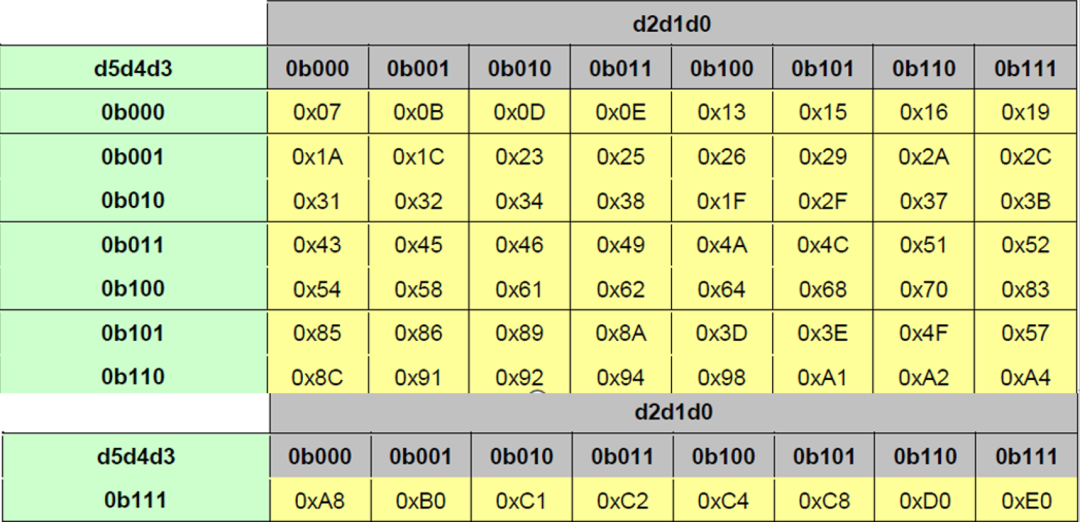

为了更紧凑地编码奇偶校验并高效地解码综合码(syndrome),采用一张特殊的矩阵:

(1)矩阵中的每个单元格代表一个综合码(syndrome);

(2)前24个单元格(橙色行)只使用前3bit或5bit来构造综合码;

(3)综合码采用左对齐的最高有效位(MSB Left-Aligned)。

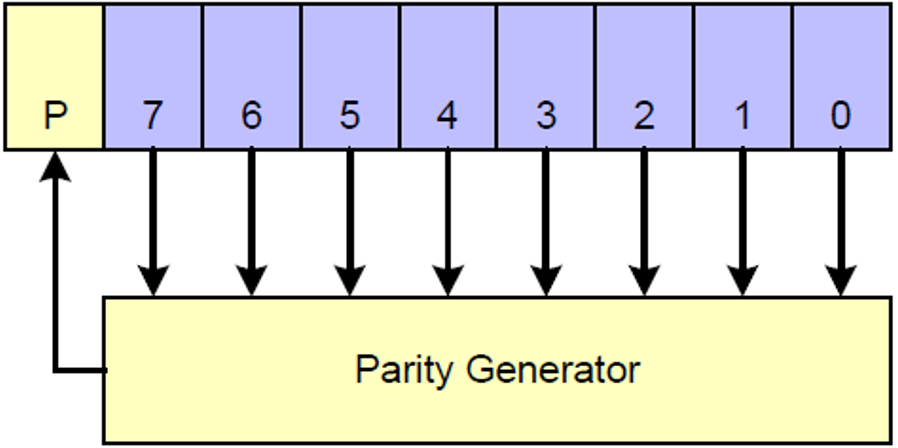

1.3 ECC Generation on TX side

Figure 2. 64-bit ECC Generation on TX Side

Figure 3. 24-bit ECC Generation on TX Side

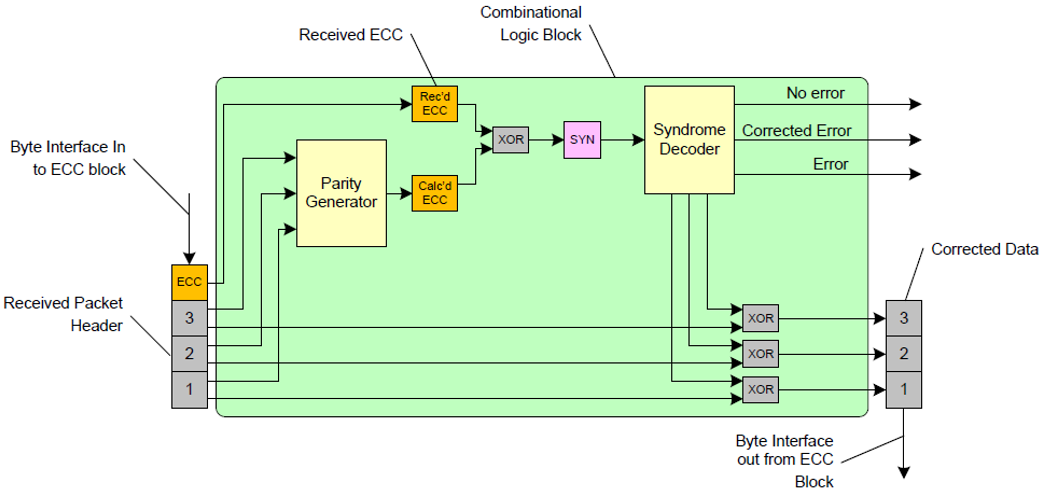

1.4 Applying ECC on RX side

(1) 接收端对接收到的数据包重新计算ECC;

(2) 将新计算出的ECC与接收到ECC进行对比,计算syndrome(综合码);

(3) 解码syndrome判断是否发生了1bit错误;

如果syndrome=0,说明数据包是正确的;

如果不等于0,查看下表进行匹配。

可以匹配,则说明是1bit可以修复的错误;如果

(4) 如果发现单比特错误,则进行纠正。

下表中橙色区域用于24-bit头部的ECC计算。整个表格用于64-bit头部的ECC计算。

下图为24bit实现示意图。

Figure 4. 24-bit ECC on RX Side Including Error Correction

2. checksum generation

ECC是用于对包头进行检测和校正。而CRC是对整个数据包进行传输错误检测。每个数据包会计算一个校验和(checksum)。

MIPI CSI-2中,checksum是16bit CRC,其生成多项式为:

其CRC结果作为数据包的尾部进行传输。如果WC=0,则CRC设为0xFFFF。

计算出的校验值会发送到接收端,用于校验传输是否正确。

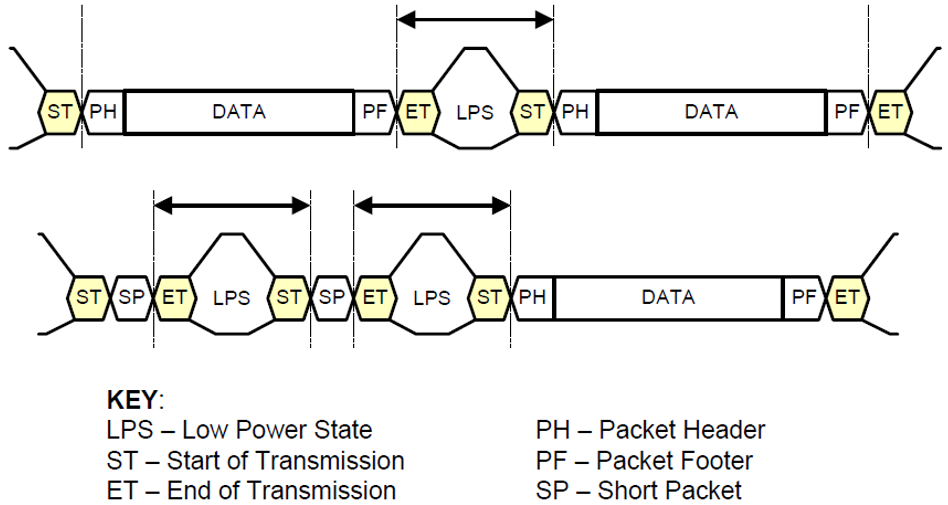

3. packet spacing

MIPI CSI-2中,数据包不是无缝传输的,每个数据包之间会插入一段LPS(低功耗状态),如下图所示。

Figure 5. Packet Spacing

4. synchronization

4.1 帧同步

传输过程中,每个图像帧都以帧起始包(Frame Start, FS)开始,帧结束包(Frame End, FE)结束。FS包包含帧起始码,FE包包含帧结束码。

FS包后紧跟一个或多个长包,传输图像数据。其中,还可以包含多个短包,用于同步信号(Synchronization Codes)。

FS和FE包的短包数据字段将包含16bit帧号(Frame Number)。同一帧的FS和FE包中的帧号必须相同,这样接收端才知道他们属于同一帧。

(1) Frame Number为0,表示帧号功能无效。

(2) 帧号递增。同一个虚拟通道VC下,每个FS包的帧号都会递增1,并周期性复位。例如:1,2,1,2,1,2或者1,2,3,4,1,2,3,4。

同一帧的FS和FE包中的帧号必须相同,这样接收端才知道他们属于同一帧。

使用规则:

(1)必须使用FS开始,FE结束;

(2)FS包与第一条数据包之间的间隔应尽量接近最小数据包间隔;

(3)最后一条数据包与FE包之间的间隔应尽量接近最小数据包间隔。

4.2 行同步

行同步与帧同步不同,帧同步一定需要,而行同步是可选的。而像素级精准则需要使用行同步信号。

与帧同步类似,行开始(Line Start,LS)包和行结束(Line End,LE)包的短包数据字段需要包含16bit行号(Line Number)。

同一行的LS和LE中的Line Number相同。

Line Number是逻辑编号,不一定等于实际物理行号。

(1) Line Number为0表示无效;

(2) 逐行递增:在相同虚拟通道VC和数据类型DT,每个LS包中的行号递增1。在新的一帧复位为1。

注意:根据MIPI01规范定义,接收端应该能处理接近0的行效应周期。

推荐学习资料:《Specification for Camera Serial Interface 2 (CSI-2)》(关注公众号”芯筹帷幄“私信 “CSI2” 可获取 PDF 版)

欢迎关注,获取更多技术资料与分享!

这里将分享芯片设计的相关知识、技术前沿以及行业动态,期待与您交流和探讨,共同进步!

1125

1125

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?