一、实验目的

(1)学习 Quatus 集成开发平台的使用;

(2)熟悉在 Quatus 集成开发平台上原理图编辑输入法的使用;

(3)熟悉QUARTUSII实验硬件平台的使用;

(4)掌握利用层次结构描述法设计电路。

二、实验内容

利用Quartus原理图输入方法,掌握 1 位全加器设计的原理图输入设计方法,并进行Quartus软件的仿真与验证。

三、实验原理

1.半加器

1.1半加器原理

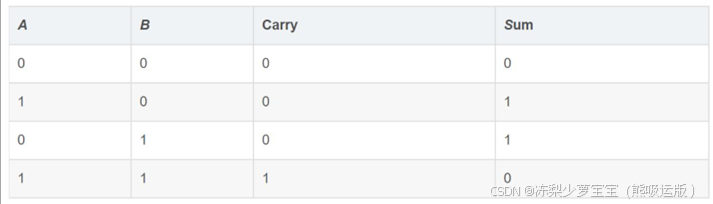

在了解全加器之前,我们先来了解半加器。半加器就是不考虑进位的加法器,只有两个输入和两个输出:输入A和B,输出和数Sum和进位Carry,半加器真值表如下:

1.2 关系表达式

Sum = A ⨁ B ;

Carry = A B .

1.3 电路设计

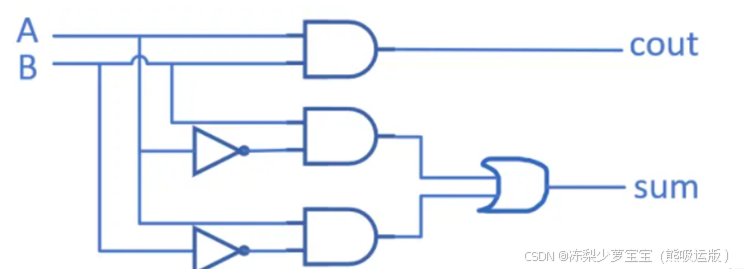

半加器的逻辑电路设计如下:

2. 全加器

2.1 定义

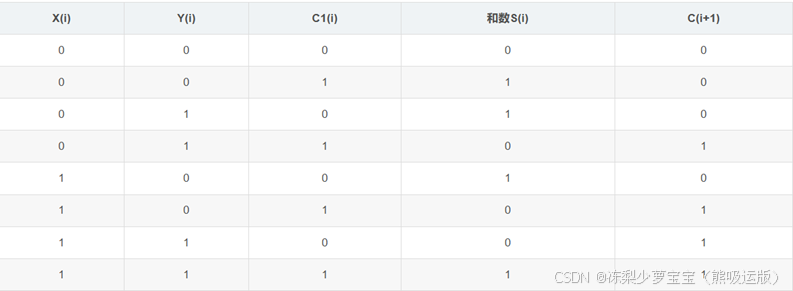

全加器就是在半加器的基础上引入一个进位输入,总共三个输入两个输出。全加器真值表如下:

2.2 关系表达式

这里的输出一共有两个,一个sum,一个进位cout。sum的值是A+B+cin然后去掉进位得到的,也就是说A、B、cin 中,如果输入1的个数是奇数,则sum为1,输入1的个数为偶数(含零)则sum为0。根据这个奇偶判定,可以想到用异或操作,所以得到表达式:

S = A ⨁ B ;

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1775

1775

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?