以D锁存器工程为例

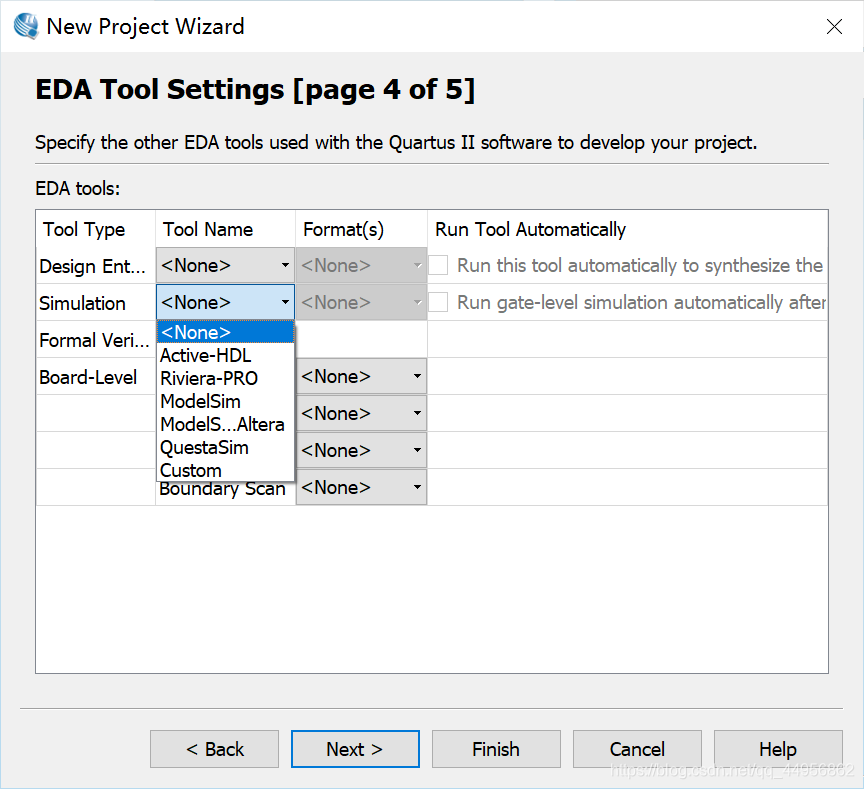

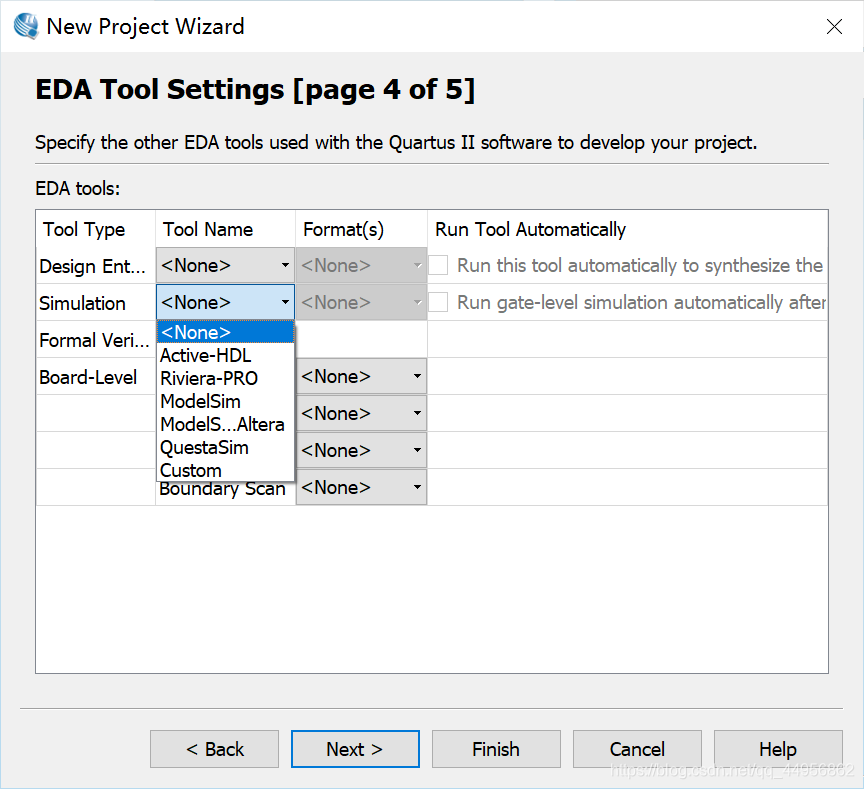

1.新建一个工程(注意:新建工程时不需要联合modelsim仿真,选择none!)

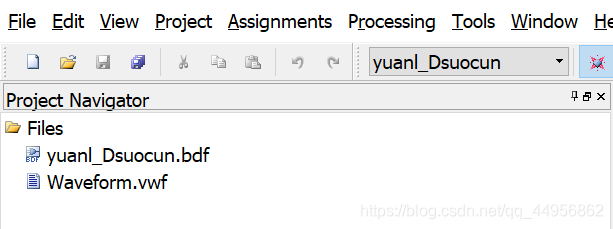

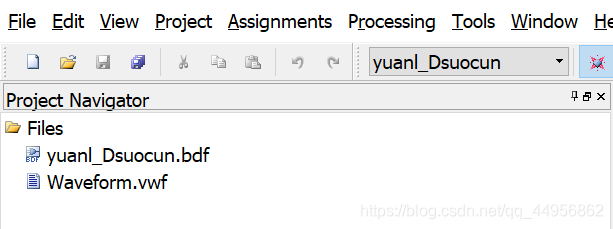

2.工程里新建原理图文件.bpf 和波形文件 .vmf

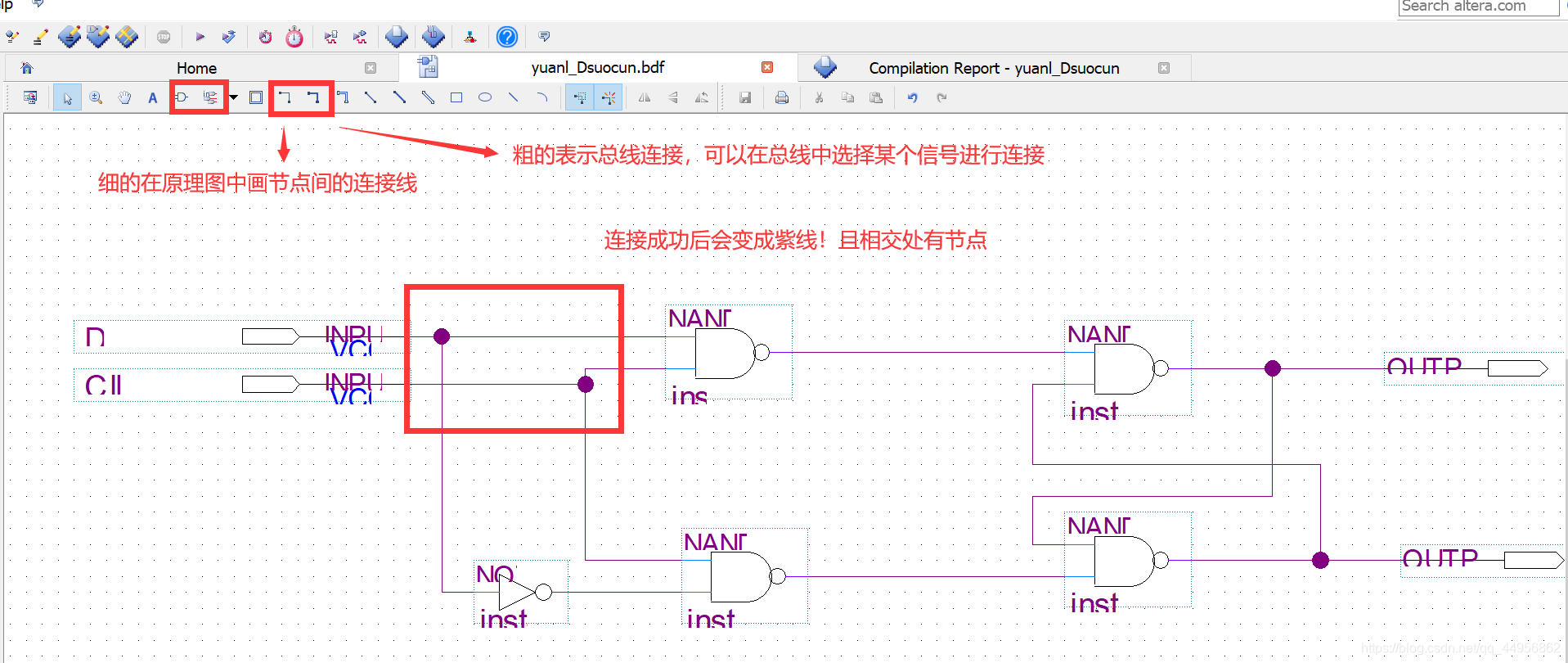

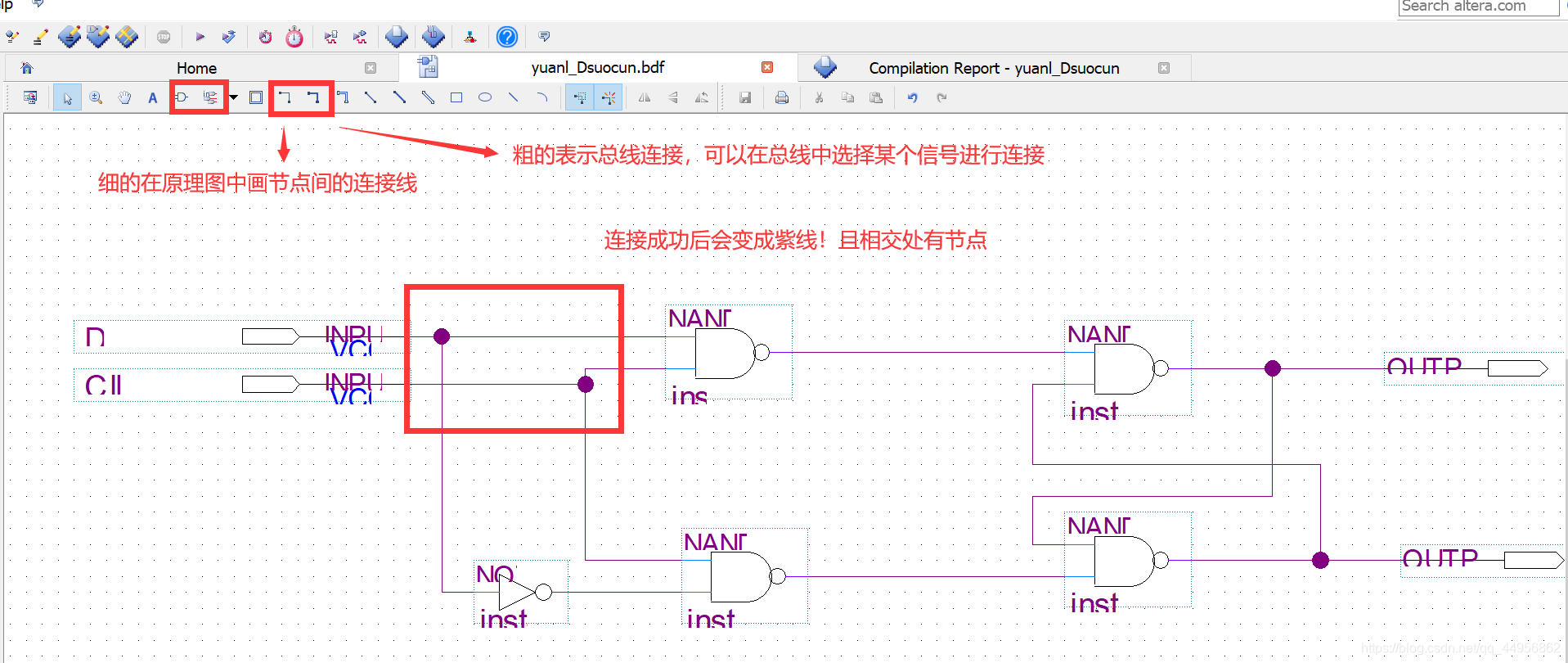

3.画好原理图,编译

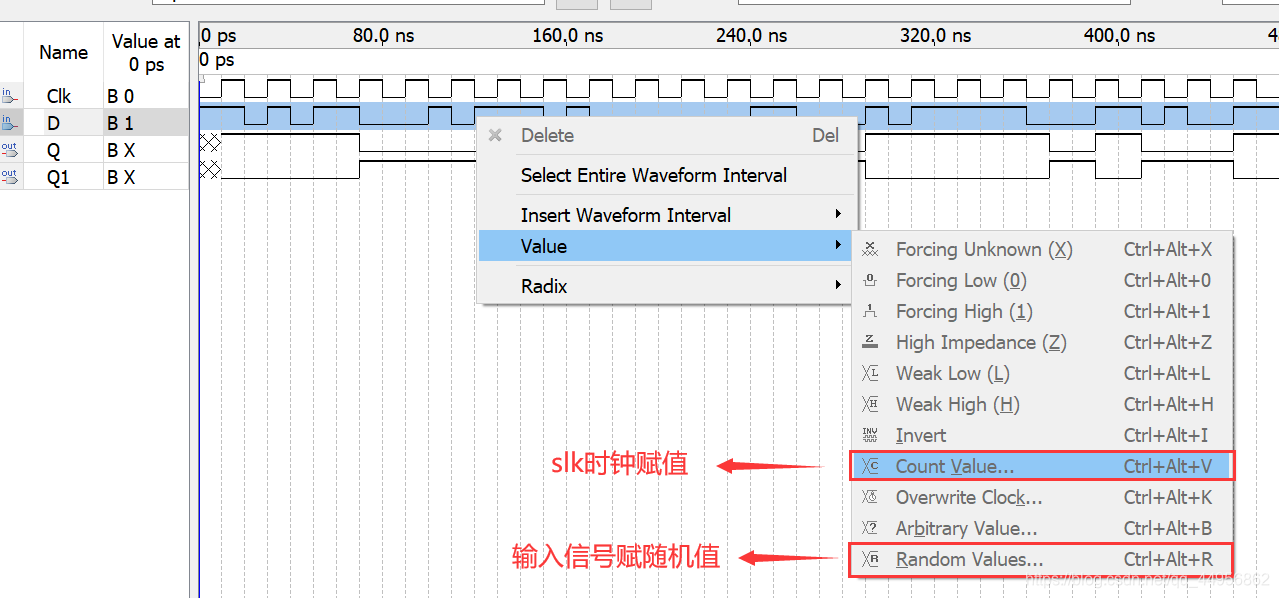

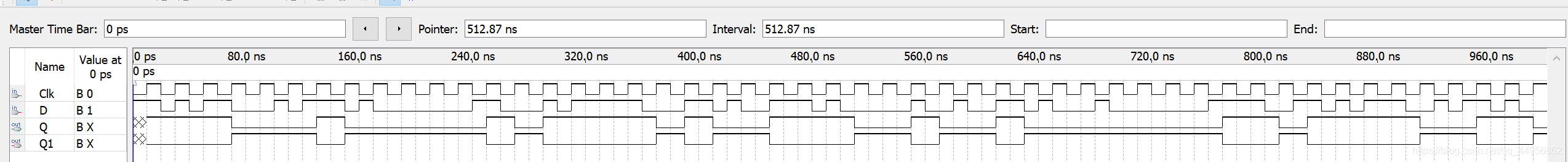

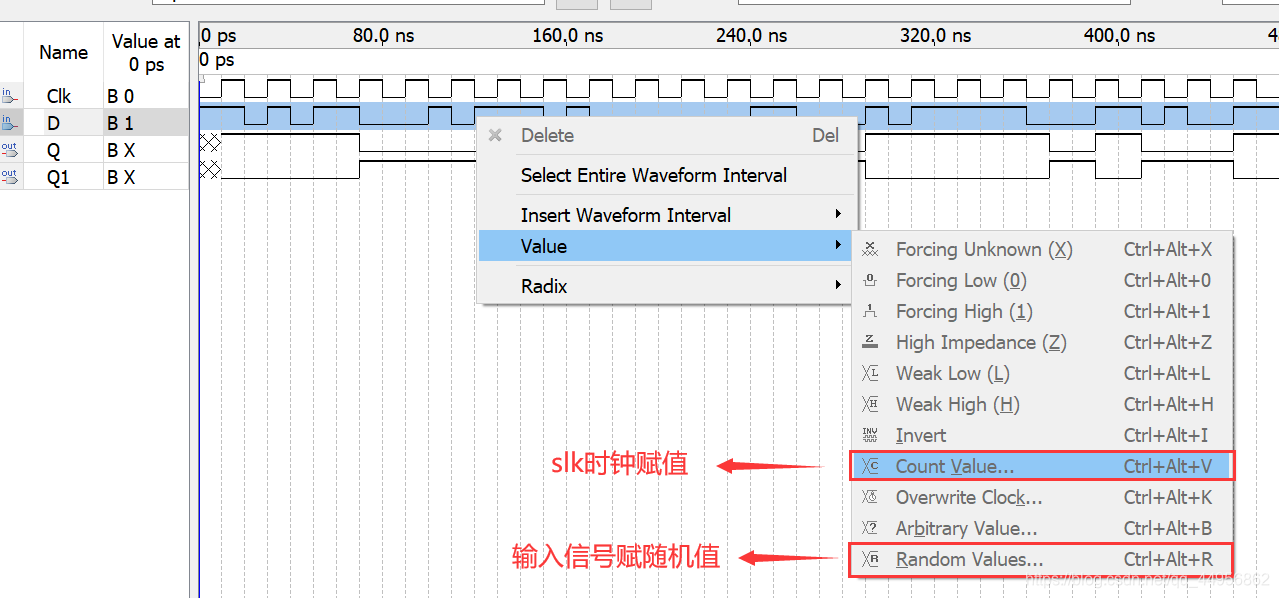

4.在波形文件中 add noders ,给输入信号赋值(slk等信号),编译出结果

基本参考: quartus II 输入原理图及仿真步骤

补充说明:

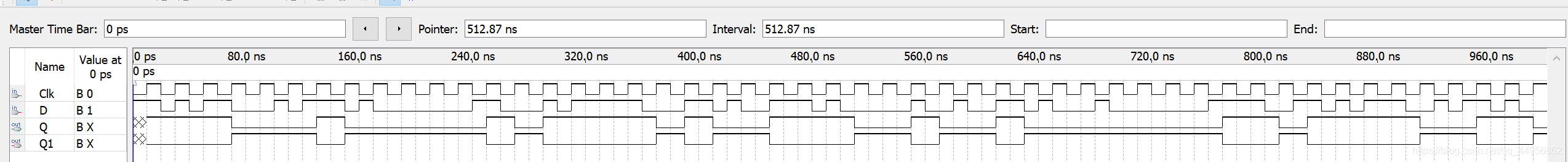

自带仿真结果

以D锁存器工程为例

1.新建一个工程(注意:新建工程时不需要联合modelsim仿真,选择none!)

2.工程里新建原理图文件.bpf 和波形文件 .vmf

3.画好原理图,编译

4.在波形文件中 add noders ,给输入信号赋值(slk等信号),编译出结果

基本参考: quartus II 输入原理图及仿真步骤

补充说明:

自带仿真结果

6505

6505

4323

4323

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?