一、NOC技术简介

片上网络(Network-On-Chip,NOC)是一种用于大规模集成电路的通信架构,其通过将计算机网络的分组交换、路由等技术移植到芯片内部,实现核心、存储单元或其他IP模块之间的高效通信。因此,NOC技术的本质是采用分布式网络互联替代总线互联或交叉开关互联,解决总线互联和交叉开关在扩展性、并行性和能耗上的瓶颈问题,更好适应芯片对于高吞吐量、低迟延、以及灵活通信的需求。

NOC技术的核心功能特征,主要有以下几点:

-

灵活的拓扑结构:支持多种拓扑结构,如网格(Mesh)、环形(Torus)、树形(Tree)、蝶形(Butterfly)等。针对特定芯片的功耗、面积和性能目标,可灵活调整节点间的连接方式。

-

高带宽和低延迟:通过并行通信路径和优化的路由算法,提供高带宽和低延迟的通信。

-

全局异步局部同步(GALS):允许不同模块在各自的时钟域内运行,可降低功耗,提高系统的灵活性和可靠性。

-

低功耗设计:通过局部化通信和动态电源管理(如DVFS)减少全局信号传输能耗。

-

可扩展性和模块化设计:支持核数从几十到上千的扩展,无需重构整体设计。同时,核间通信通过统一协议(如AXI)实现模块化集成,简化IP核复用

-

支持异构计算:可连接CPU、GPU、AI加速器、IO单元等异构模块,并通过协议转换层适配不同IP核的通信标准(如AMBA、TileLink),实现跨架构协同。

-

高可靠性:集成错误检测(如CRC)、容错路由(如多路径冗余)和QoS(服务质量)机制,等等。

二、互联技术演进历程

当前主流的用于多核处理器间的互连技术有片上总线(BUS)互连、交叉开关(Crossbar Switch)互连、以及片上网络(NOC)互连。随着单核到多核到众核的性能需求推动着互连技术从片上总线到交叉开关到片上网络的演进过程。

(1)片上总线互连

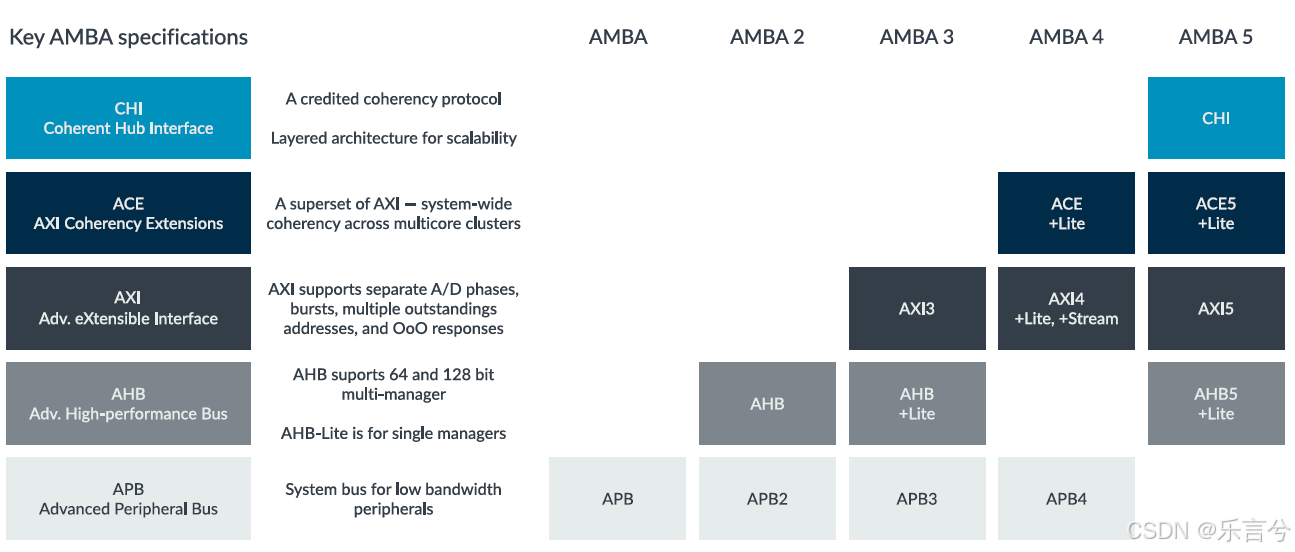

早期以CPU为主导的单核SOC系统采用片上总线互联技术,其片上模块数量较少,片上总线互联架构足以满足性能需求。但是,随着系统性能需求越来越高,多核处理器逐渐普及,早期的片上总线也在不断演进与发展。其中,ARM的AMBA总线是最典型的片上总线互联,因其高性能和协议的开放性,成为广泛应用的标准总线协议。AMBA总线从最初的单一总线发展为多层级、多协议体系,如图1所示为AMBA总线主要协议的演进历程,根据应用需求,主要分为先进外围总线APB(Advanced Peripheral Bus)、先进高性能总线AHB(Advanced High-performance Bus)、先进可扩展接口AXI(Advanced eXtensible Interface)、AXI一致性扩展ACE(AXI Coherency Extensions)和一致性集线器接口CHI(Coherent Hub Interface)。

图1 Key AMBA Specifications

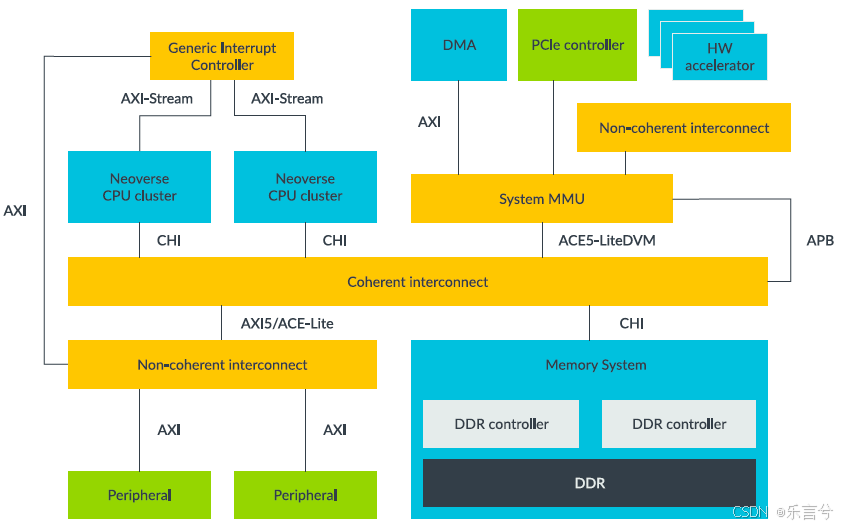

在SOC系统设计中,AMBA总线互联的典型应用如图2所示。SOC系统含有CPU、HW accelerator、Memory、DMA等多个功能模块,这些功能模块采用AMBA总线协议,如APB、AXI、CHI等协议,实现通信与互联。

图2 AMBA总线在SOC设计中的示例

总线互联结构较为简单,但是存在带宽瓶颈,且可扩展性差,当核心数量逐渐增加到几十时,通信效率出现急剧下降。因此,总线互联适用于较少核心数的系统。

(2)交叉开关互连

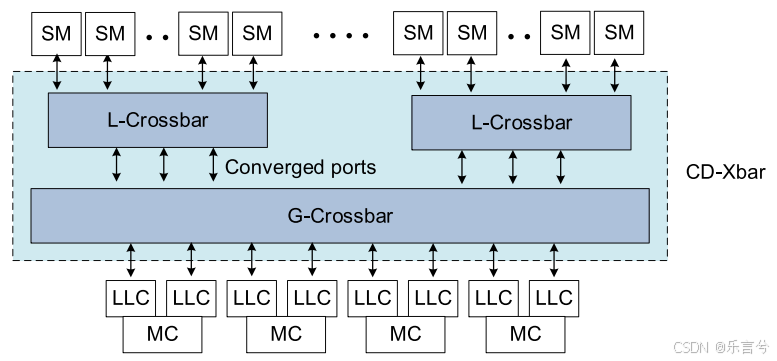

早期的总线互联属于共享总线模式,多设备间存在竞争,需仲裁访问权限,因此,早期总线互联存在带宽利用率较低,扩展性差的问题。随着早期电话交换系统需实现任意线路间的直接连接的应用需求,以及多核处理器系统中高带宽、低延迟的应用需求的背景下,交叉开关技术出现了。交叉开关(Crossbar Switch)是一种全连接的互联架构,允许多个输入端口与输出端口之间同时建立独立的通信路径。交叉开关技术的优势在于其全连接架构的并行传输,具有高带宽和低延迟特点。每个输入端口与输出端口独立连接,支持多设备间同时通信,实现带宽的N倍数提升(N为交叉开关端口数)。同时,全连接架构中数据直接从输入到输出端口,无仲裁和路由计算的开销,且固定路径的延迟极低,因而实现低延迟通信。如图3所示为交叉开关互连的典型应用案例。CD-Xbar是一种收敛-发散交叉开关(Converge-Diverge Crossbar)网络架构(用于GPU NOC网络架构),旨在解决随着流处理器(SM)数量增加时的性能瓶颈问题。CD-Xbar架构特点如下:(1)局部交叉开关(Local Crossbar):将多个SM连接到一组收敛端口,而不是直接连接到最后一级缓存(LLC)切片。(2)全局交叉开关(Global Crossbar):将收敛端口连接到LLC切片。(3)收敛-发散机制:通过局部交叉开关将SM的请求汇聚到收敛端口,再通过全局交叉开关将请求分配到LLC切片。

图3 CD-Xbar架构图

但是,在实际应用过程中,交叉开关互联存在较大的挑战,比如硬件物理设计复杂度、功耗高、信号完整性等问题。交叉开关中的交叉点数量对端口数平方增长(O(N2)),比如16x16的交叉开关需256个交叉点,随着端口数逐渐增多,交叉开关占用的芯片面积比越来越大。大量的交叉点处驱动电路的功耗也越来越高,以及长走线的信号完整性也会受影响。因此,交叉开关互联适用于中等规模的多核系统。

(3)NOC互连

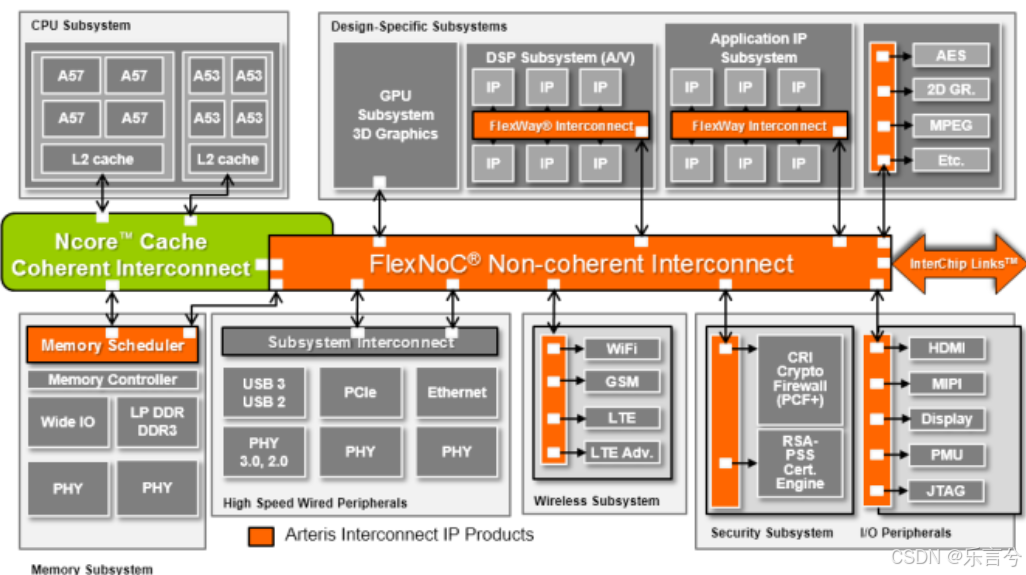

随着半导体工艺进入纳米时代,单芯片集成数十亿晶体管成为可能,多核/众核处理器、异构计算单元(CPU/GPU/NPU)及复杂SOC的兴起,以及性能、成本等需求越来越高,前述的片上总线互联和交叉开关互联均面临严峻挑战。NOC(Network-On-Chip)技术逐渐得到发展,NOC技术采用分布式计算系统的通信方式,将计算机网络的分组交换、路由等技术移植到芯片内部,来解决片上总线和交叉开关互联技术的局限性,比如片上总线的扩展性瓶颈、交叉开关的硬件复杂度限制。具体为NOC技术采用分布式拓扑结构(比如MESH拓扑、Torus拓扑)来增强扩展性和优化长距离通信,支持大规模核心系统,带宽也随核数线性增长,以解决片上总线扩展性瓶颈;NOC技术采用虚拟通道(Virtual Channels)即单条物理通道链路支持多个虚拟通道,降低硬件复杂度为(O(N))等。如图4所示为NOC互连的典型应用案列。

图4 Arteris互连架构

综上所述,上述三种互连技术各有优劣势,结合AMBA总线的易用性、交叉开关的低延迟和NOC的高扩展性,三者之间存在互补与融合发展趋势。比如AMBA+NOC的结合使用,可充分利用AXI总线连接局部模块和NOC管理全局通信互连;比如Crosssbar Switch+NOC的混合使用,可充分利用交叉开关的低延迟和NOC的高扩展性。

三、应用场景

片上网络(NoC)技术广泛应用于需要高并发、低延迟通信的复杂芯片场景,包括:高性能计算与AI加速器(如GPU/TPU众核互联)、多核处理器(服务器CPU核间通信)、自动驾驶SoC(传感器融合与实时决策)、5G通信芯片(高吞吐数据处理)、物联网边缘设备(低功耗异构集成)以及数据中心DPU(资源虚拟化与存算优化)。其优势在于通过分布式拓扑、自适应路由和QoS保障,满足大规模核间通信、动态负载均衡和异构计算需求,同时兼顾能效与可靠性,成为现代AI、HPC及智能终端芯片的核心基础设施。

后续文章会持续分享关于片上网络NOC技术的相关知识,文章内容仅个人学习过程的总结,欢迎交流探讨~

1440

1440

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?