锁相环英文

Phase locked loop,所以很多资料上就简称PLL

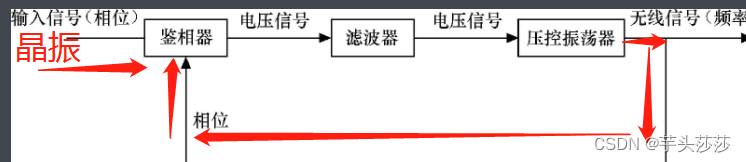

现在很多芯片工作频率很多,频率多高取决晶振频率大小,比如我们电脑芯片1.5GHZ比如我们常用的单片机MCU又72MHZ,但是晶振不可能高达1.5GH的等,正常晶振是到达100-200MHZ,所以我们就需要用到锁相环这个大哥,有了它我们才能进行超级加倍!

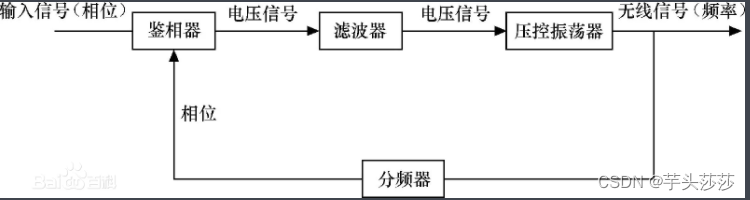

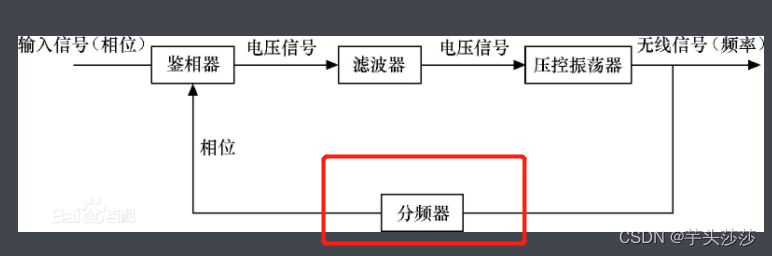

下面先看锁相环的框图

这是完整的框图,下面我们进行分析,我们先不看底下的分频器

输入信号:就是我们晶振的输入

鉴相器:就是对输入信号和压控振荡器的输出信号进行对比

滤波器:就是低通滤波器

压控振荡器:顾名思义随着电压升高我们频率随之增大

那我们就会奇怪,我们直接用压控振荡器不就可以,调节电压控制频率就完事了,但是你要想只要电压有一点飘动,那频率就会随之变化,而我们芯片工作频率要稳定,所以显然只有压控振荡器是不够的。

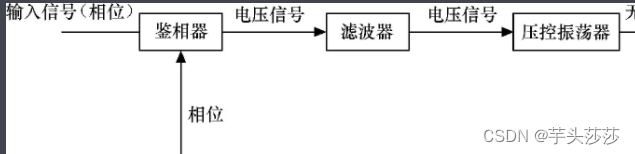

要保证频率一致,是不是就要要看我们输入和输出是不是一致,所以鉴相器就是对着输入和输出的反馈信号进行比较,如图

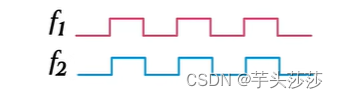

比较两边的频率和相位是否一致,如不一致 鉴相器做成调整经过N个调整,使得输入和输出频率相位相等

那么低通滤波器就是对输入进行滤波,减小高频干扰影响

到这里都理解工作原理,那么8MHZ是要变成72MHZ,我们怎么8MHZ比72MHZ,这时候就需要一个分频器,将72MHZ分频成8MHZ给鉴相器比较久OK

560

560

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?