PCI Express,是计算机总线PCI的一种,它沿用现有的PCI编程概念及通信标准,但建基于更快的串行通信系统;PCIE总线使用的是高速差分总线,并采用端到端的连接方式, 现在的高速总线基本上都是串行总线,这样可以使用更高的时钟频率。

PCIe采用的是树形拓扑结构, 它的体系架构一般由root complex,switch,endpoint等类型的PCIe设备组成

root complex: 根桥设备,是PCIe最重要的一个组成部件; root complex主要负责PCIe报文的解析和生成。RC接受来自CPU的IO指令,生成对应的PCIe报文,或者接受来自设备的PCIe TLP报文,解析数据传输给CPU或者内存。

switch: PCIe的转接器设备,目的是扩展PCIe总线。和PCI并行总线不同,PCIe的总线采用了高速差分总线,并采用端到端的连接方式, 因此在每一条PCIe链路中两端只能各连接一个设备, 如果需要挂载更多的PCIe设备,那就需要用到switch转接器。switch在linux下不可见,软件层面可以看到的是switch的上行口(upstream port, 靠近RC的那一侧)和下行口(downstream port)。

一般而言,一个switch 只有一个upstream port, 可以有多个downstream port.

lspci -tv命令可以显示pcie的总线拓扑,如上图所示, 一个PCIe设备的ID由以下几个部分组成:

以0000:00:00.0为例,分别对应PCI域,总线号,设备号,功能号

配置空间

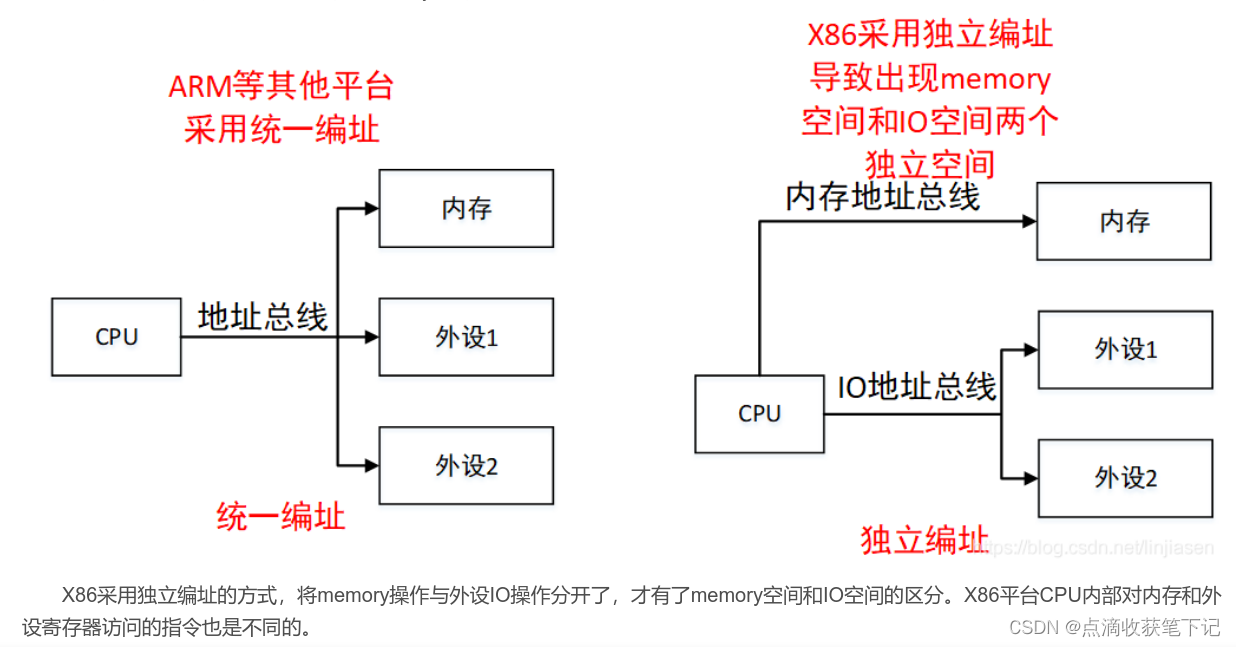

PCI有三个相互独立的物理地址空间:memory地址空间、I/O地址空间和配置空间。这三个地址空间都是采用唯一的地址进行寻址,比如我们使用地址0x100时需要指定这个地址在哪个地址空间,配置空间,I/O地址空间和memory地址空间的0x100偏移,对应的是不同的存储位置。

PCIe架构下定义了4种地址空间:Memory空间、IO空间、配置空间和message空间。message空间其实就是用来report带内的message和event的(比如error message、电源管理消息等),其实就是通过带内message transaction的方式来代替带外信号,用message的好处就是可以省去许多带外信号。

PCIe spec规定了所有PCIe设备(除了host bus bridge外)必须实现配置空间,说白了就是PCI-SIG规定了一种独立于memory空间的PCIe设备访问(读写、配置)机制(说白了就是一堆按规则排列的reg)。PCI-SIG详细规定了PCIe设备reg的排列(每个capability id reg的后面4Byte会保存next capability的起始地址,这样方便芯片厂商扩展reg,并且PCIe驱动软件天然可以使用list来管理这些reg

————————————————

版权声明:本文为CSDN博主「linjiasen」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/linjiasen/article/details/87944672

我们可以读取配置空间获得设备的信息,也可以通过配置空间来配置设备,通过pci设备的id和配置空间的偏移地址, 软件可以来访问具体的寄存器。

PCIe设备的每一个功能(function)都对应一个独立的配置空间, pcie的配置空间布局如下:

CPU可以通过访问BAR地址读取PCIe的设备空间,但是我们需要读取到配置空间才能获取BAR,那么怎么访问PCIe的配置空间呢?

ARM使用ECAM的方式访问PCIe配置空间。ECAM是一个将配置空间映射到MEMORY空间的规则。硬件根据ECAM的方式将某个Memory空间映射给PCI配置空间,CPU访问对应的memory空间即可以操作PCIe配置空间。

————————————————

版权声明:本文为CSDN博主「Hober_yao」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/yhb1047818384/article/details/106676528

PCI/PCIE设备配置空间的访问方式----IO访问 & 内存访问

X86系统中,对PCIE设备配置空间的地址映射一般有两种方式:内存映射和IO映射。因此开发者也可以通过内存访问或者IO访问来访问其配置空间

PCIE设备的访问离不开其Bus,Dev,Fun的编号方式,如下图寄存器所示,Bit[23:16]用来存放Bus号,共8Bit,因此解释了上述表述为何一共有256条Bus,Bit[15:11]存放Dev,共5bit可存32个Dev,Bit[10:8]存放Bus,共3Bit可存8个Fun。这也就也是了为何上述PCIE设备数一共是256个Bus,32个Dev和8个Fun。

————————————————

版权声明:本文为CSDN博主「欢乐的鱼」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/Liang0528/article/details/120161547

1736

1736

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?