一、场景介绍

通常使用microblaze软核的场景一般不是soc fpga 芯片,本次使用ZYNQ芯片是想验证一下microblaze地址空间的读写操作,手头上只有一块zynq的板子,于是想在PL端添加microblaze软核测试;

二、实际工程

开发环境:VIVADO 2021.2 、VITIS2021.2;

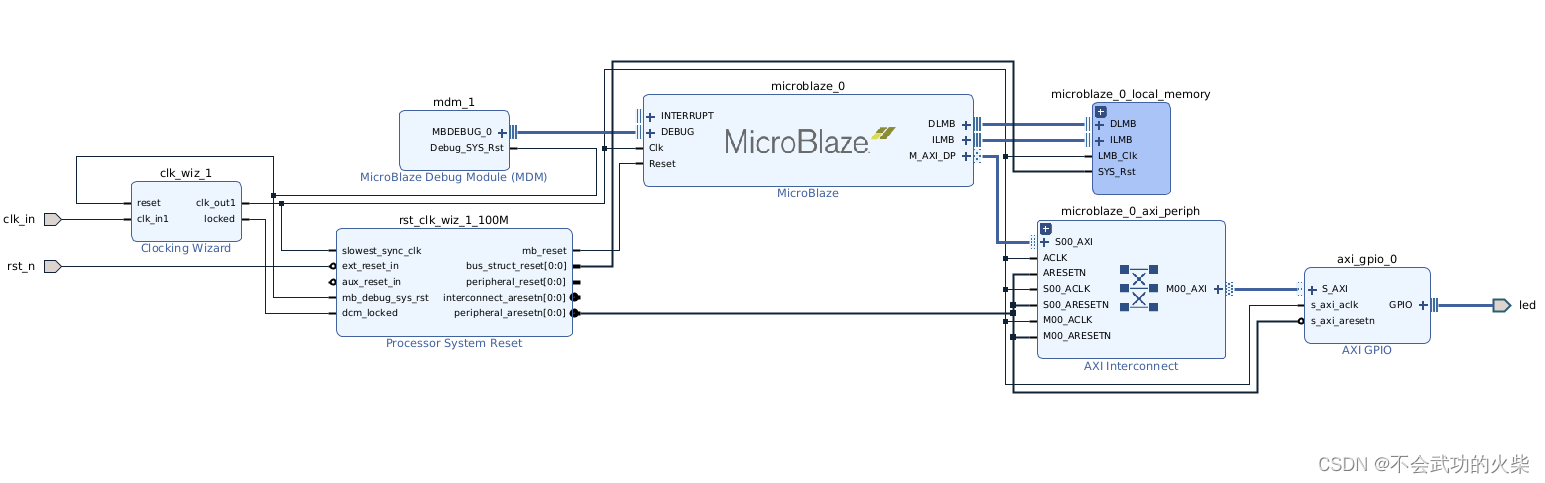

单独添加一个microblaze软核,添加一组AXI GPIO,实际block design 如下图:

启动vitis建立工程之后,编译vitis工程之后(build project)点击run as-> launch hardware会出现以下错误:

三、错误分析

看到网上大致有两种说法:

1、未编译工程;

2、编译出错(比如地址空间分配过小);

仔细检查之后此处的错误不是以上提到的两种情况,多次尝试后也未能解决;最后猜测是否是必须要添加AMR端才可以正常;

四、解决方式

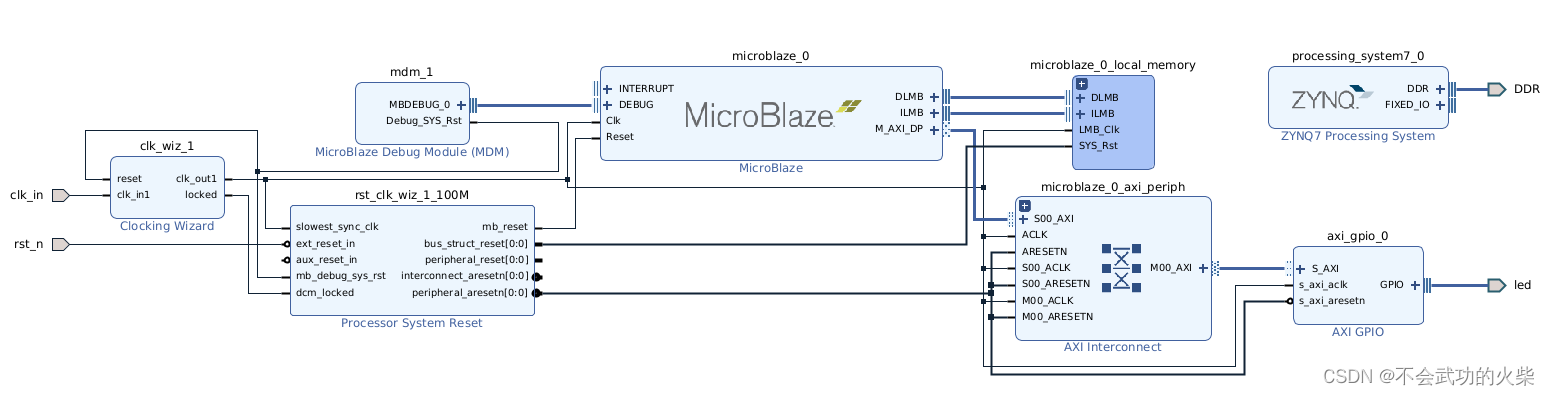

在block design 中添加arm核之后,编译工程后通过,设计加载正确。更改后的设计如下图(实际只是添加了ARM核,并未使用ARM):

此文仅为测试调试过程中的记录,如有类似错误可以参考。如有其他问题可以相互交流学习。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?