目录

1、使用 Quartus Prime 18.1 创建工程、添加相关.v文件并进行编译

5、使用 Power Analyzer Tool 进行功率分析

一、环境

Intel® Quartus® Prime Standard Edition Software 18.1.0.625

ModelSim-Intel® FPGA Edition (includes Starter Edition) 18.1.0.625

二、顶层文件 及 TestBench文件

在顶层文件中创建一个名为NewMainBoardFPGA的顶层模块:

`timescale 1ns / 1ps

module NewMainBoardFPGA (

CLK_in ,

CLK24M_out ,

LED_out ,

ADCCS_out ,

ADCSCLK_out ,

ADCMOSI_out ,

ADCMISO_in ,

VSwitch_out ,

ISwitch_out

);

///

/****************input and output*************/

input CLK_in;

output CLK24M_out;

output LED_out;

output ADCCS_out;

......在TestBench文件中创建一个名为NewMainBoardFPGA_tb的测试模块:

module NewMainBoardFPGA_tb();

/

/*************LOGIC DEFINE**************/

logic clk_24m;

......

/

/*************CODE BEGIN**************/

initial begin

clk_24m = 1'b0;

clk_100m = 1'b0;

nrst = 1'b0;

sysva = 12'd1234;

sysvb = 12'd3456;

sysvc = 12'd1893;

loadva = 12'd246;

loadvb = 12'd1023;

loadvc = 12'd2246;

sysia = 12'd3518;

ntc = 12'd542;

sysib = 12'd1246;

sysic = 12'd3254;

#300 nrst = 1'b1;

end

//模拟外部24Mhz时钟

always #PERIOD24MHZ clk_24m = (~clk_24m);

always #PERIOD100MHZ clk_100m = (~clk_100m);

NewMainBoardFPGA gen_NewMainBoardFPGA( //模块例化

.CLK_in (clk_24m),

.CLK24M_out (clk_arm),

.LED_out (led2),

.ADCCS_out (spi0_cs),

.ADCSCLK_out(spi0_clk),

.ADCMOSI_out(spi0_simo),

.ADCMISO_in (spi0_somi),

.VSwitch_out(vswitch),

.ISwitch_out(iswitch)

);

注意,若使用到外部的器件模拟文件,也需要将器件模拟的源代码移动到TestBench中,否则Modelsim在进行仿真是会报错。(后续待研究)

三、Power Analyzer Tool使用步骤

1、使用 Quartus Prime 18.1 创建工程、添加相关.v文件并进行编译

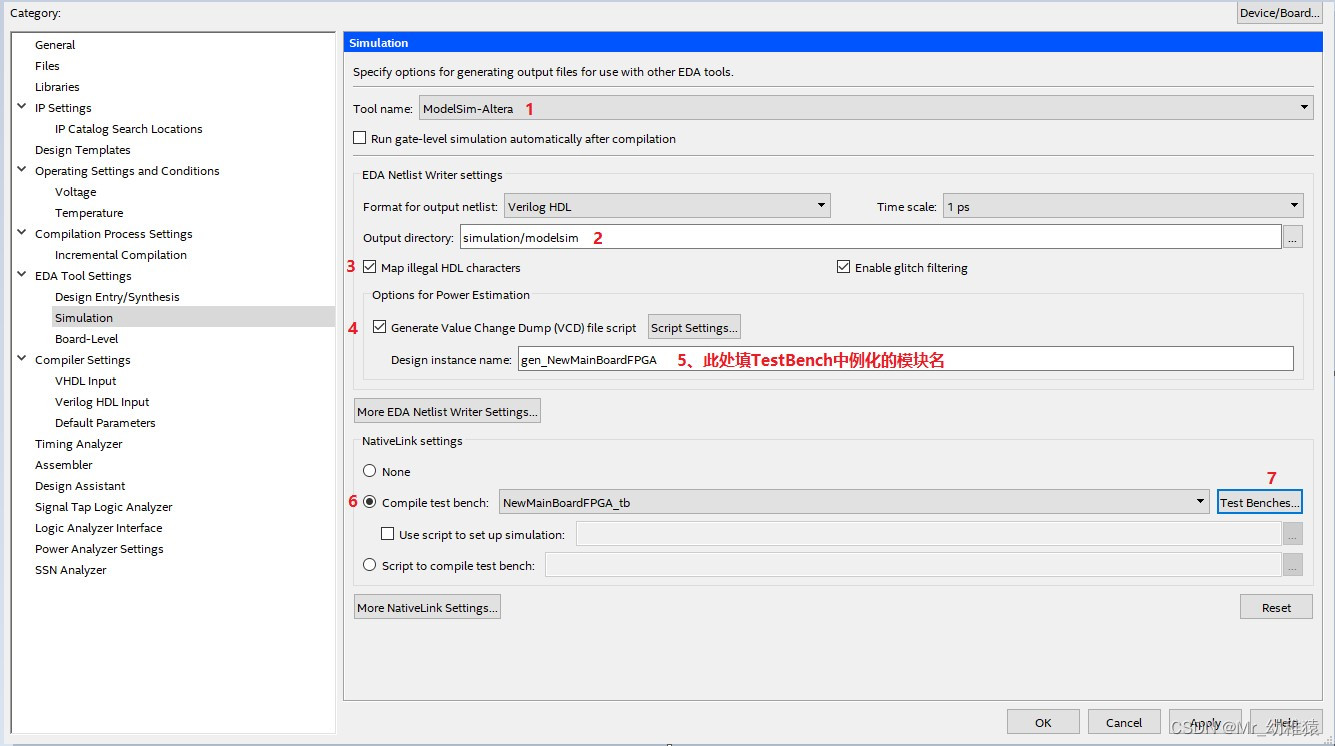

2、 对EDA仿真工具进行设置

Assignments -> Settings: EDA Tool Settings -> Simulation

设置完成后,点击Apply 和 OK。

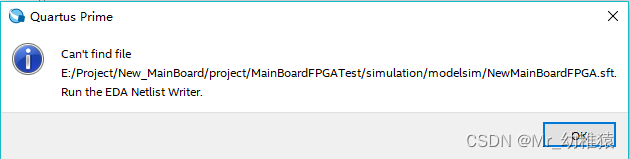

3、重新编译程序

若不重新编译程序,可能会出现如下错误:

4、进行门级仿真

点击Tool -> Run Simulation Tool -> EDA Gate Level Simulation,出现如下结果,点击Run。

接下来Modelsim就会自动打开并开始仿真,仿真结束后,输入quit -sim关闭仿真。至此,就会在工程文件夹下的simulation\modelsim中生成 NewMainBoardFPGA.vcd 文件。

5、使用 Power Analyzer Tool 进行功率分析

点击Processing -> Power Analyzer Tool

input file 选项中 点击Add Power Input File(s),添加仿真结束生成的NewMainBoardFPGA.vcd文件

设置完成后,点击 Start ,开始进行功率分析。

6、分析结果

2974

2974

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?