简介

之前简写了3篇关于微架构的文章,涉及ARM N2,ARM V2以及代表RISC-V阵营的P870,本文分享从网上找到的微架构图,并修正一下之前表述错误或者不合适的地方,也欢迎大家讨论。

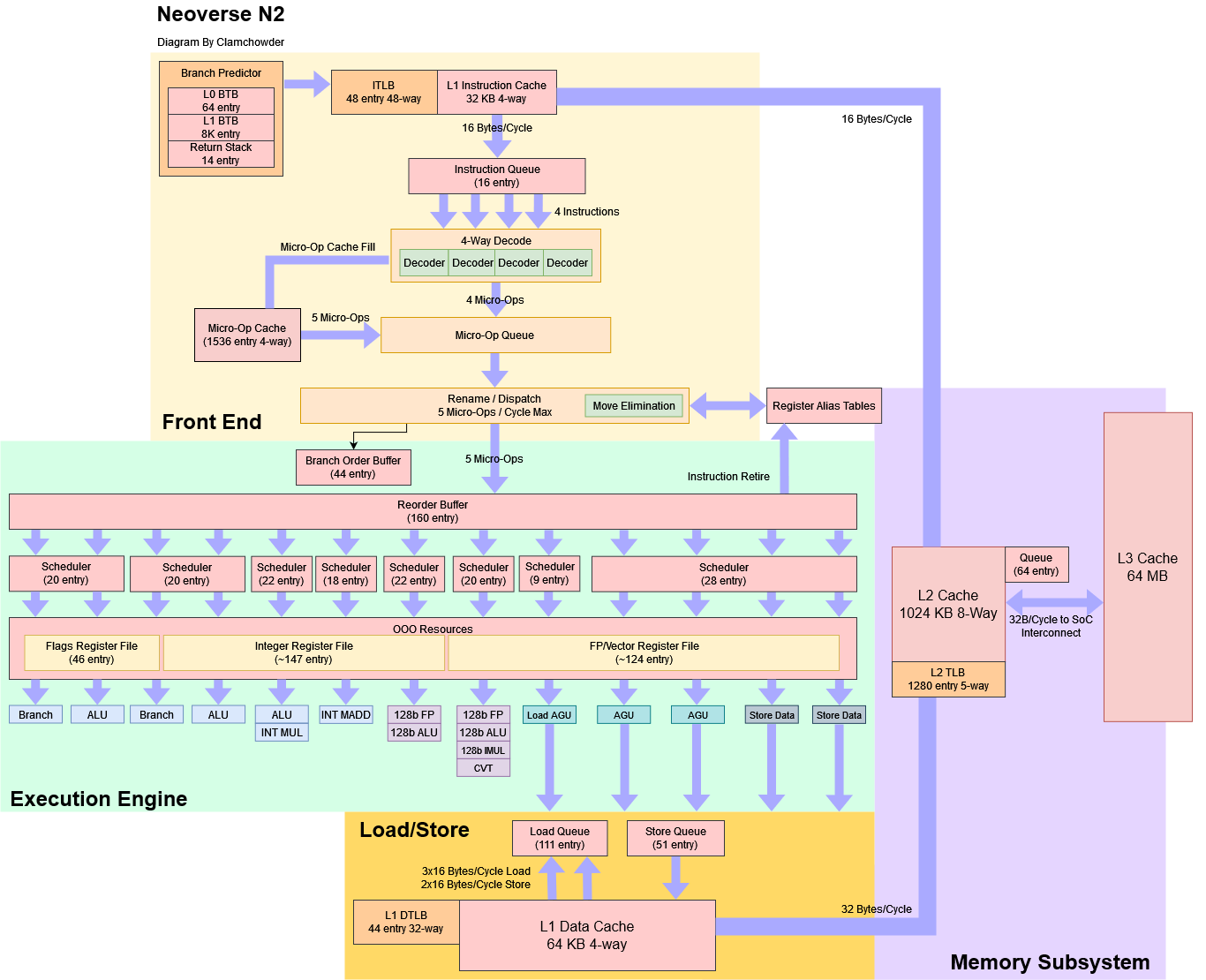

ARM N2

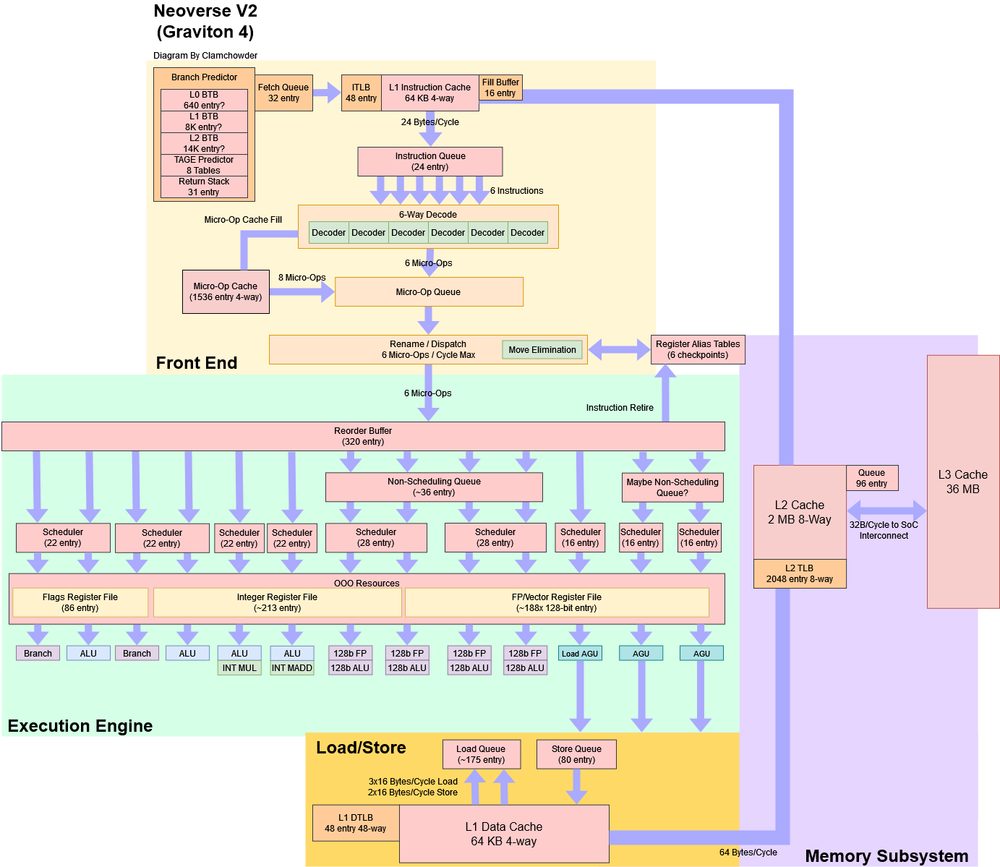

ARM V2

ARM N2和V2的差别大致对应ARM同年的X系列和A系列的差别(超大核和大核),具体的参数微架构图给出了汇总,仅供大家参考。前文介绍“ARM N2处理器微架构介绍”“ARM V2处理器微架构介绍”。

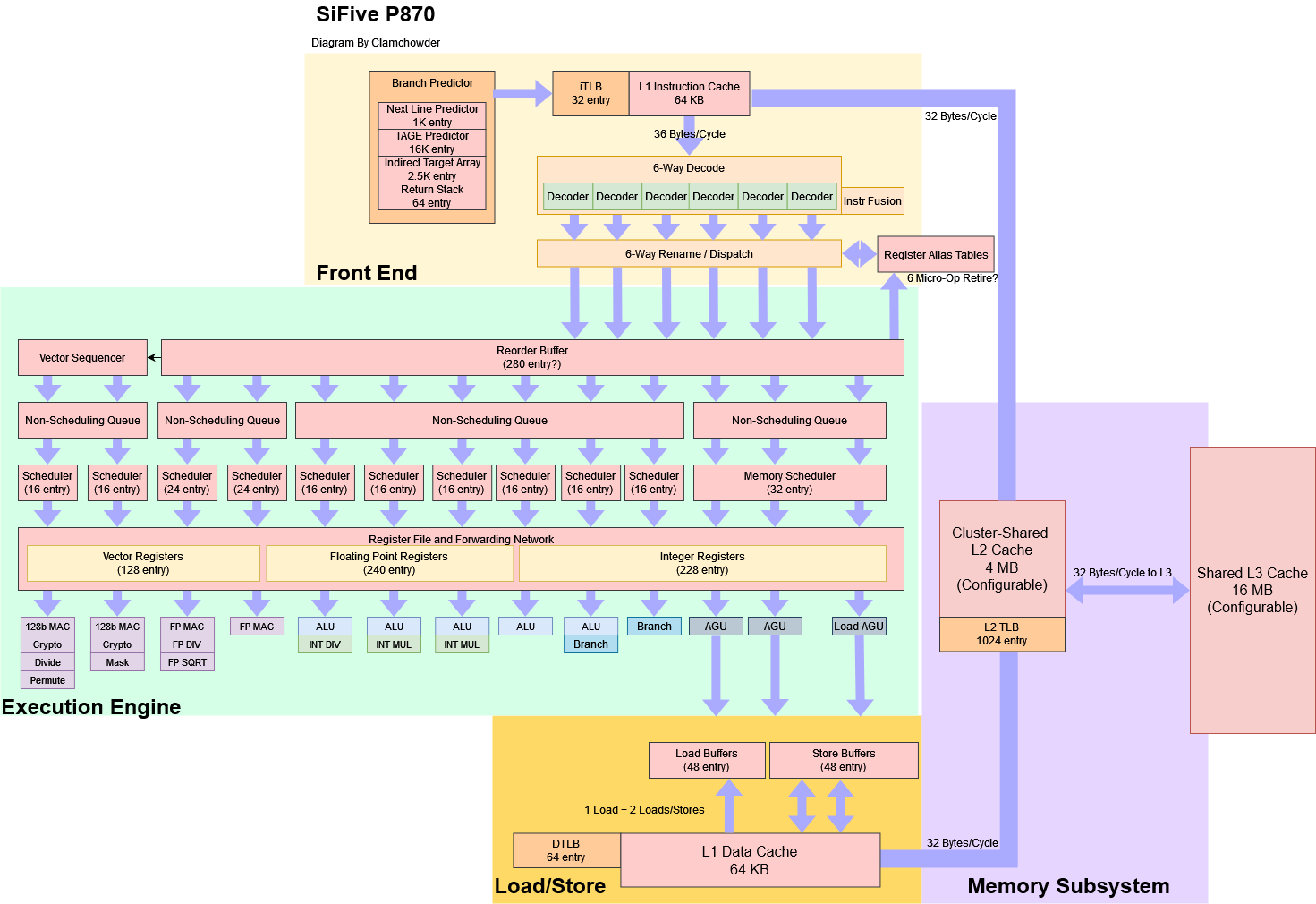

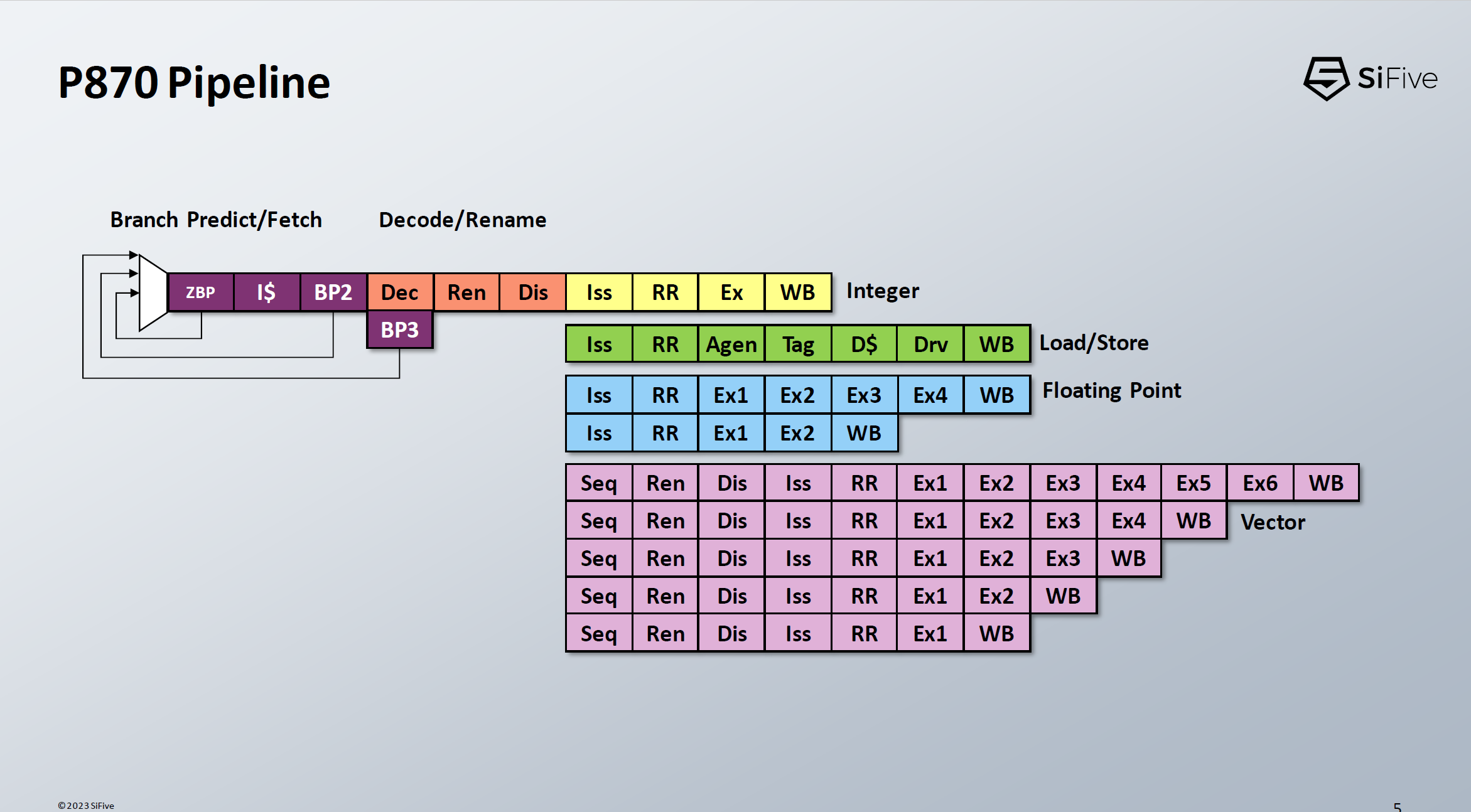

SIFIVE P870

这个系列我在“RISC-V架构CPU的先进微架构设计”一文中有描述,里面也有不少描述不合适的地方,例如,“P870分支预测错误惩罚比ARM的更严重”,我细看了下流水线图,流水线到BX仅仅8cycle?从官方的图上看是这样的,这一点我没那么确定,如果到BX去刷新错误分支,惩罚的cycle数比arm而言小。但这个毕竟只是个流水线图,没有更多信息证明。不过从微架构各项参数来看,P870除了每个cycle预测2分支以及op-cache外,基本和V2对标,公开的CPU频率和面积也都平衡的很好,跑分在18 SpecINT2k6/GHz,处在很高的水准。CPU性能评估不是很好量化,不能说ARM有op-cache就一定性能好(而且现在ARM还放弃了),很多东西都是PPA的权衡,仅考虑公开参数,RISC-V较为先进的微架构设计和ARM的微架构差距应该没有我上次说的2.5年那么大。不过差不管多少年,个人觉得核心差距不在微架构上,在生态上。

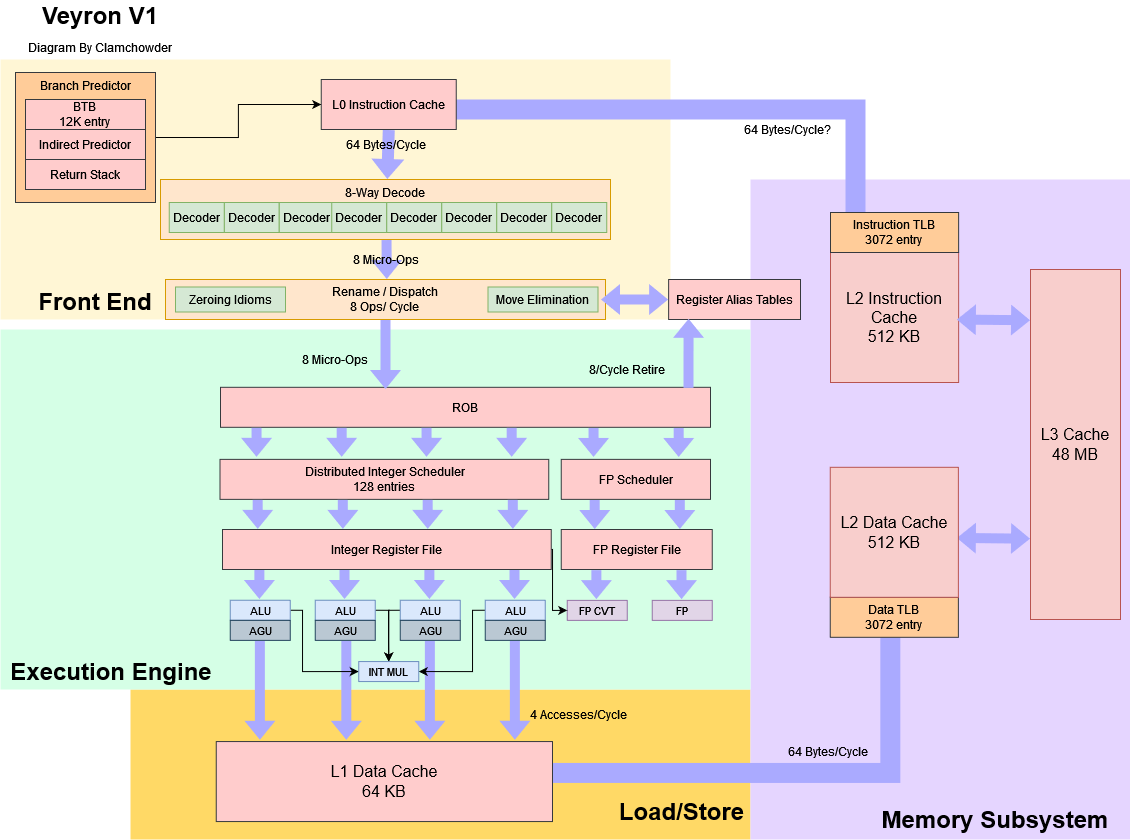

Veyron V1

这个芯片之前也在前文讲过,设计的感觉比较激进。

总结

从当前公开的资料显示,RISC-V阵营的微架构设计水平确实处在一个比较高的水准,和ARM差距不那么大,但就标准生态而言,还是有些差距,比如ARM具备完善的安全生态,软件生态方面,RISC-V还需要在高端领域继续努力。除了类似前几篇很宏观的介绍,后续我还有计划写一些较为详细的CPU微架构文章。关于CPU的问题也欢迎大家和我交流

1216

1216

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?