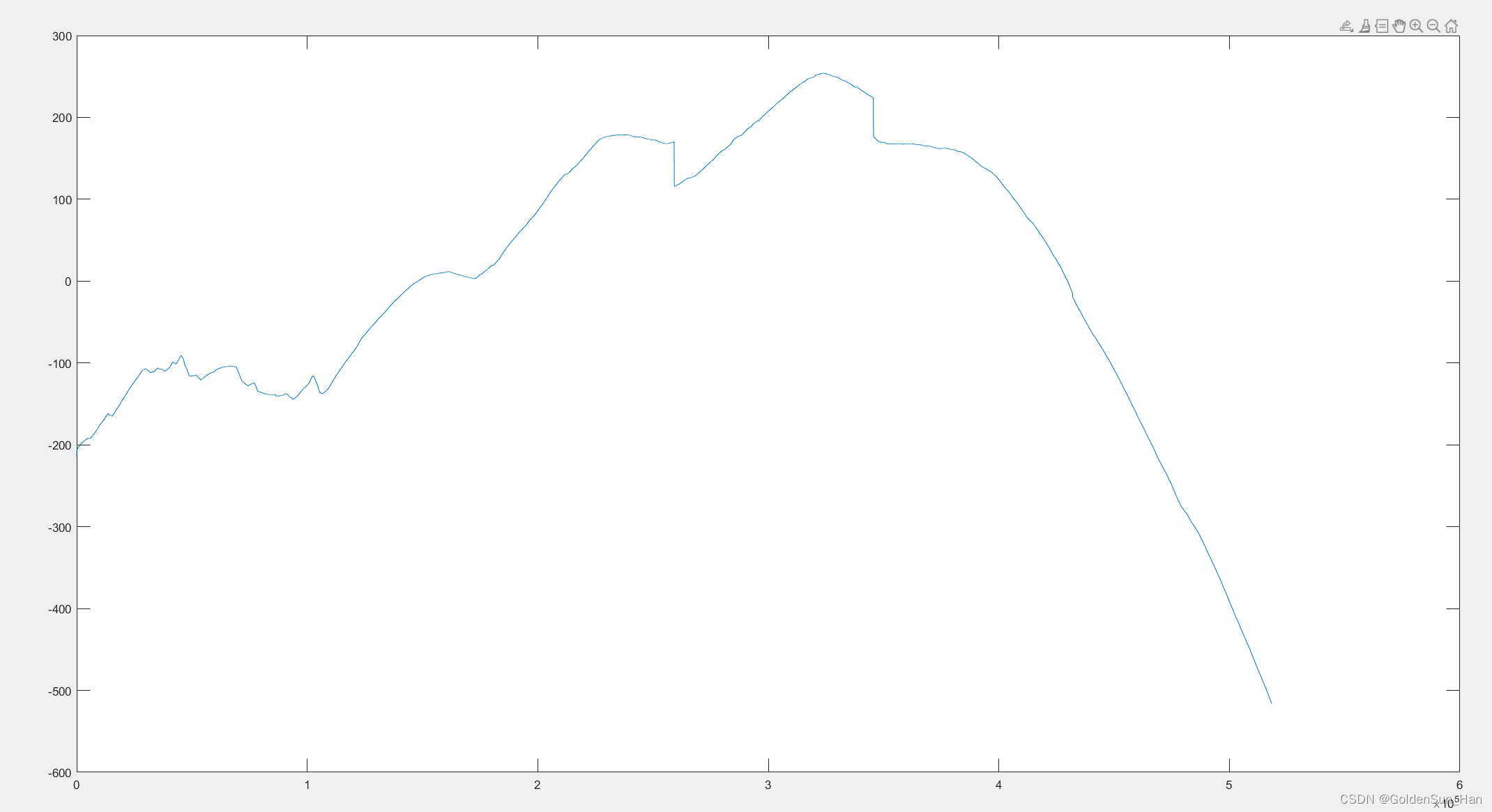

基于武大的最终产品进行时间传递时会存在周跳现象,而用其他机构的产品计算时候就不存在这个问题,不知道为什么。。。。。。

基于武大最终产品时间传递时存在跳变

最新推荐文章于 2024-06-30 17:37:26 发布

文章讨论了在使用武汉大学开发的时间传递产品时遇到的周跳问题,与其他机构的产品相比,该问题并未出现,但具体原因不明。

文章讨论了在使用武汉大学开发的时间传递产品时遇到的周跳问题,与其他机构的产品相比,该问题并未出现,但具体原因不明。

2539

2539

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?