文章来源:Flyback Converter Snubber Design

Snubber Design

前言:所有的PWM变换器都具有引起振铃的非线性寄生参数,必须要进行抑制,否则半导体器件很容易损坏并且还会产生更高的噪声。以Flyback变换器为例进行说明。

01 Flyback Converter without Snubbers

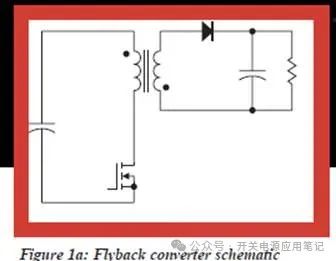

图1a所示为没有缓冲电路的反激变换器。理想情况下,电路在开通和关断时具有方波特性,然而实际情况下功率开关的关断会中断通过变压器漏感的电流,由于线路感抗将导致FET漏极上的电压尖峰。

Figure 1b: Flyback converter drain voltage with no snubber

电感将与电路中的杂散电容产生振铃,产生高幅值高频波形,如图1b所示。在反激原边,测得漏感与寄生电容谐振。

产生的振铃将会产生两个问题:首先,FET的漏极电压过高可能会导致其雪崩击穿;其次,振铃能量将会传导并辐射到整个电源、负载以及电子系统中。振铃频率也会在传导和辐射EMI中显示为EMI频谱的峰值。在大多数设计中,这是不可接受的,所以有必要添加电路元件来抑制振铃(使用RC缓冲器)或箝位电压(使用RCD箝位),亦或两者兼而有之。这些网络的设计是测量和分析的结合,以确保坚固可靠的结果。我们将回顾两种不同类型的缓冲器设计过程。

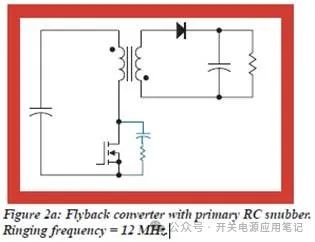

02 Primary RC Snubber

图2a所示为利用RC缓冲电路来抑制FET漏极上的振铃。电阻为LC谐振提供阻尼,而串联电容则防止功率级开关频率的电压施加在电阻。电容的大小是为了使电阻在振铃频率下有效。RC缓冲器最好直接放置在要保护的半导体上。

如果使用与FET串联的电流检测电阻,需确保缓冲器连接到检测电阻的顶部,而不是接地。执行此操作时,当缓冲电容放电时,检测电阻在导通时不会看到电流尖峰。

设计RC缓冲器的要求为:选择一个电阻来适当地阻尼振铃;选择一个电容以尽量降低网络的耗散功率。

Design Step1:Measure Leakage Inductance

设计有效的RC缓冲器的第一步是测量引起振铃的寄生参数:总等效电容或漏感。电容难以定义和测量,它是非线性半导体的结电容、变压器绕组电容和其他杂散电容(如散热器)的组合。振铃频率通常足够高以至于即使是示波器探头在连接到电路时也会影响波形。

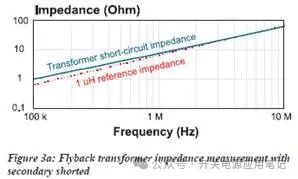

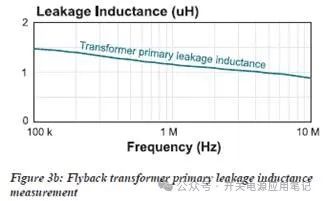

这就剩下变压器的漏感Lk,利用频率响应分析仪很容易测量。将反激变压器副边短路,测量原边绕组阻抗。建议在宽频率范围内测量,包括电源开关频率和缓冲器振铃频率,以便捕获适当的漏感值。

由于变压器绕组的邻近效应,漏感在较高频率下会有很大变化,如图3b所示:漏感随频率增大而降低。

Design Step2:Measure the Snubber Ringing Frequency

FET漏极上的振铃是不对称的,其峰值尖锐而底部较宽。这是由于FET输出电容的非线性特性,其随着电压的增大而减少。根据振铃估算振铃频率fr。为了设计较好的缓冲器,振铃频率最好比开关频率高两个数量级,否则耗散功率将会很大。必须尽量降低变压器的漏感,或电路电容,又或者两者都减少。

Design Step3:Calculate the Sbubber Resistor and Capacitor

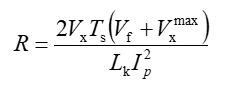

为了抑制振铃,需要计算谐振电路的特征阻抗,如式(1):

![]()

如果我们使用等于振铃特性阻抗的缓冲电阻,振铃将会被很好地抑制。因此,我们使用R=Z的设计点来选择电阻。

缓冲电容用于最小化在开关频率点的损耗,同时允许电阻在振铃频率有效。最好的设计点是电容在振铃频率上的阻抗等于电阻值。

![]()

即:

![]()

(先确定R,R=ωLk;再确定C)

Design Step4:Calculate the Sbubber Dissipation

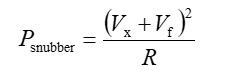

耗散功率由缓冲电容的大小决定。近似耗散由式(4)给出:

![]()

其中VDS是FET上的电压,由输入电压加上输出反射电压给出。在此计算中确保使用开关频率fs,而不是振铃频率。

注意:通常的1/2系数不会出现在此表达式中,因为当电容器充电和放电时,电阻都会耗散功率。充电是用电感完成的,因此,耗散可能比该表达式预测的要低一点。

Design Step5:Experimental Verification of Design

设计的最后一步是实验测试缓冲器。不要跳过此重要步骤。开关变换期间的测量误差、计算错误、引线长度过长和非线性电路元件都会影响缓冲器的工作性能。

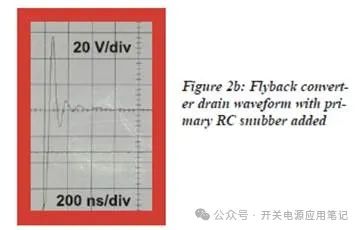

图2b所示为添加缓冲器后原边FET漏极上的振铃。注意到振铃很快就被抑制住了,大大减少了EMI。波形的峰值也大大降低。

仅使用简单的RC缓冲器很难进一步降低该电压尖峰。对于许多应用场合,RC缓冲器是最佳解决方案,但对于一些使用集成电源控制器的离线解决方案,有必要将该电压箝位到更低的值以防止FET失效。

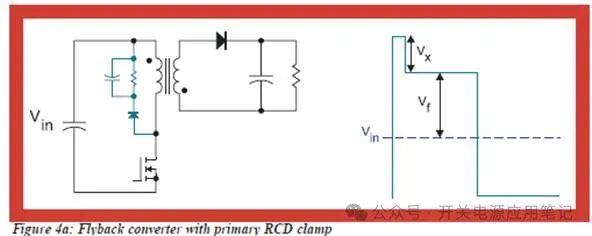

03 Primary RCD Clamp

图4a所示为RCD钳位电路,当RC缓冲器不足以防止开关过压时,用来限制FET漏极上的峰值电压。RCD钳位的工作原理是一旦漏极电压超过钳位电容的电压就会吸收漏感中的电流。使用一个相对较大的电容可以在一个开关周期内保持电压恒定。

RCD钳位的电阻始终消耗功率,即使主电路中没有功率也是如此。即使变换器负载非常小,电容器也始终被充电至变换器次级反射的电压Vf(极限条件下负载为0,则漏感中电流几乎为0,所以RCD电容上两端电压基本为0)。随着负载增加,更多的能量将流入电容,所以电压将在理想的方波电压基础上增加一个额外的量Vx,如图4a所示。

Design Step1:Measure Leakage Inductance

在设计缓冲器之前,漏感的测量至关重要要。前文已详细介绍了RC缓冲器的设计,对于RCD钳位,我们关心的是漏感中存储了多少能量而不是振铃频率处增加的漏感量。对于更保守的设计,最好使用在开关频率下测量的漏感量,而不是振铃频率。

再次强调不要猜测漏感,或使用1%规则作为其值。实际测量它以确保得到一个良好的缓冲器。

Design Step2:Determine Peak Clamp Voltage

需确定功率MOSFET电压降额,并计算在此钳位电压水平下的耗散功率。MOSFET关断时流过电流为Ip的漏感中存储的能量为:

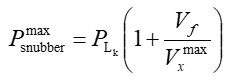

对RCD缓冲器的分析已出现在论文和许多应用说明中。假设没有对其他杂散电容充电,所有的泄漏能量都从漏感传导到缓冲电容中。假设缓冲电容足够大,其钳位电压值在一个开关周期内不会发生显著变化。基于这两点假设,RCD钳位的耗散功率可以用漏感存储的能量表示:

换句话说,FET上钳位的电压越高,整体耗散就越低(分子与分母的关系)。当然,必须平衡FET上的总电压VDS,因此也不能任意降低耗散。

典型的设计是电压Vx等于反激电压(Vin+Vf)的1/2,在这种情况下,耗散等于漏感中存储能量的3倍。然而,这是一个保守的估计。它不考虑电感的损耗放电,也不考虑杂散电容。实际上,由于这些影响,设计中的钳位损耗将比预期的要小。

对于高压离线设计,电压Vx将有一个由最大输入电压、最大电流和FET击穿电压设定的硬限制。不要超过FET规定的VDS,并且要注意击穿电压会随着温度的升高而降低。一些设计者依靠FET的雪崩能力,让他们经常超过击穿电压,为了获得高可靠性并不推荐这种方法。

Design Step3:Select Clamp Resistor

缓冲器的电容需要足够大,以在吸收泄漏能量的同时保持恒定的电压。除此考虑外,其数值并不关键,当缓冲器正常工作时不会影响峰值电压。

电阻值是决定Vx的关键参数,应遵循:

阻值越大,钳位电容放电速度越慢,则电压上升越高。阻值越小钳位电压越低,但会带来较大损耗。在大多数设计中,RCD钳位电阻值与前面所述的RC缓冲器的电阻值有很大不同。不要指望得到相似的值。

Design Step4:Calculate Power Loss

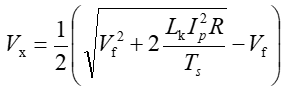

缓冲器的设计现在已经完成,但我们需要知道在最大电流以外的其他电流下的耗散情况。使用如下公式计算已知缓冲器在给定的峰值电流和漏感下的电压上升。Vx为:

耗散功率为:

Design Step5:Experimental Verification

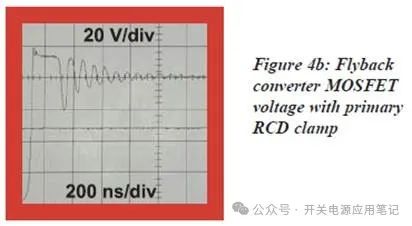

与RC缓冲器的设计一样,实验验证必不可少。图4b显示了该电路在箝位FET漏极电压峰值方面的有效性。

该图还显示了RCD钳位的局限性。钳位结束后,电路恢复振铃。对于理想元件,这种情况不会发生。然而,RCD钳位二极管存在反向恢复时间,这使得漏感电流在二极管中以相反的方向流动,从而导致振铃。因此为RCD缓冲器选择的二极管类型是至关重要的。它必须在合适的额定电压下尽可能快地运行。(反激RCD二极管选择trr时间较长的,如:整流二极管)。

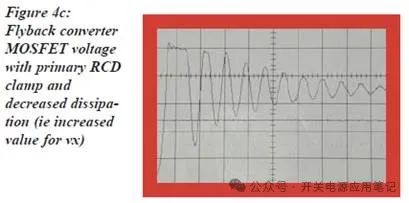

这种振铃的严重程度将取决于RCD二极管上的反向电压。允许钳位电压爬升越高,耗散就越低,但施加在二极管上的电压和dv/dt就越高。仅仅20ns的关断延迟是振铃波形周期的一个重要部分。 图4c显示该振铃如何随着钳位电压的升高而增大的。虽然FET仍然得到了很好的保护,但此情况下的RCD缓冲器并没有解决振铃引起的EMI问题。

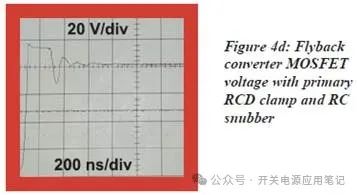

随后,可以通过重新RC缓冲器来再次抑制振铃。图4d显示了同时使用RCD钳位和RC缓冲时的漏极电压波形。这为FET提供了最佳保护和最低的EMI,但会导致最高的功耗。

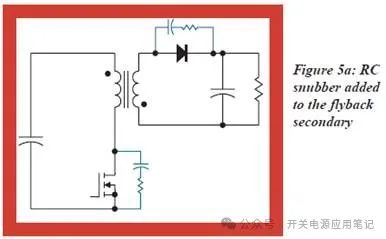

04 Secondary RC Snubber

为了保护主功率开关,许多设计人员花费大量时间为原边设计有效的缓冲器。设计完成后,初级侧的波形看起来很干净,而另一个噪声和应力往往被忽视。

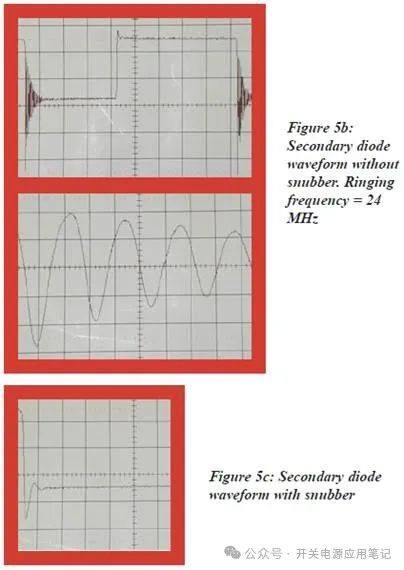

如果将探头放在变压器副边,由于输出二极管的关断,会观察到另一个振铃现象。图5b显示了两种不同时间尺度下的波形。施加在输出整流二极管上的过压是很严重的,而且往往比原边波形的破坏性更大。特别是肖特基二极管,对压非常不宽容,这些振铃波形必须以类似于初级波形的方式加以抑制。

次级缓冲器最好直接放置在二极管上。副边缓冲器的设计与原边缓冲器几乎相同。确保使用正确的漏感值,该值由测量的原边感量除以匝数比的平方计算得出。

注意副边波形比原边波形更明显地不对称。次级电容以二极管电容为主,变压器的影响很小。因此,半导体电容的非线性更加明显。

可以看到,副边振铃频率远高于原边振铃频率,分别为24 MHz和12MHz。这是好的,因为它使得副边耗散最小。振铃频率相对于开关频率越高越好。

图5c显示了副边使用RC缓冲器的结果。波形的阻尼非常有效,耗散功率小于100mW。

此外,不要忘记变换器的辅助绕组输出。每个次级二极管都需要施加一个RC缓冲器以适当保护器件。

248

248

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?