Verilog 的基础知识

前言

上一篇文章介绍了Verilog的综述,下面咱们就开始讲解 Verilog 的基础知识,进一步了解Verilog,从而更好的加以使用。

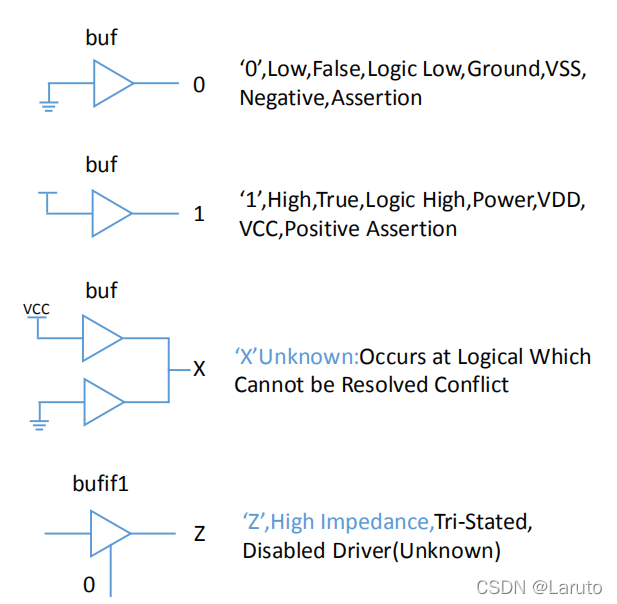

一、Verilog的四值逻辑系统

首先我们先来讲一下 Verilog 的四值逻辑系统,大家看下图 。

在 Verilog 的逻辑系统中有四种值,也即四种状态:逻辑 0:表示低电平,也就对应我们电路 GND;逻辑 1:表示高电平,也就是对应我们电路的VCC;逻辑 X:表示未知,有可能是高电平,也有可能是低电平;逻辑 Z:表示高阻态,外部没有激励信号是一个悬空状态。

二、Verilog的数据类型

在 Verilog 语言中,主要有三大类数据类型,即寄存器数据类型、线网数据类型和参数数据类型。从名称中,我们可以看出,真正在数字电路中起作用的数据类型应该是寄存器数据类型和线网数据类型,它们共同遵守 Verilog 的四值逻辑系统。

1.寄存器数据类型

首先我们介绍的是寄存器数据类型,所谓寄存器数据类型就是表示一个抽象的数据存储单元,它只能在 always 语句和 initial 语句等过程语句中被赋值,它的缺省值为 x。在实际的数字电路中,如果该过程语句描述的是时序逻辑,则该寄存器变量对应为寄存器;如果该过程语句描述的是组合逻辑;则该寄存器变量对应为硬件连线;如果该过程语句描述的是不完全组合逻辑,那么该寄存器变量也可以对应为锁存器。由此可见,寄存器类型的变量不一定会综合为寄存器。寄存器数据类型有很多种,如 reg、integer、real 等,其中最常用的就是 reg 类型,它的使用方法如下:

reg a; //定义 a 为 1bit 的 reg 类型

reg [7:0]<

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2814

2814

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?