一、概述

1.1 芯片封装的概念

指将制备合格芯片、元件等装配到载体上,采用适当连接技术形成电气连接,安装外壳,构成有效组件的整个过程,封装主要起着安放、固定、密封、保护芯片,以及确保电路性能和热性能等作用。

封装对集成电路气质机械支撑、机械保护环境保护的作用,可以为被封装的对象传输信号和分配电源、散热等作用。

封装材料

金属封装、陶瓷封装、金属陶瓷封装、塑料封装

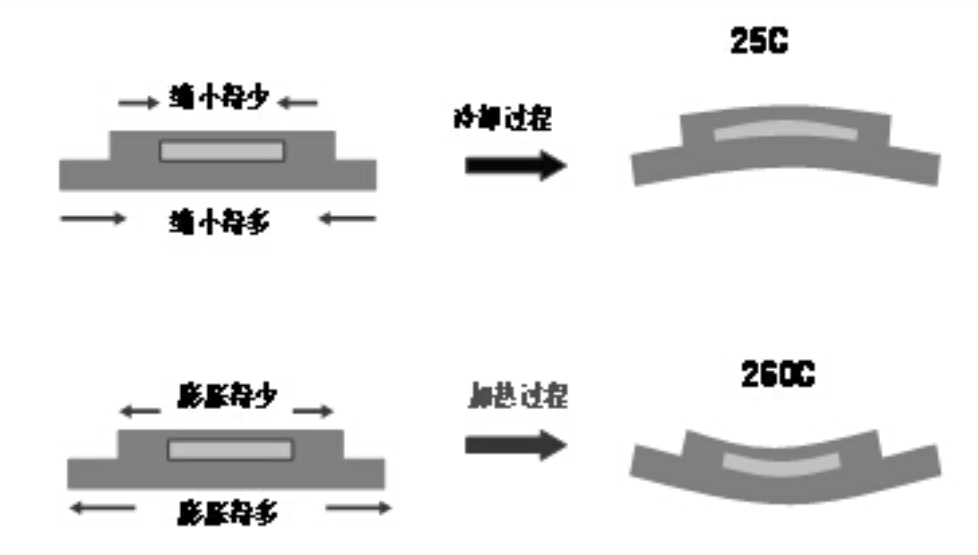

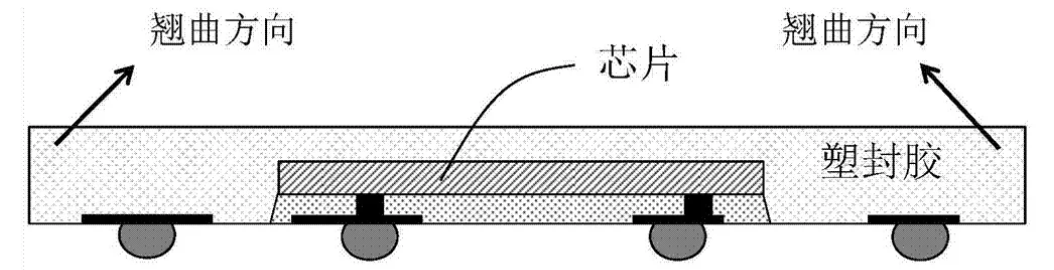

芯片封装的翘曲问题

翘曲一般发生在再流焊工艺中,材料间热膨胀系数的差异及流动应力的影响,再加上黏着力的限制,导致整个封装体在封装过程中受到了外界温度变化的影响,材料间为了释放温度影响所产生的内应力,通过翘曲变形来达到消除内应力影响的目的。

在预热阶段,不同的膨胀系数、不当涂膏或部件放置不当等,导致部件的一端从焊膏分开,直接的热传导被缝隙阻断,如果热量通过部件传导,则一端的融化焊料相对于另一端形成新月形 ,其表面拉力的曲转力矩比部件的重量大而引起部件的翘曲。

1.2 封装的发展历程

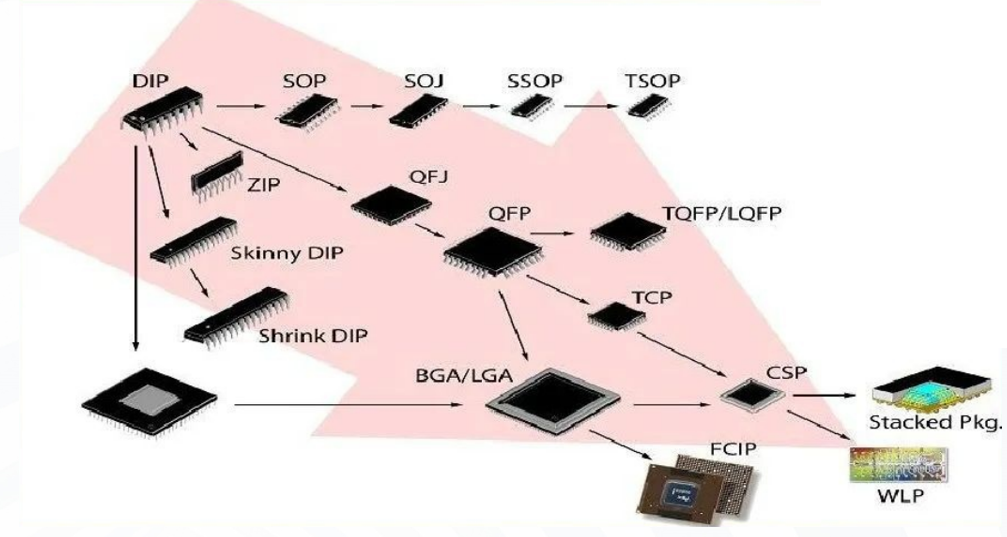

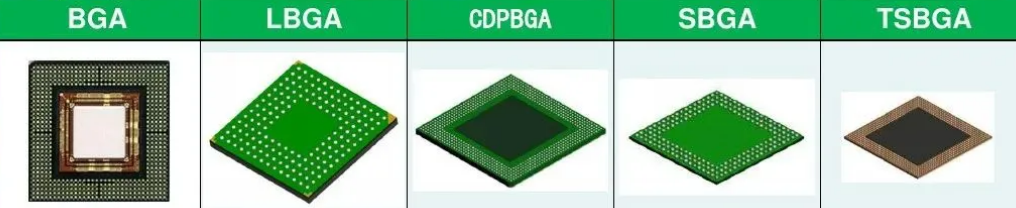

芯片封装技术发展可分为四个阶段。

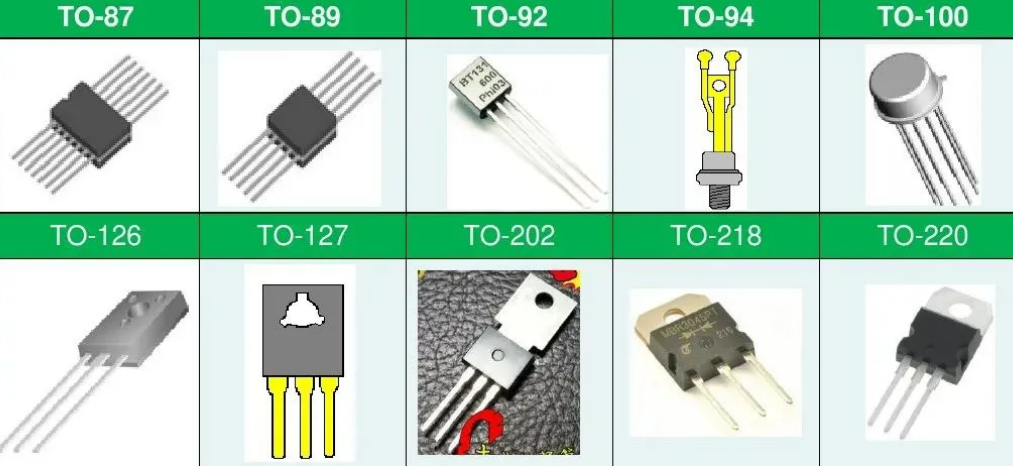

第一阶段:通孔插装阶段

插孔安装在PCB上,应交节距固定,引脚数增加伴随着封装尺寸的增大

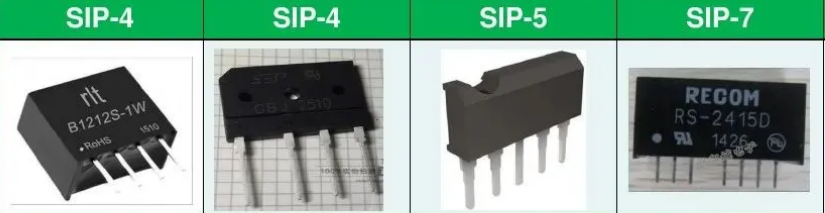

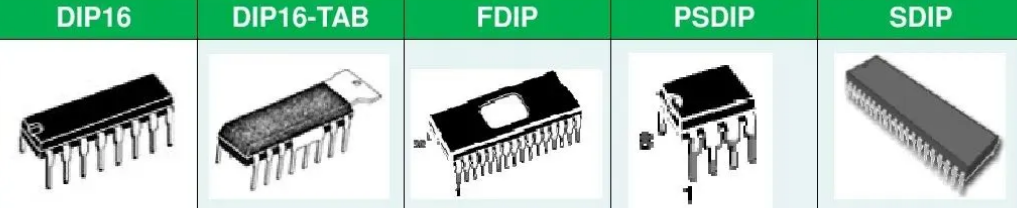

封装形式通常是:TO型封装、单列直插式(SIP)、双列直插封装(DIP)

如图是TO型封装,数字代表引脚间距

如图是SIP封装:

如图是SIP封装:

如图是DIP封装:

如图是DIP封装:

根据管脚间距、窗口封装也衍生出SDIP、FDIP等封装方式。

第二阶段:表面安装器件阶段

引线代替针脚,并成L型,封装题的尺寸固定儿周边引脚节距根据需要变化。这种封装形式大大提高了管脚和组装的密度,是封装技术的第一次革命。

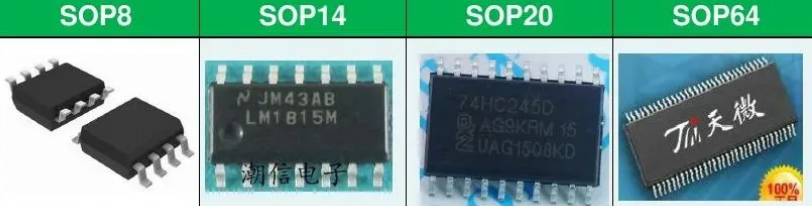

常见的封装是小外形封装(SOP)和扁平封装(QFP)。

从SOP衍生出来很多其他型号,比如根据管教间距更小、厚度更薄的SSOP,带散热片的HSOP等。

如图是SOP封装,数字代表引脚数

如图是QFP封装,呈方形,引脚为L型引脚,引脚数一般在100个以上

如图是QFP封装,呈方形,引脚为L型引脚,引脚数一般在100个以上

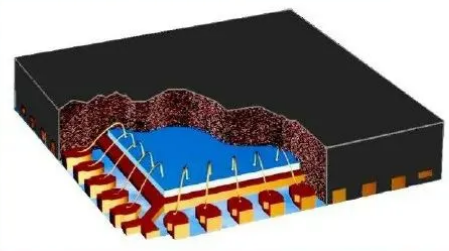

如题是QFN封装,相比QFP,QFN只有两端的焊盘,没有L型引脚

第三阶段:面积整列表面封装阶段

使用表面焊球代替引线,按面积阵列形式分布的表面贴装。

常见的封装是焊球整列封装(BGA)、芯片尺寸封装CSP

如图是BGA封装,外形呈方形,底部为焊球的栅格整列,根据基板材料和层数有衍生版本

第四阶段:高密度封装时代

在不改变封闭体安装面积的前提下,在同一个封装体内与垂直方向叠放两个以上的芯片,这种封装形式已经开始超越传统意义上的水平方向的封装,封装开始进入先进封装时代。

芯片的封装始终朝着高性能、高密度、低成本的方向迈进。

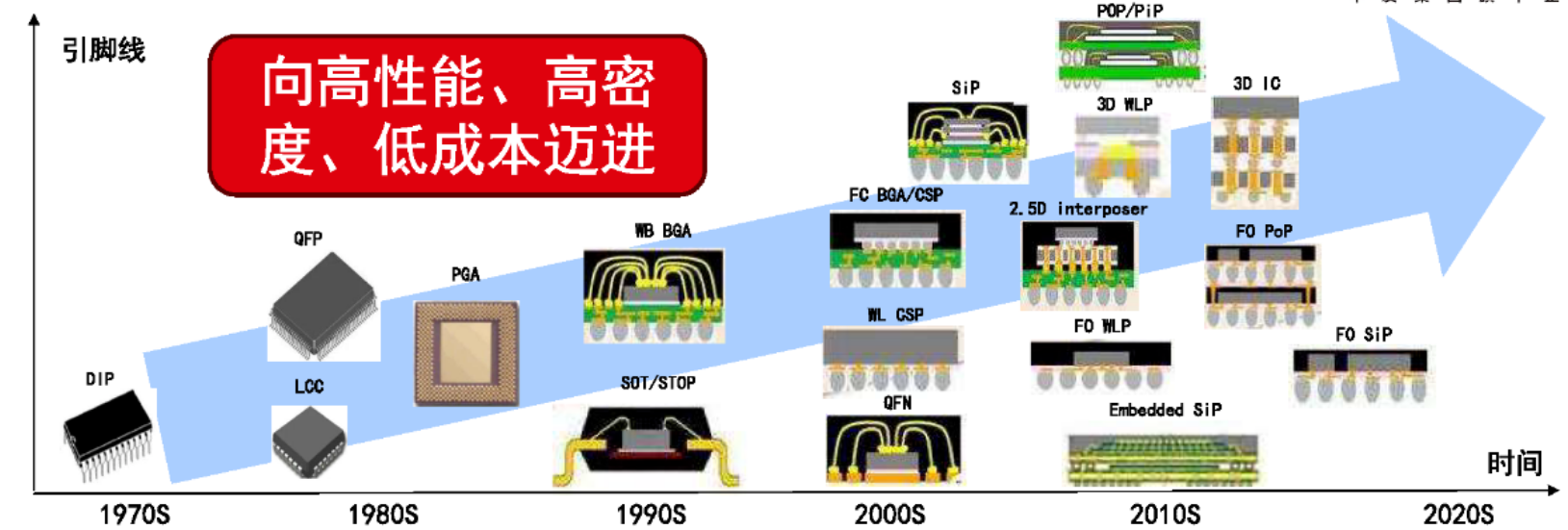

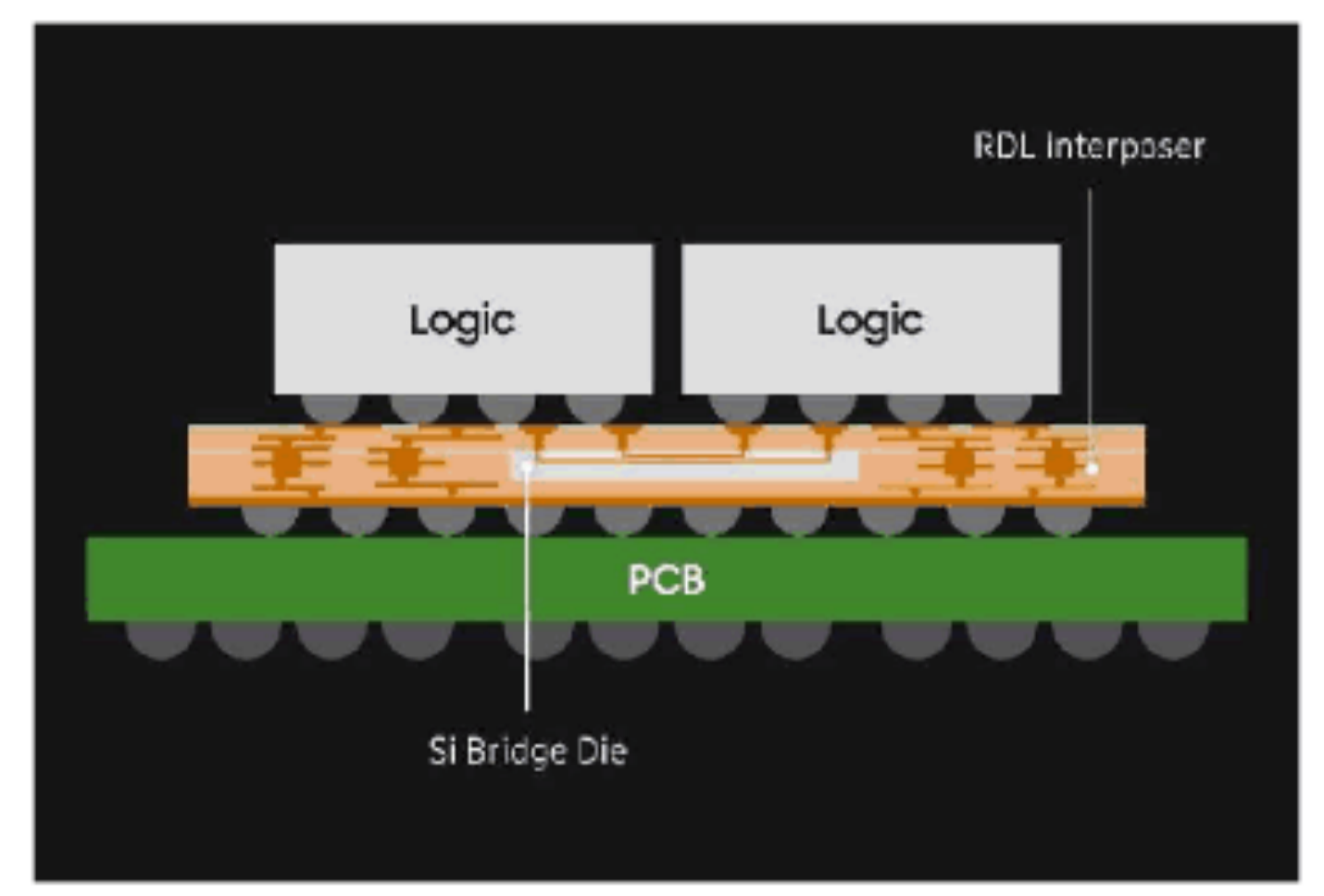

3. Laminate w/Si Bridge

3. Laminate w/Si Bridge

嵌入式桥接技术(EMIB),由Intel提出并积极应用

4. Fan-out(RDL)

通过RDL层来实现信号的传输,典型工艺为台积电InFo工艺,应用于智能手机

5. Fan-out w/Si Bridge

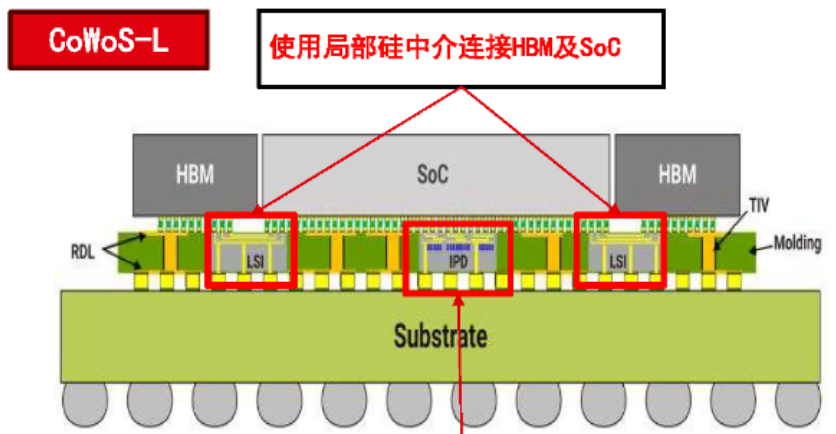

硅中阶层传输信号,RDL层传输电源和地,典型工艺为台积电CoWoS_L工艺

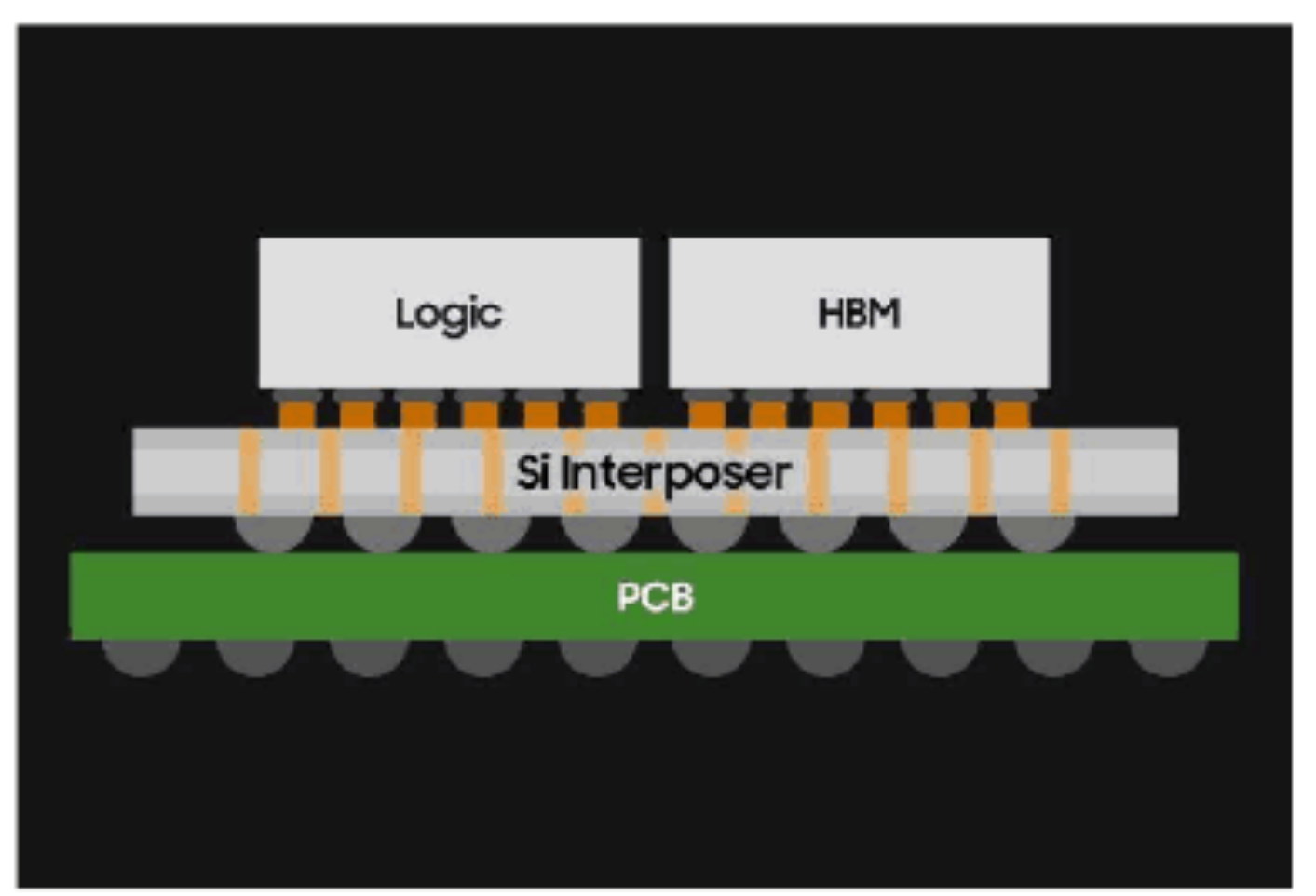

6. Si interposer

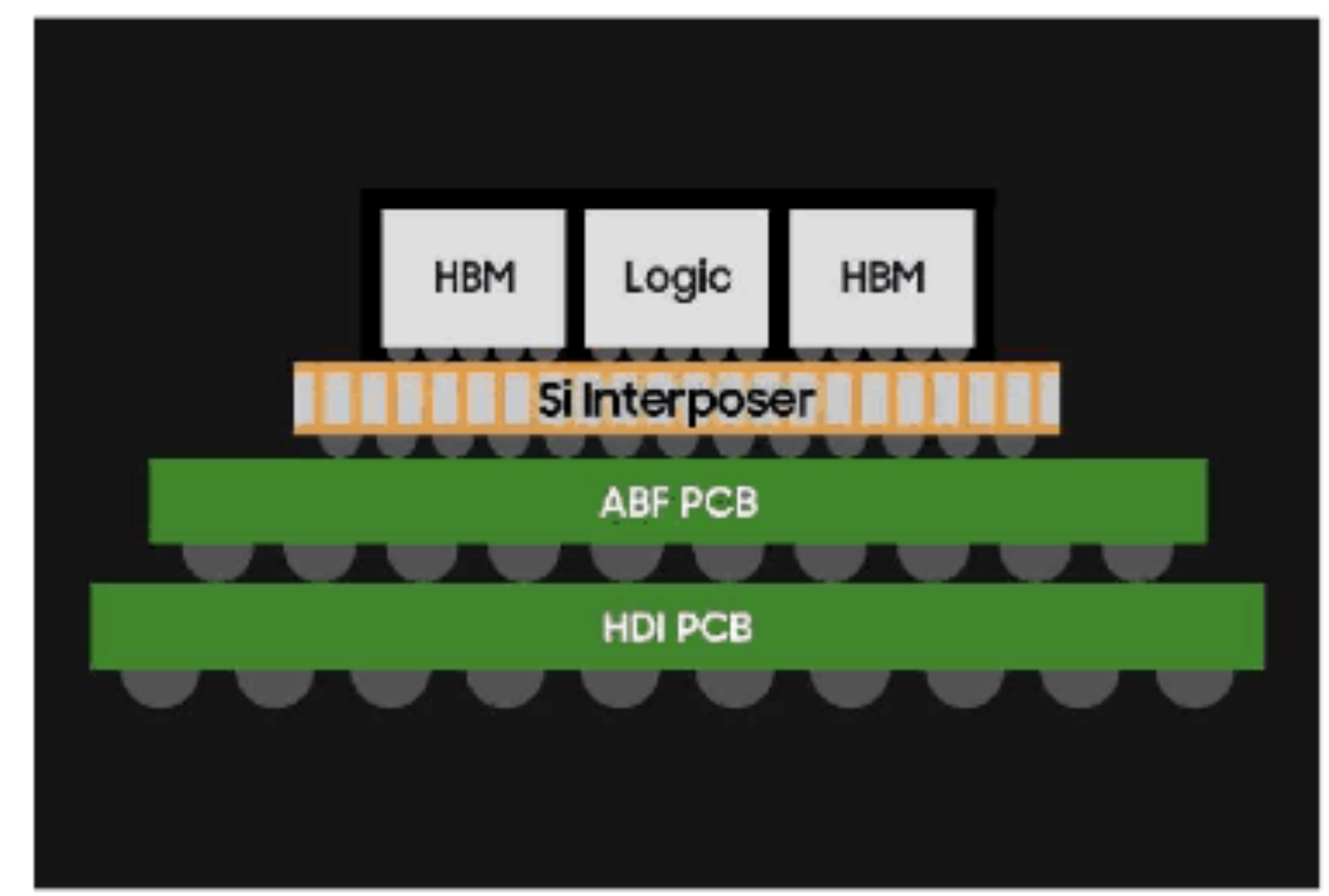

2.5D封装技术,在基板和die之间放置了额外的硅中介层,die之间的通信通过硅中介层中的连线进行。典型工艺为台积电CoWoS_S工艺,针对于高性能计算市场,主要集成logic层和HBM颗粒。

根据封装密度又可分为如下封装形式,如图所示为封装密度和成本关系示意图:

1.3 封装连线方法

1.3.1 引线键合(Wire Bonding)

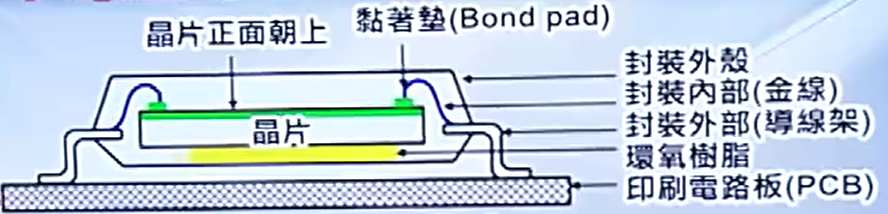

引线键合是传统的封装方式,具体过程是将晶圆切割为晶粒(Die)后,使晶粒贴合到相应的基板架的小岛(LeadframePad)上,再利用导线将晶片的接合焊盘(Bond pad)与基板的引脚相连(WireBond),实现电气连接,最后用外壳加以保护(Mold,或Encapsulation)。典型封装方式有DIP、SOP、TSOP、QFP等。

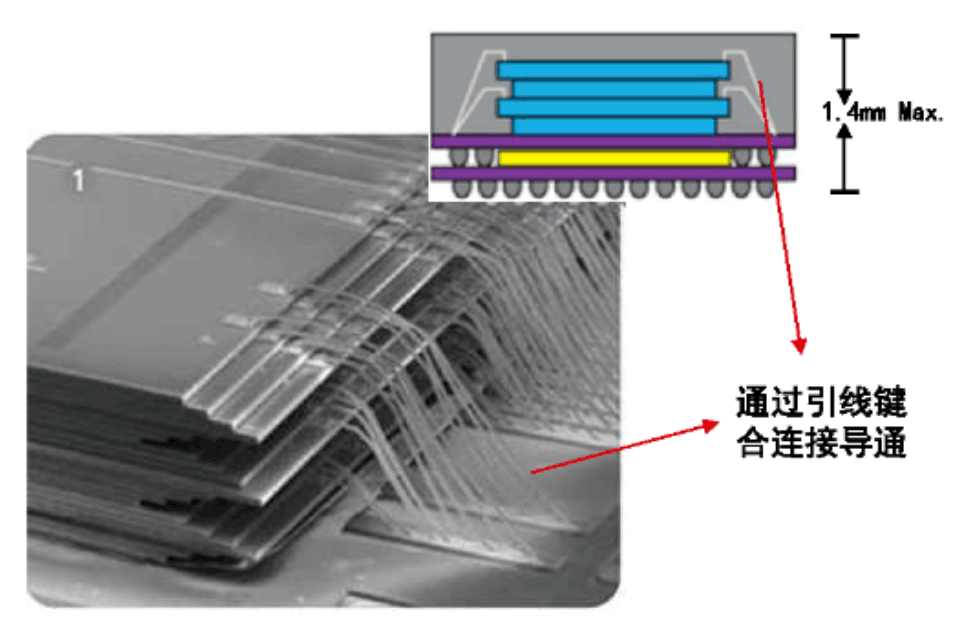

在存储芯片的封装中,引线键合的方式方式也很常见。

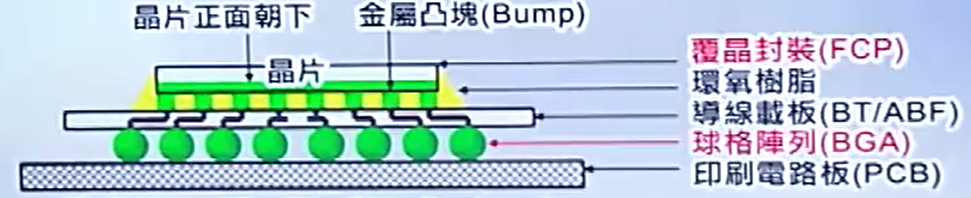

1.3.2 覆晶封装(Flip chip packege)

也就是常说的倒装,倒装使在die地板上沉积锡铅球,将芯片翻转加热,利用熔融锡铅球与导线载板相结合来替换传统的引线键合。

倒装将die正面朝下,将整个芯片面积与基板直接连接,节省了引线,具有更好的电器性能。

bump和die直接有一层金属过渡层,主要起粘附和扩散阻挡作用。

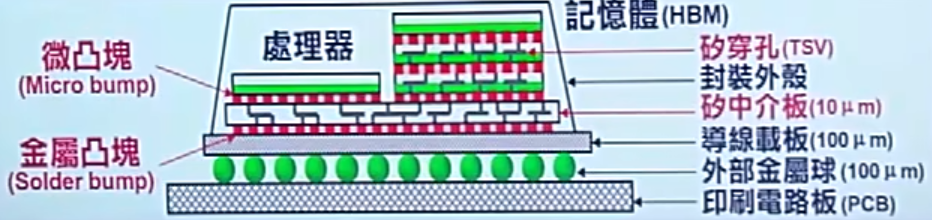

硅通孔TSV

随着Moore定律的放缓,单die的封装已经不能满足芯片高密度集成的需求,因此出现了通过TSV在中介层打孔布线,实现2.5D以及3D的高密度布局布线的封装。在芯片堆叠封装时,使用引线键合连接各个堆叠die的侧面,随着die数量的增多,引线变得更加复杂,且需要更多空间容纳引线,相比之下,硅通孔芯片堆叠则不需要复杂的布线,因此封装尺寸更小。

具体方法:通过硅片上钻孔,并填充金属等到店材料来实现芯片垂直互联。通TSV实现die to die互联或者die与substrate互连。

先进封装的特征

根据封装的层次可分为传统封装和先进封装。区别在于连接芯片的封装,先进封装可在更小空间内实现更高设备密度,并使功能得到扩展,通过TSV、桥接器、硅中介层或导线层完成芯片的合封或堆叠,从而提高信号传输速度,减小能耗,降低空间需求。

芯片封装的前三阶段都属于传统封装范畴,从第四阶段开始进入先进封装时代,广义的先进封装指2D封装,2.5D/3D封装等。从TSV出现开始,封装再次经历了一次大的变革,此后通常称2D封装是标准封装,狭义的先进封装则包括2.5D封装、3D封装等。

die的bump

bump间距

bump大小

bump类型

-

C4

-

microbump

die间布线

封装先进程度的衡量指标是die间距。

- die间距越小,线长就越小,信号衰减也越小,信号完整越好,;

- 同时封装能容忍的布线密度越大,单位面积内的信号线数量越多,信号衰减和串扰也就越小,SI也会更好。 而影响布线密度的因素处理布线层的性能,也包括线宽,以及bump大小材料,归根结底也就是封装厂工艺水平

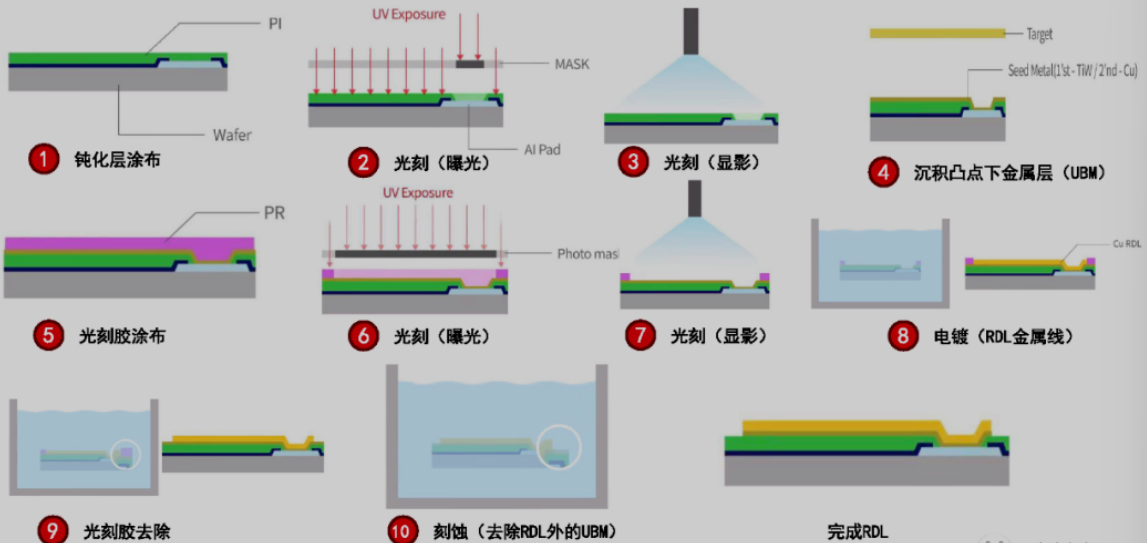

重新布线层RDL

晶圆级封装一般需要RDL工艺(Re-distributed layer,重布线层),因为晶圆上的焊盘大部分是铝焊盘,无论是做晶圆级封装还是板级封装,铝金属不易做后续处理,都需要用另外的金属来覆盖铝。RDL是将原来设计的芯片线路接点位置(I/O pad),通过晶圆级金属布线制程和凸块制程改变其接点位置,同时满足焊球间最小间距的约束。

鄙人理解:重新布线层可以是封装基板,也可以是interposer,根据工艺水平而定。

RDL的制造方法:

中介层interposer

中介层是一种有硅或有机材料制成硅基板,是先进封装中多芯片模块传递电信号的通道,可以实现芯片间的互连,也可以实现与封装基板的互连,充当多科裸片和电路板之间的桥梁。具有较高的细间距布线能力和可靠的TSV能力,可以先高密度IO需求,在先进封装中扮演重要角色。

interposer分为passive interposer(无源中介层)和active interposer(有源中介层)、photonic(光中介层)

无源中阶层没有器件,只有走线,优点是面接较小,封装良率更高

有研究表明,即使与无源硅插入器相比,有源插入器对于大型SoCs也具有成本效益1。

晶圆级封装(WLP)

WLP指现在正片晶圆上同时对众多芯片进行封装、测试,最后切割成单个器件,并直接贴装到基板或PCB上,生产成本大幅降低。

由于没有引线、键合和塑胶工艺,封装无需向芯片外扩展,使得WLP封装尺寸几乎等于芯片尺寸

二、2D 封装

比较成熟的制造工艺,各家工艺厂商的定义基本类似,2D封装

MCM封装

有机基板封装方式,pitch可达130~150um。

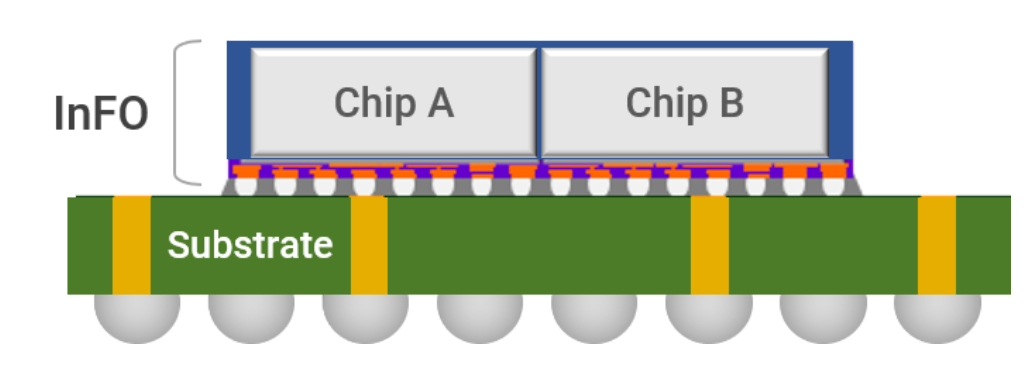

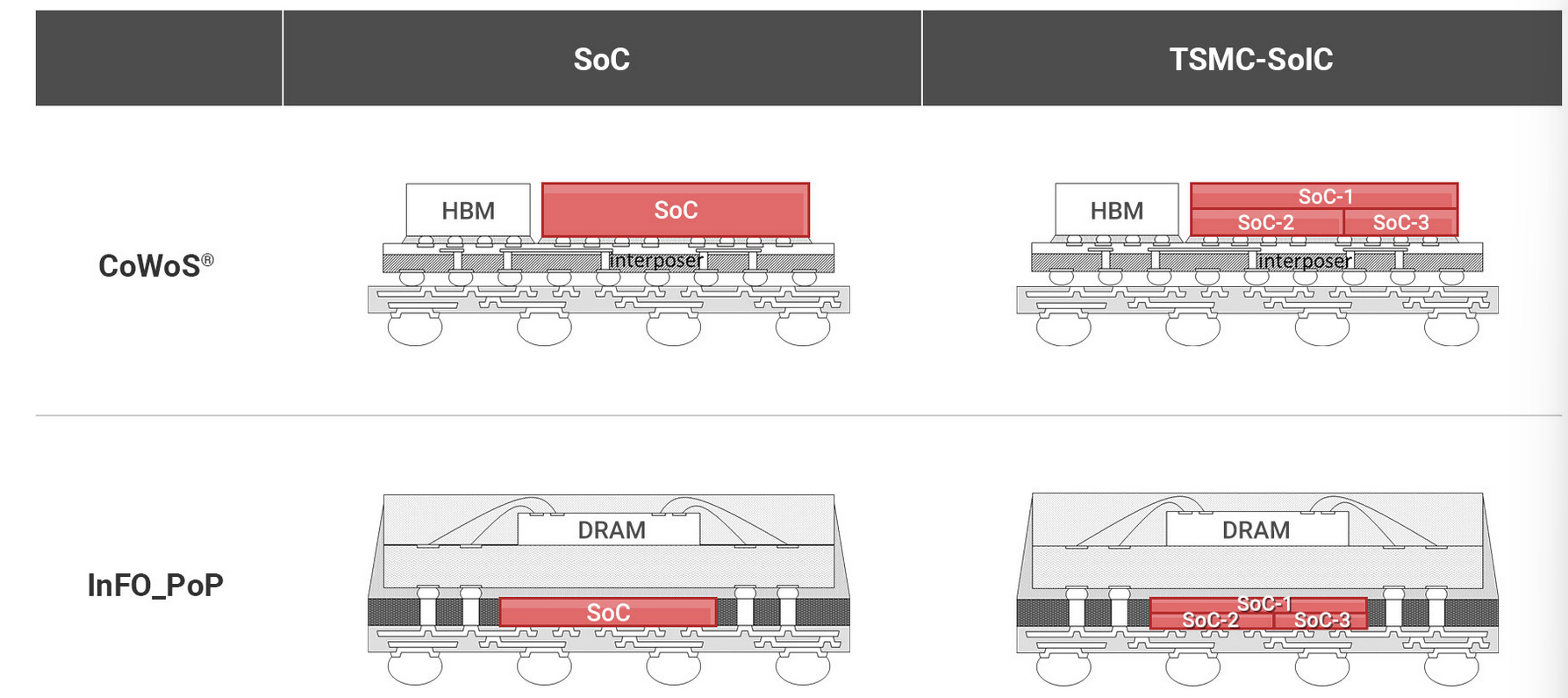

TSMC InFO封装技术

Intergrated Fan-Out,即整合型扇出层叠封装技术,使用高密度的RDL层和TIV(Through InFO Via)进行die间互连。

主要分为InFO_PoP和InFO_oS。

InFO_PoP是扇出晶圆级封装和PoP封装的集合体

InFO_oS

die无需集成bump,die间数据走线直接通过RDL层进行

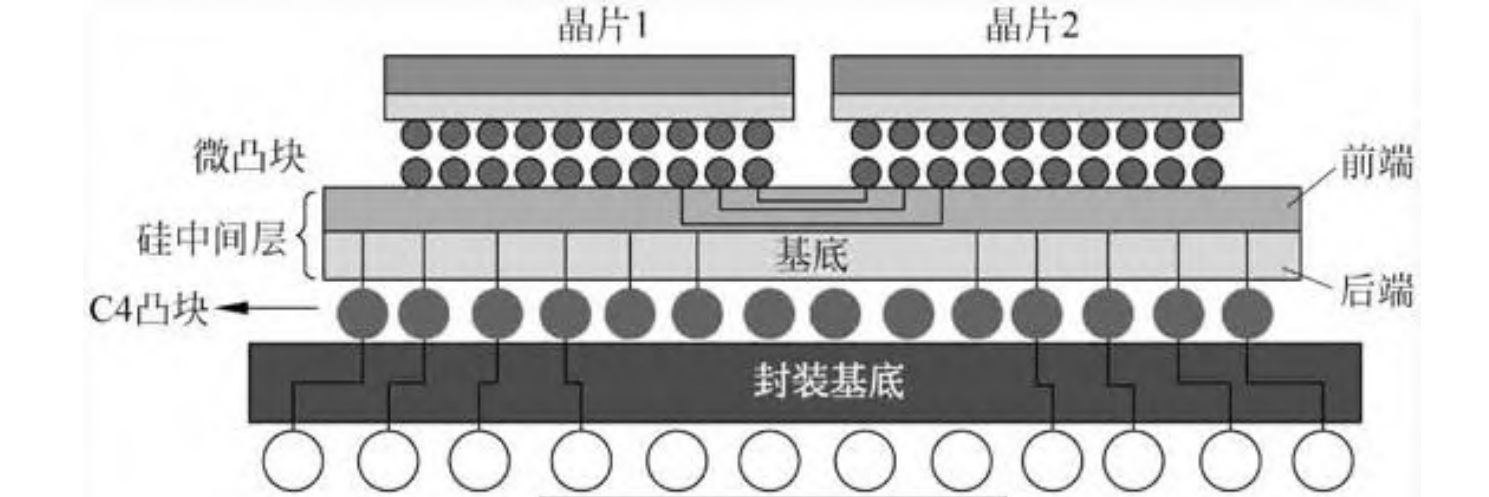

三、2.5D 封装

2.5D封装相比较2D封装,在硅中介板上排布CPU、HBM等die,并经由bump连接,interposer上分布了不同die间的连线,该过程为前段工艺;整体芯片的引脚通过TSV穿过interposer的基板层连接下方的金属凸块,再经由封装基底连接外部金属球,该过程为后段工艺,最终实现die、interposer、封装基板的连接。

如图是鲲鹏920 2.5D封装示意图:

2.5D芯片封装设计需要新的设计验证方法学。2.5D封装技术更加各家工艺厂商定义不同有不同的实现方式。

- 2.5D 封装的挑战

- die间信号/电源完整性分析

- 跨die的静态时序分析

- 高速通路的跨芯片跨尺寸的die间联合仿真

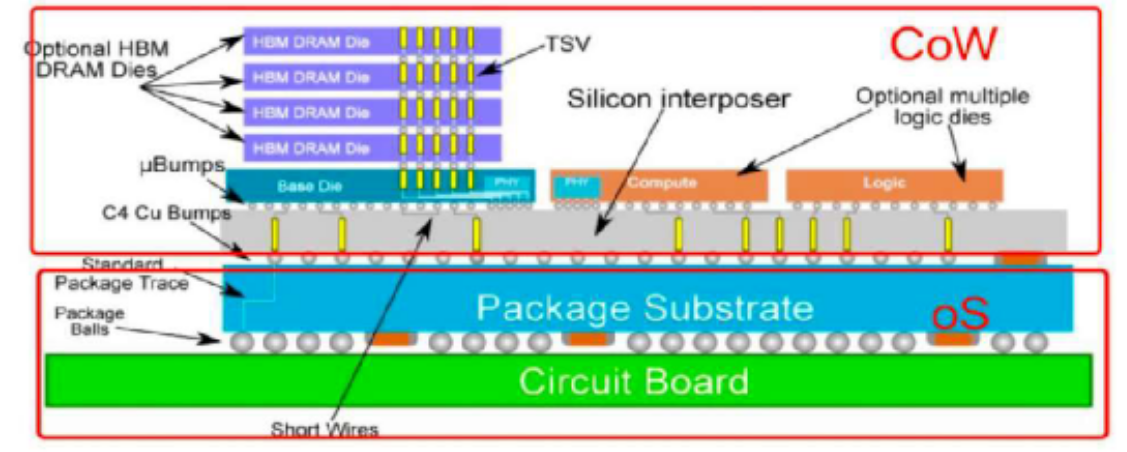

TSMC CoWoS封装技术

CoWoS是台积电制造H100、A100、Epic Genoe、MI300的先进封装技术。

CoWoS由CoW和oS组合而来,CoW表示Chip on Wafer,指裸片在金源上被拼接的过程,oS表示on Substrate。

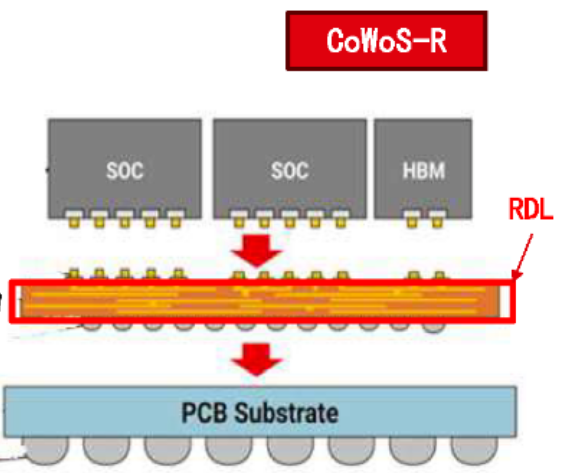

根据中介层采用不同技术划分为CoWoS-S、CoWoS-L、CoWoS-R三个系列,三个系列的pitch指标逐渐增大。

CoWoS-S采用硅中介层,主要面向HPC提供高密度晶体管,pitch可小于20um;

CoWoS-R类似InFO技术,利用RDL中介层进行互联,更抢到小芯片间互联,pitch可达40~55um;

CoWoS-L结合S和R的优点,使用夹层与LSI(局部硅互联)芯片进行互联,使用RDL层进行电源与信号传输,提供最灵活集成。

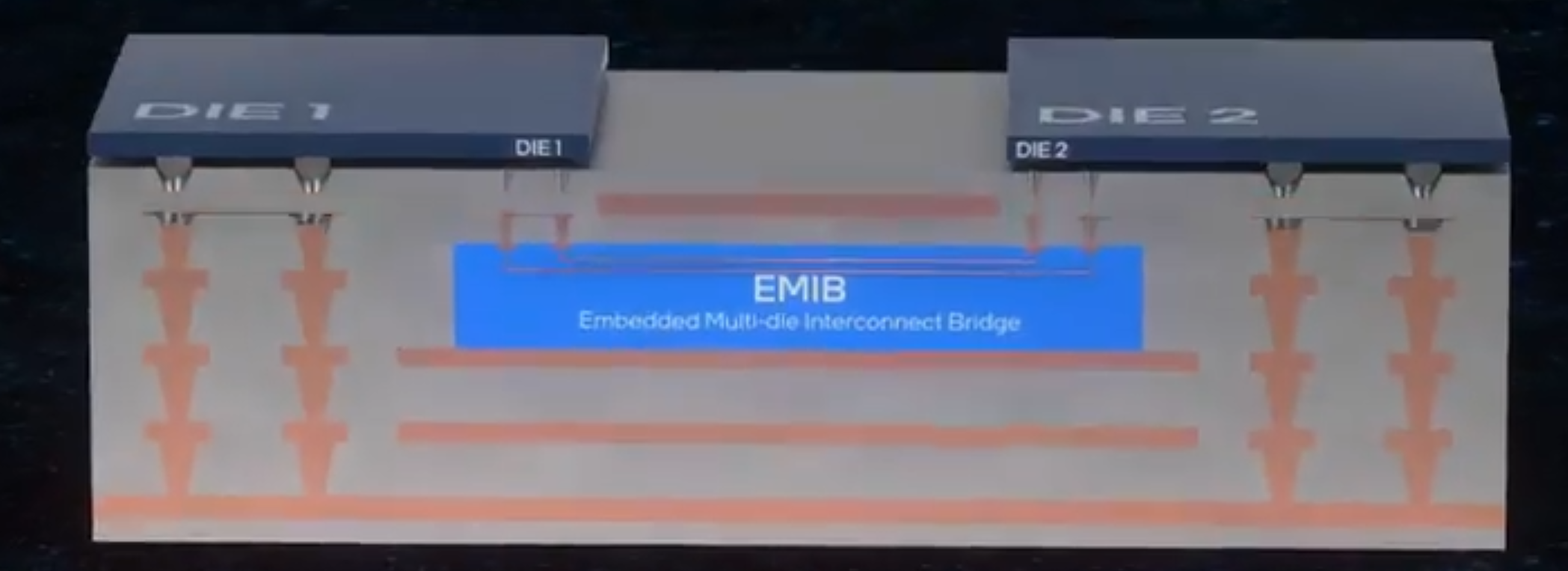

Intel EMIB封装技术

EMIB是Intel发布的先进封装技术,全称为Embedded Multi-Die Interconnect Bridge,意为“嵌入式多裸片互连桥接”。

具体将带有多层导电金属(back end of line, BEOL)互连的超薄硅片埋入封装基板的最上层,通过焊球和倒装芯片的连接,实现两个或多个芯片间的局部高密度连接。

相比interposer层的连接,该方式布线较短,体积更小,无需TSV的制作工艺,封装良率更高,成本更低。

Samsung I-Cube2.5D封装技术

三星的2.5D封装就技术分为三个系列,分别是I-Cube S、I-Cube E和H-Cube技术

I-Cube S是将逻辑die和存储die放置在一个硅中介层上,通过TSV与封装基板连接。

I-Cube E类似intel的EMIB技术,在基板中嵌入一个硅桥进行布线连接,因此无需TSV和interposer层。

H-Cube是一种混合基底结构,将精细成像的ABF基地和高密度互连的中介层相结合。

四、3D封装

3D封装和2.5D整体类似,不同的是,3D封装时通过硅穿孔将芯粒堆叠起来,上下芯粒间通过硅穿孔中的导线连接。

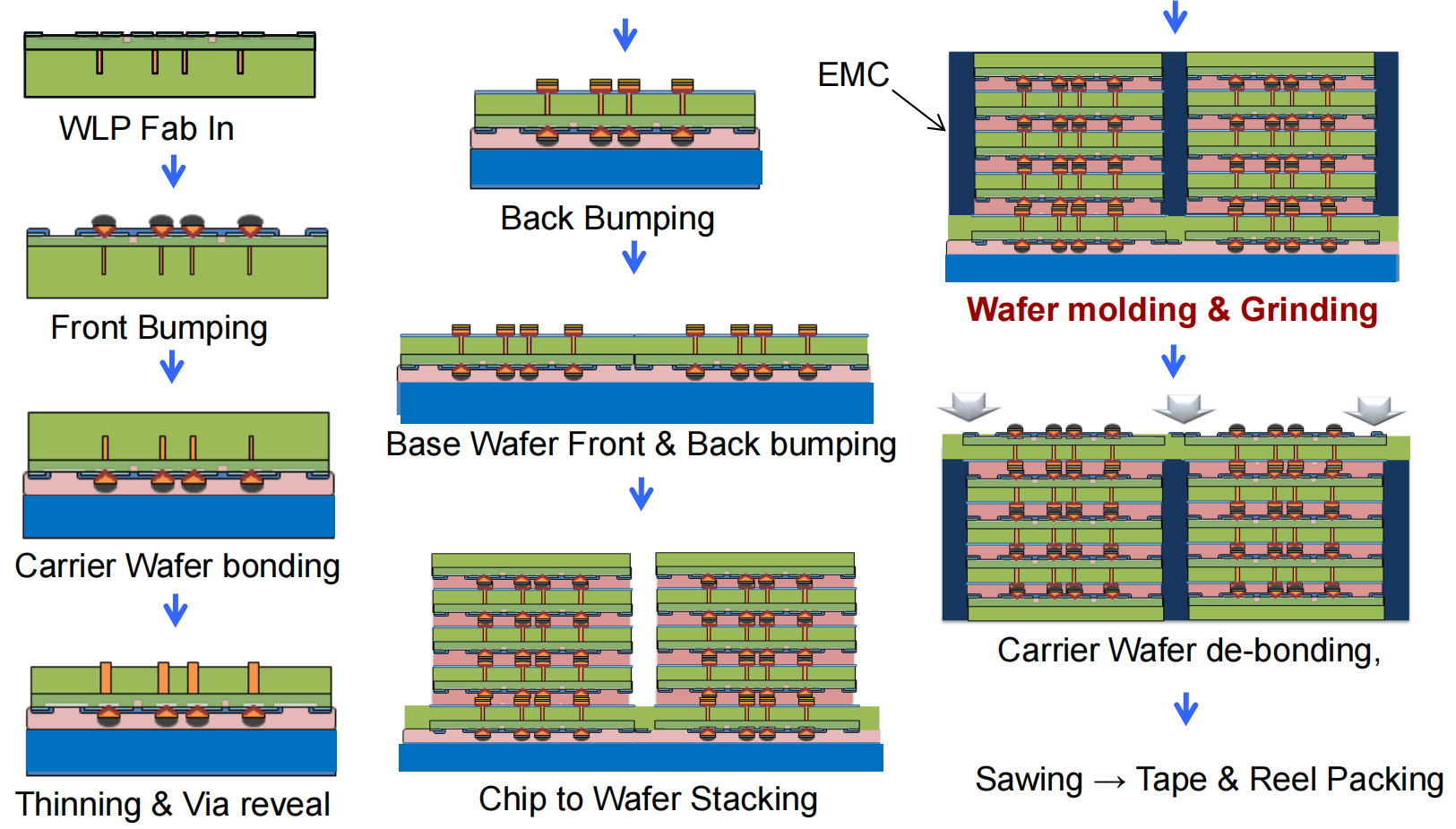

3D堆叠技术(WoW:wafer on wafer)

由于考虑到芯片的散热,该封装技术通常用于DDR芯粒的堆叠。HBM即使用3D堆叠技术

根据台积电2020年技术数据,芯粒堆叠最多可叠致8片。

3D封装的优势

- 相比2D封装,减少的Die连接线长和die占地面积,进而导致耕地的连接延迟和功耗

- 由于TSV的存在,获得更高的互连密度,缓解了2D封装下IO pin数量的限制

- 较小的footprint也使得芯片良率更高ao

3D封装流程

(图片来源于 3D ASIP, 2013 M. S. Seo )

Hybrid Bonding混合键合技术

HB最早应用于SONY高端CMOS图像传感器。通过把图像传感器警员、数据存储及处理器芯片的警员直接键合,实现大规模的图像数据高效并行传输,后来该技术广泛应用于逻辑芯片和存储芯片的3D互连。

相比3D堆叠技术,HB的bump pitch更小,布线密度更高,可靠性也更高。

TSMC SoIC 3D封装技术

SoIC技术先将同构或异构芯片垂直堆叠到单个die面积的区域上,再整体集成到后端先进封装(CoWoS/InFO)中。

SoIC技术主要分为Wafer-on-Wafer(WoW)和Chip-on-Wafer(CoW)。

WoW拓扑再晶圆上集成一个复杂的SoC die,并提供深沟槽电容(DTC)结构以实现最佳去耦;CoW拓扑则再晶圆上堆叠多个SoC die

SoIC-CoW

参考文献

华金证券——芯片封装详解

芯片传统封装讲解——知乎

TSMC 先进封装讲解——知乎

TSMC InFO技术——TSMC官网

- D. Stow et al., “Cost-Effective Design of Scalable High Performance Systems using Active and Passive Interposers,” in ICCAD, 2017.

1 ↩︎

1884

1884

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?