Intel的SoC架构分为client端和server端,以下二级标题为Intel每代产品的代号,同一代号的桌面端和服务器端产品架构区别挺大,有时服务器端架构也会用到桌面端芯片上。每一代代号代表一种微架构,每代微架构的变革很大。

一、桌面端SoC架构

1.1 Sandy Bridge

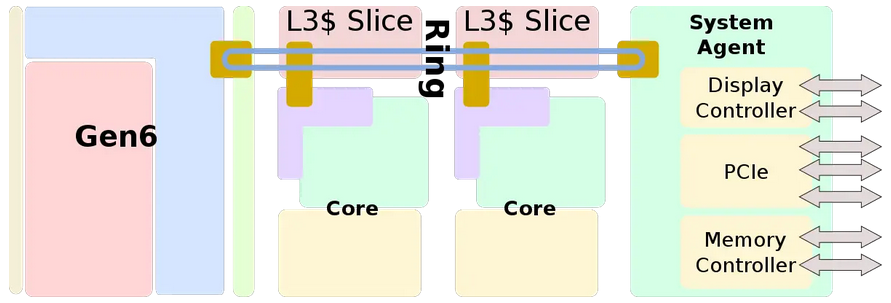

Intel 2010年推出的一种模块化设计解决方案的SoC,将SoC分为CPU、GPU、SA(System Agent)等多个模块,模块间通过ring总线互联。

Sandy Bridge

如图为双核架构:

- L1/2/3 写回策略

- L3 cache所有核共享,ring总线时钟域,26~31时钟周期的延迟

- 通过QPI总线连接2个die

Broadwell

- 2014年10月发布

- Intel 14nm

skylake

- 2015年发布

- Intel 14nm

-

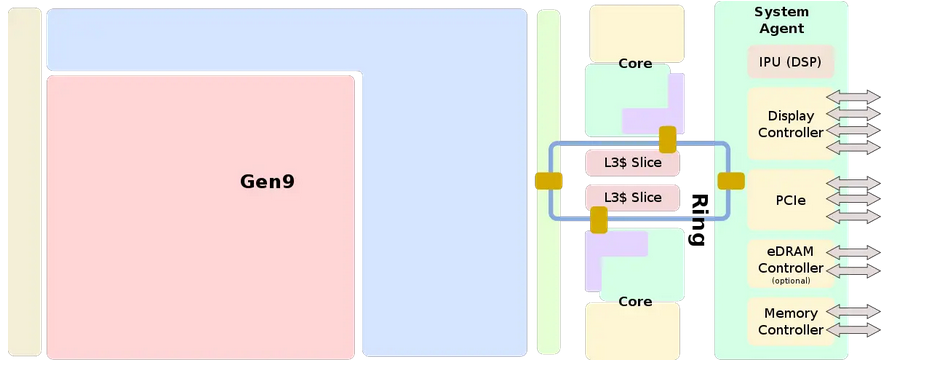

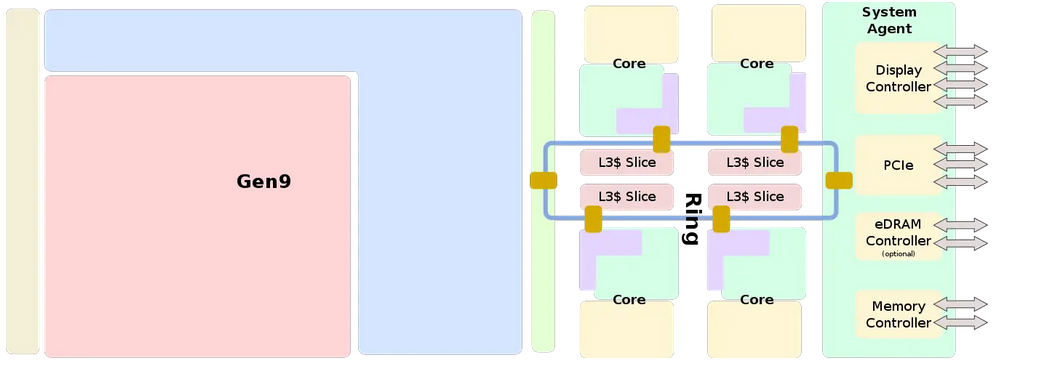

双核

-

四核

Kaby Lake

- 2016年8月发布

- Intel 14nm

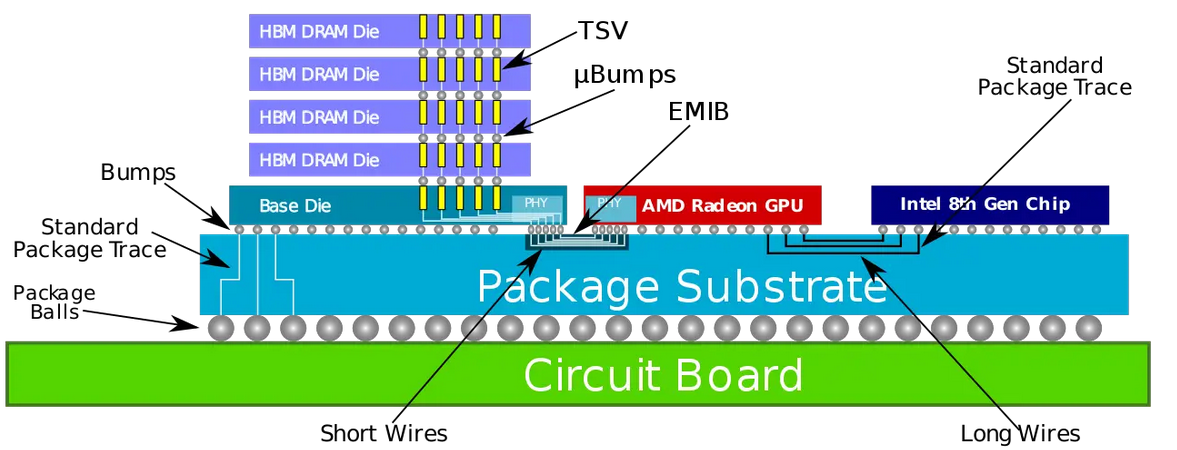

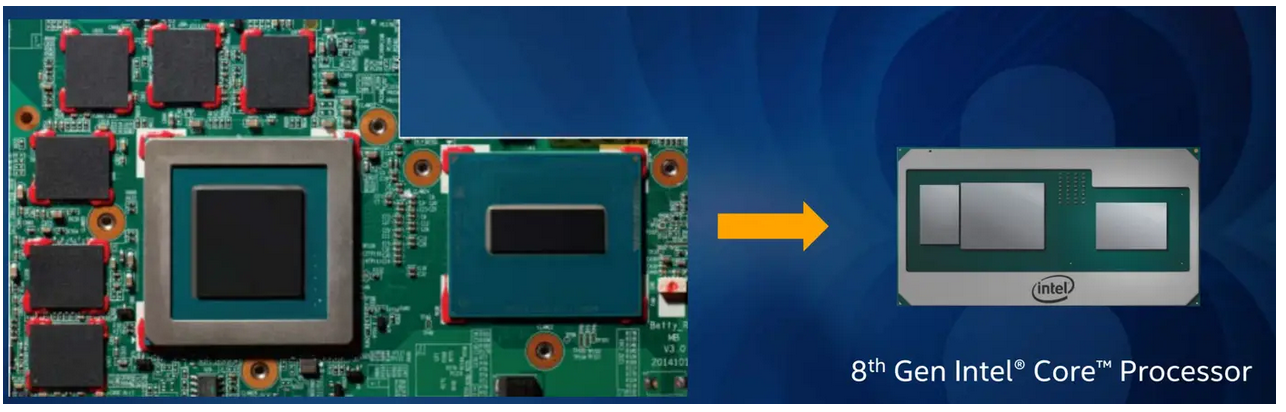

Kaby Lake G

- 2018年发布

Intel在这款芯片中采用chiplet技术,通过EMIB封装将自家的CPU die和AMD的GPU die在基板上封装在一起,二者通过PCIe协议连接

下图为示意图:

下图为实物图:

Coffee Lake

Icelake

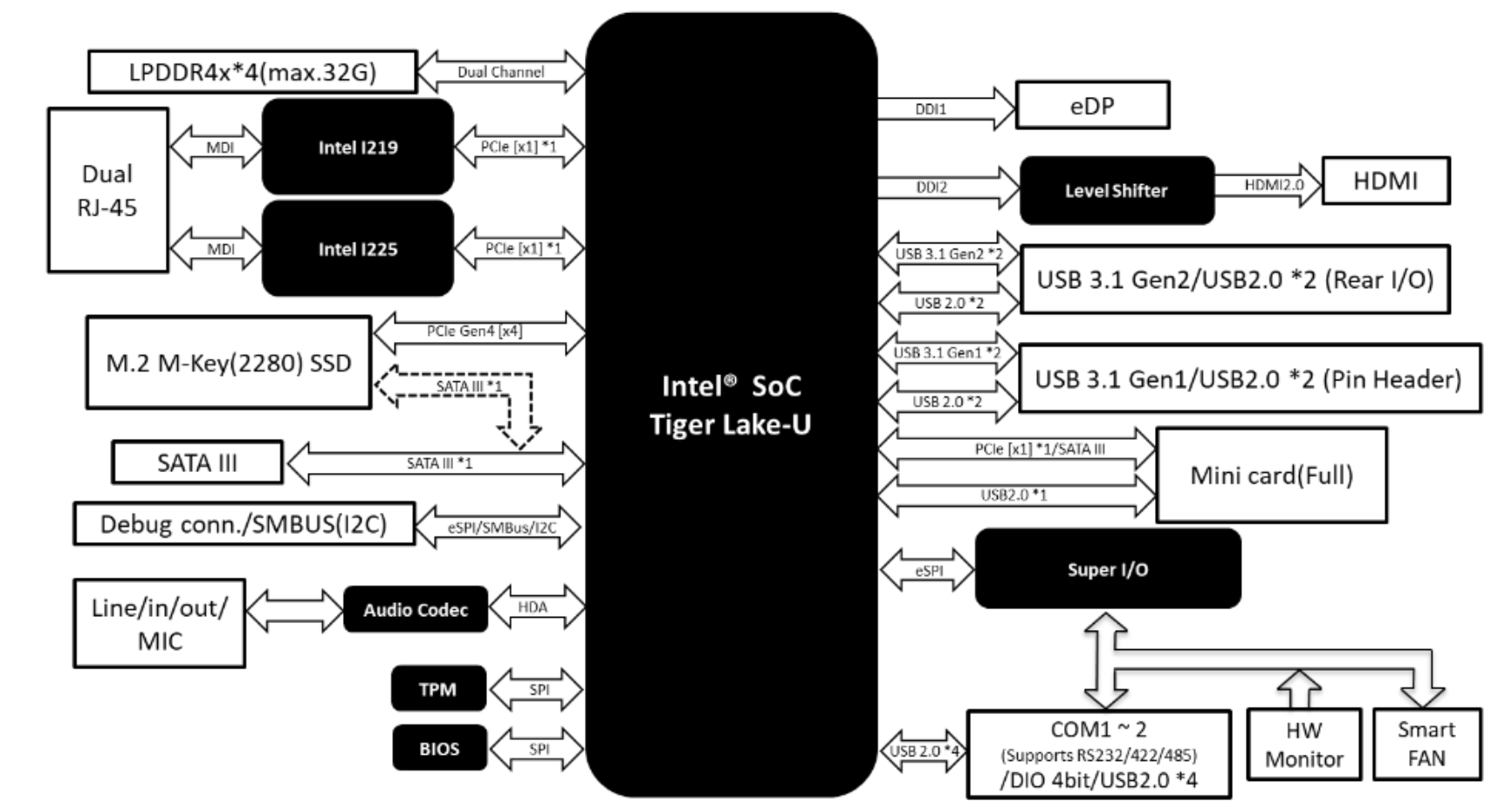

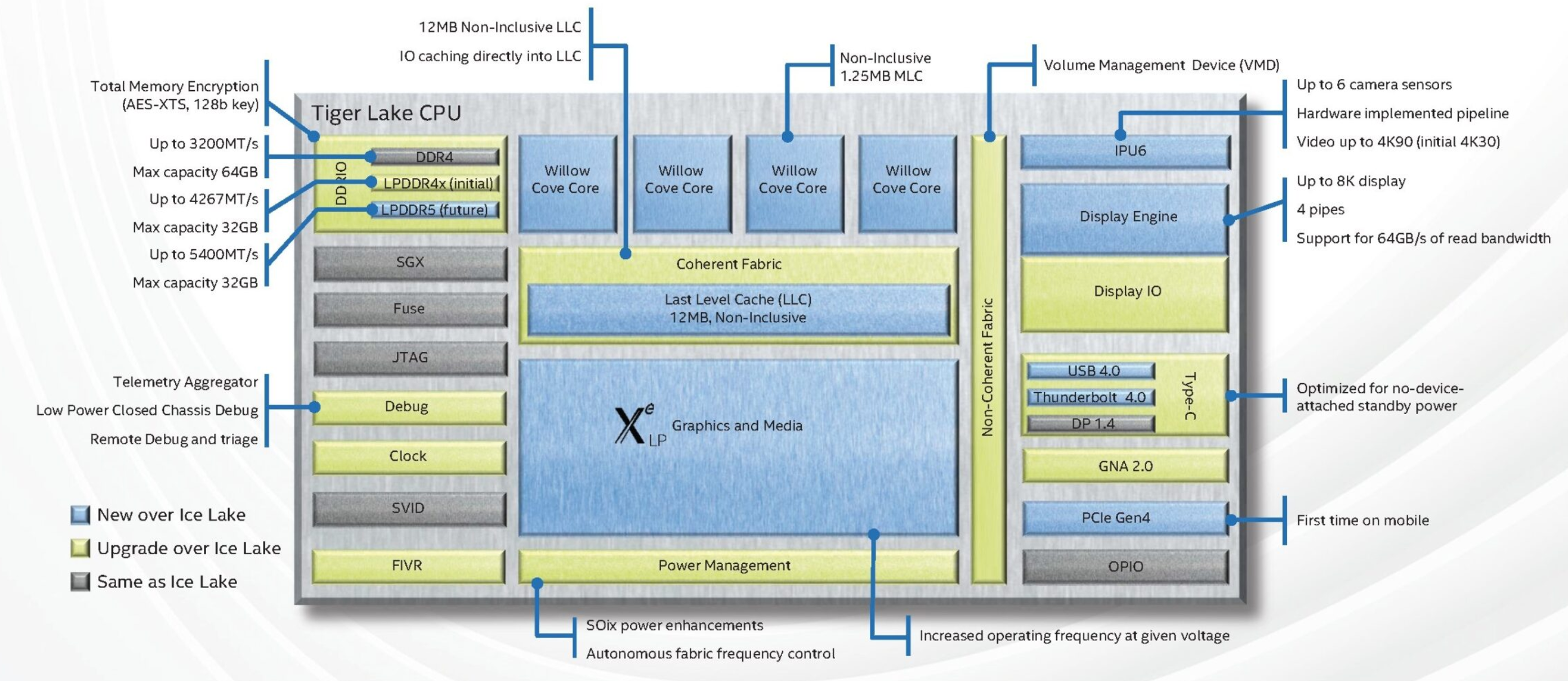

Tigerlake

Intel在第32界hotchips会议上发布了11代适用于移动平台的处理器架构Tigerlake,相比上一代Icelake,Tigerlake有如下创新:

- 基于Intel 10nm++制程工艺

10nm++是Intel的10nm SpuerFin晶体管工艺,相比标准的10nm工艺,可以获得17~18%的主频性能提升 - 采用最新的Willow Cove核

相比上一代Sunny Cove核,该核拥有更高的性能吞吐量 - 支持频率3200Mhz,容量64GB的DDR4控制器

- 处理器采用dual-ring互连架构

4路CPU核核Xe-LP集成GPU通过双路环状互连,运行频率可达1.3Ghz。

该型CPU面向移动平台,如笔记本、游戏本等市场,有Tiger Lake-Y, Tiger Lake-U 和 Tiger Lake-H等类型CPU。

Tiger Lake-U是面向轻量化笔记本邻域的CPU,共4核8线程,最高频率可达4.5Ghz,配备GT2 tier、12代Xe GPU,采用UP3封装。

Tiger Lake-Y与U系列配置类似,但采用UP4封装,也将支持LPDDR4X内存。

Tiger Lake-H是面向高性能领域的CPU,共8核16线程,L3cache达24MB,L2cache达10MB,支持AVX2和AVX-512指令集,配备二级内存和软件保护扩展,支持3200Mhz的DDR4。

架构框图:

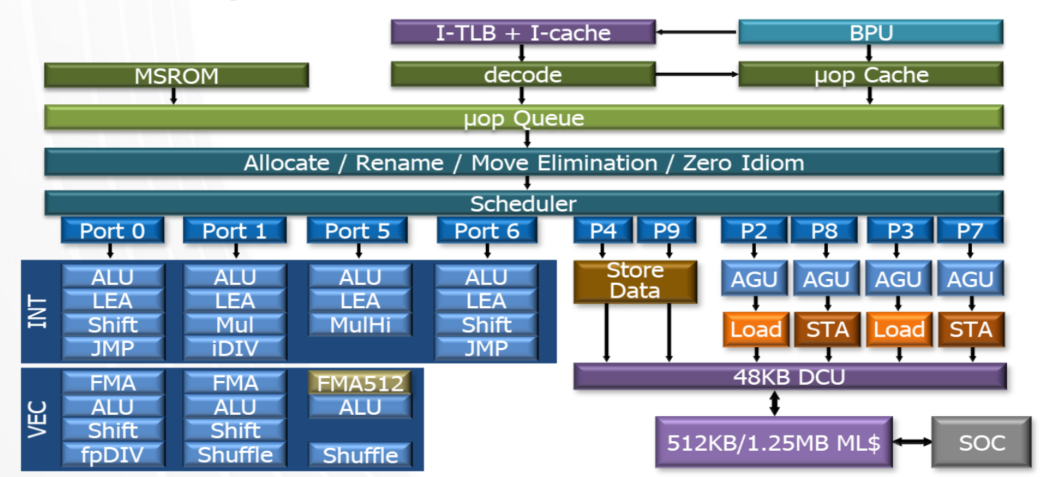

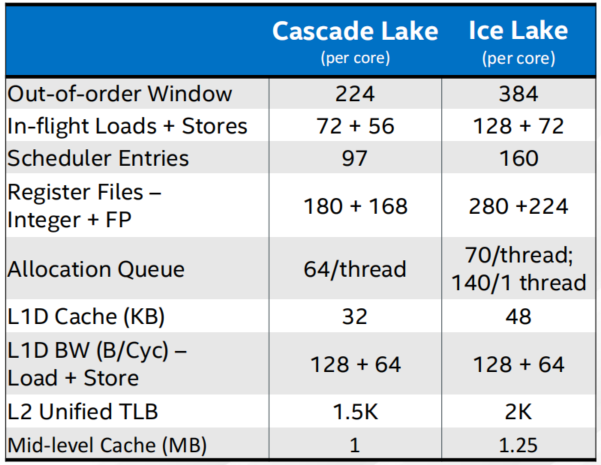

相比上一代Icelake有如下区别:

Alderlake

Intel经典的性能核+效率核的大小核架构

- 2021年发布

- 性能核:Golden Cove

- 效率核:Gracemont

二、服务器端SoC架构

2.1 Broadwell

- 2014年10月发布

- Intel 14nm

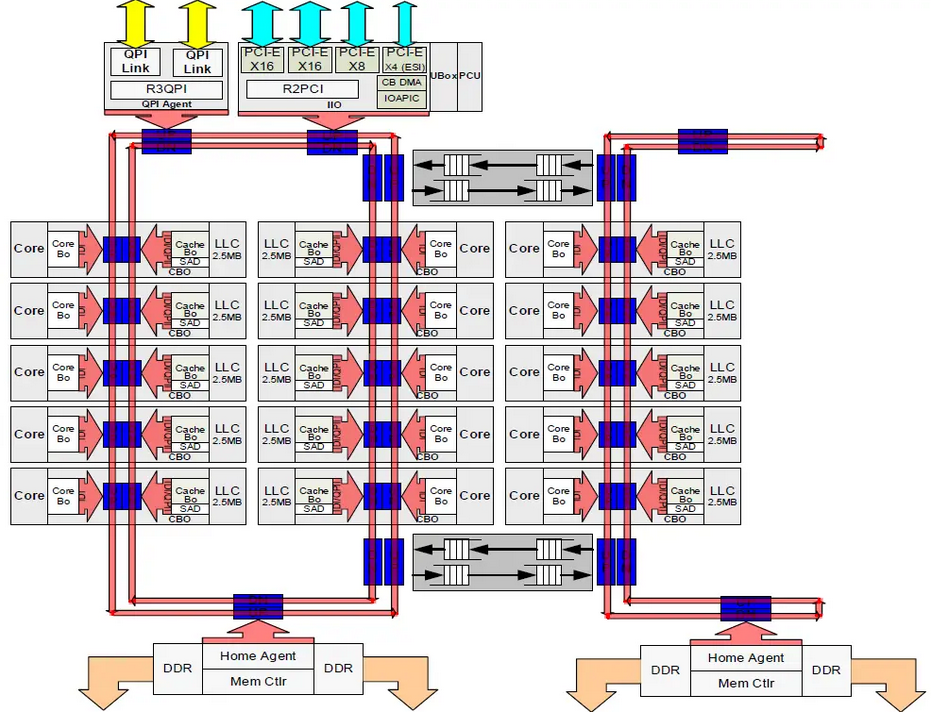

XEON E5 V4 LCC( low core count )

XEON E5 V4 MCC( medium core count )

XEON E5 V4 HCC( HIGH core count )

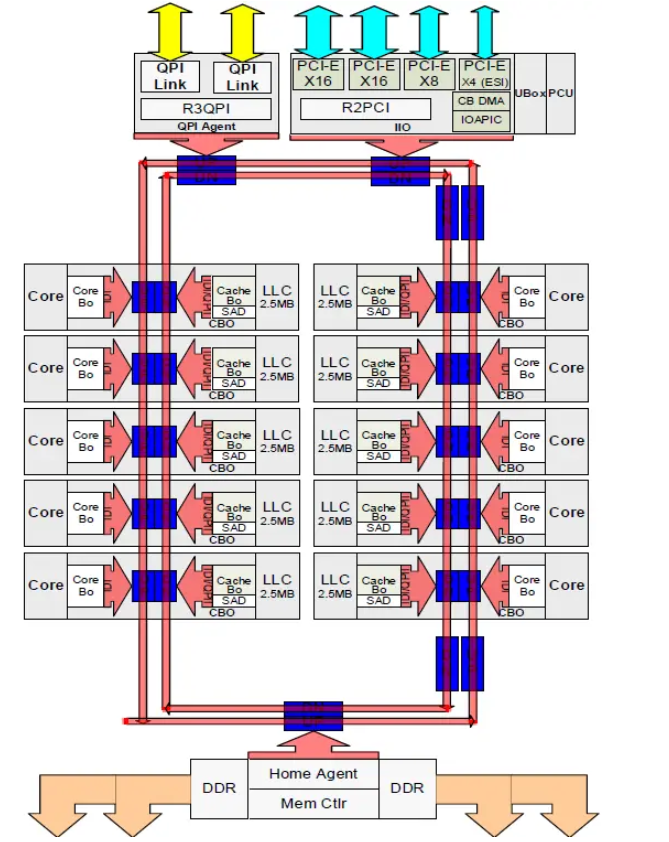

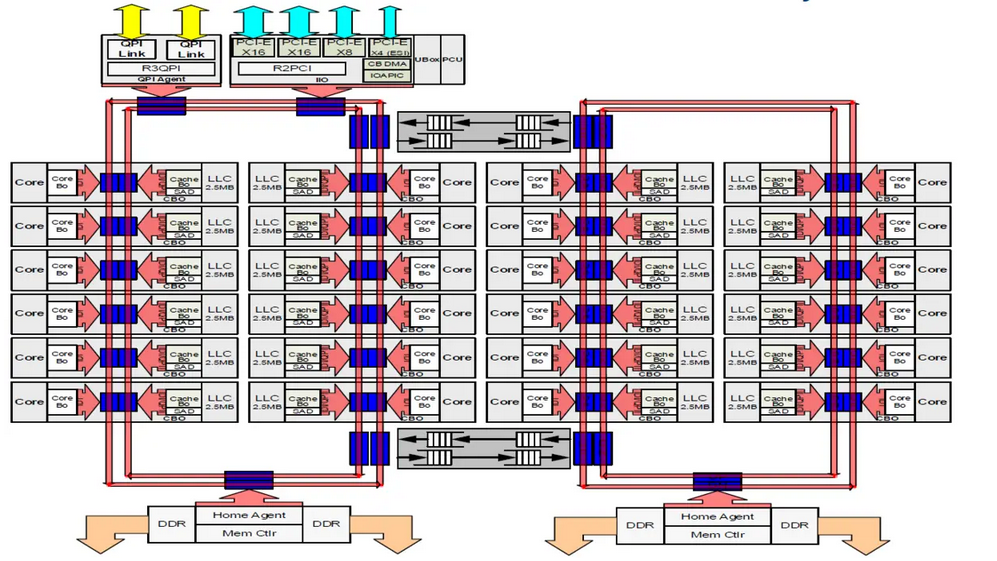

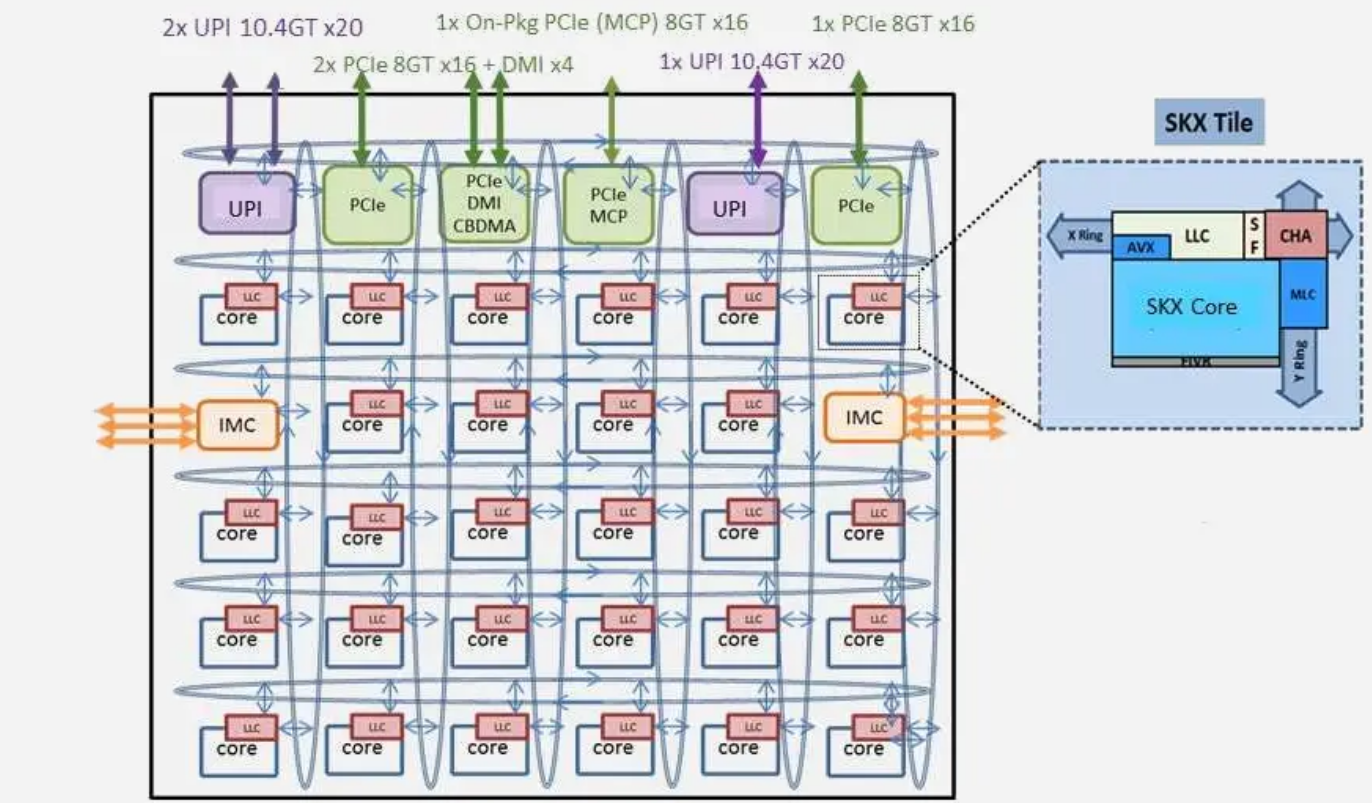

2.2 skylake

- 发布时间:2017年5月

- 工艺:intel 14nm

ring到mesh的变革

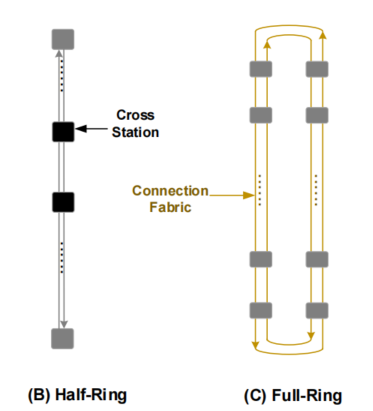

从skylake开始,Intel服务器SoC开始采用mesh网络替代ring网络1。原先的ring随着互联core数量的增加,访存延迟逐渐增大。intel尝试将大的ring网络划分成两半,这样减少了路由跳数,增加额外的带宽,但仍然不能解决日益严重的根本的低效问题。

由此,intel开始尝试mesh网络,mesh是由多个half ring垂直和水平摆放构成的2维阵列,half ring将core、存储节点和IO设备连在一起,每个节点都在两个half ring中,这种连接方式不仅减少了core-to-core、core-to-mem间的访存延迟,也减少了io与mem的延迟。

core上包含LLC、SF(snooping filter)以及CHA(caching and home agent),core通过CHA与ring连接,CHA可以进行地址映射、以及报文转发路由功能。

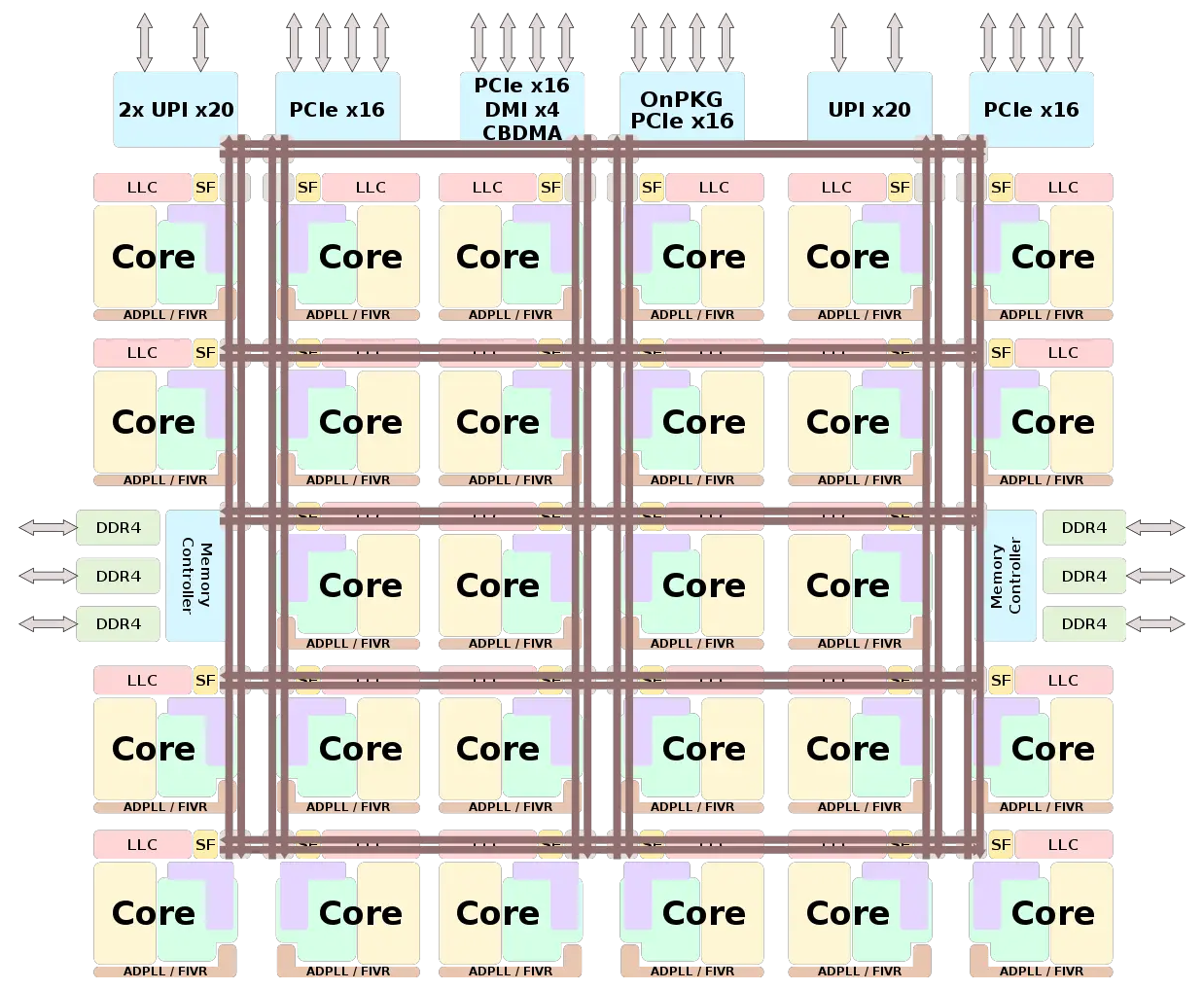

XCC SoC

面向高端领域的28核设计。

2.3 Cascake lake

XCC SoC

SoC架构图和Skylake得XCC版本一样。

2.4 Cooper Lake

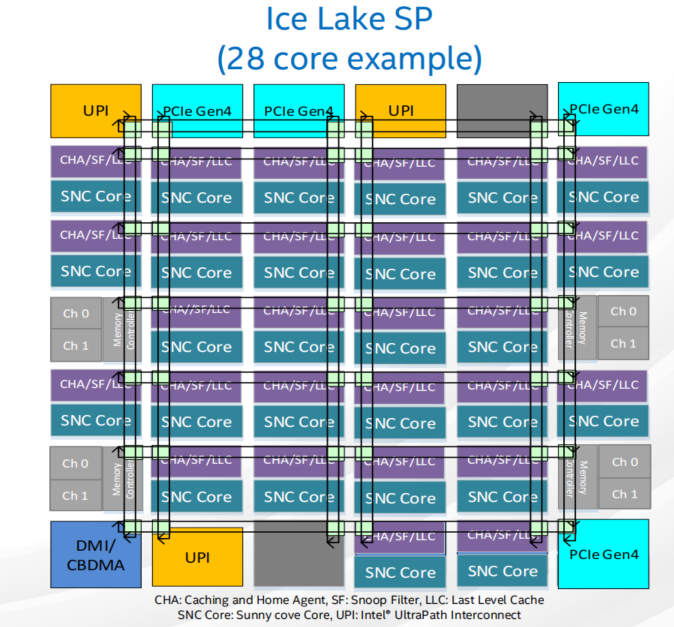

2.5 Icelake

- 2021年4月发布

- Intel 10nm

- 40cores die面积:640mm2

采用bufferless mesh网络集成40 cores

Icelake-SP

- 最早于2020年HOT会议上发布[3]

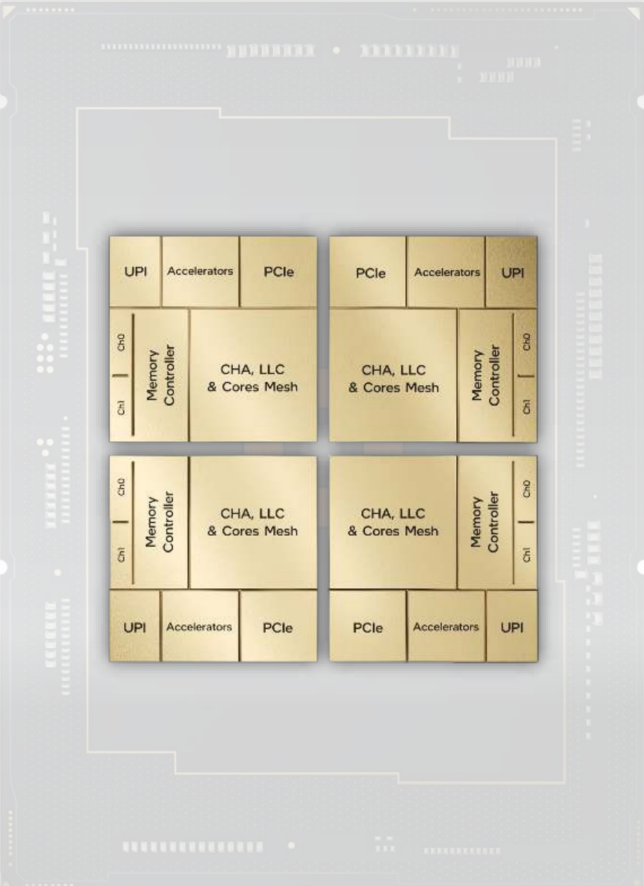

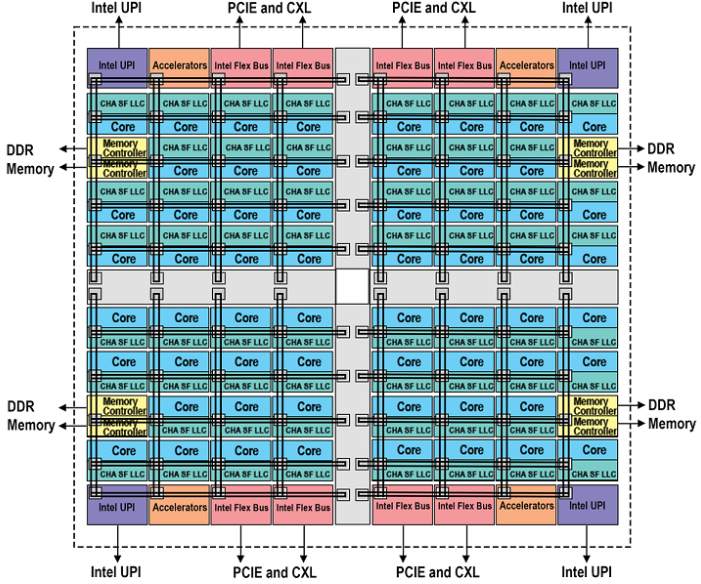

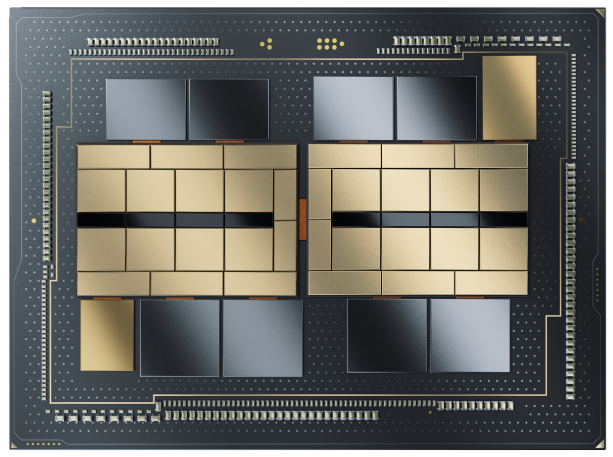

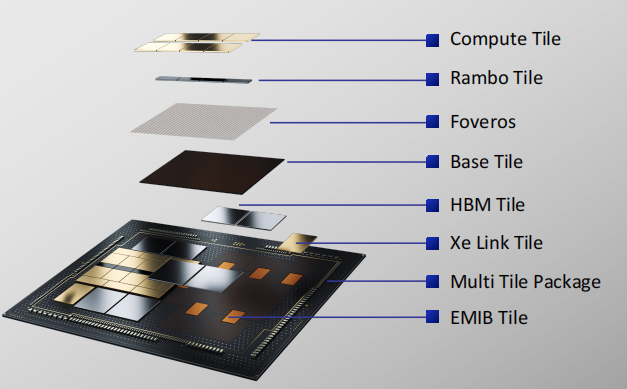

Sapphire Rapids

- 2023年发布

- Intel 7nm

多Die架构

如图所示[^2]:

单die架构(尚不确定)

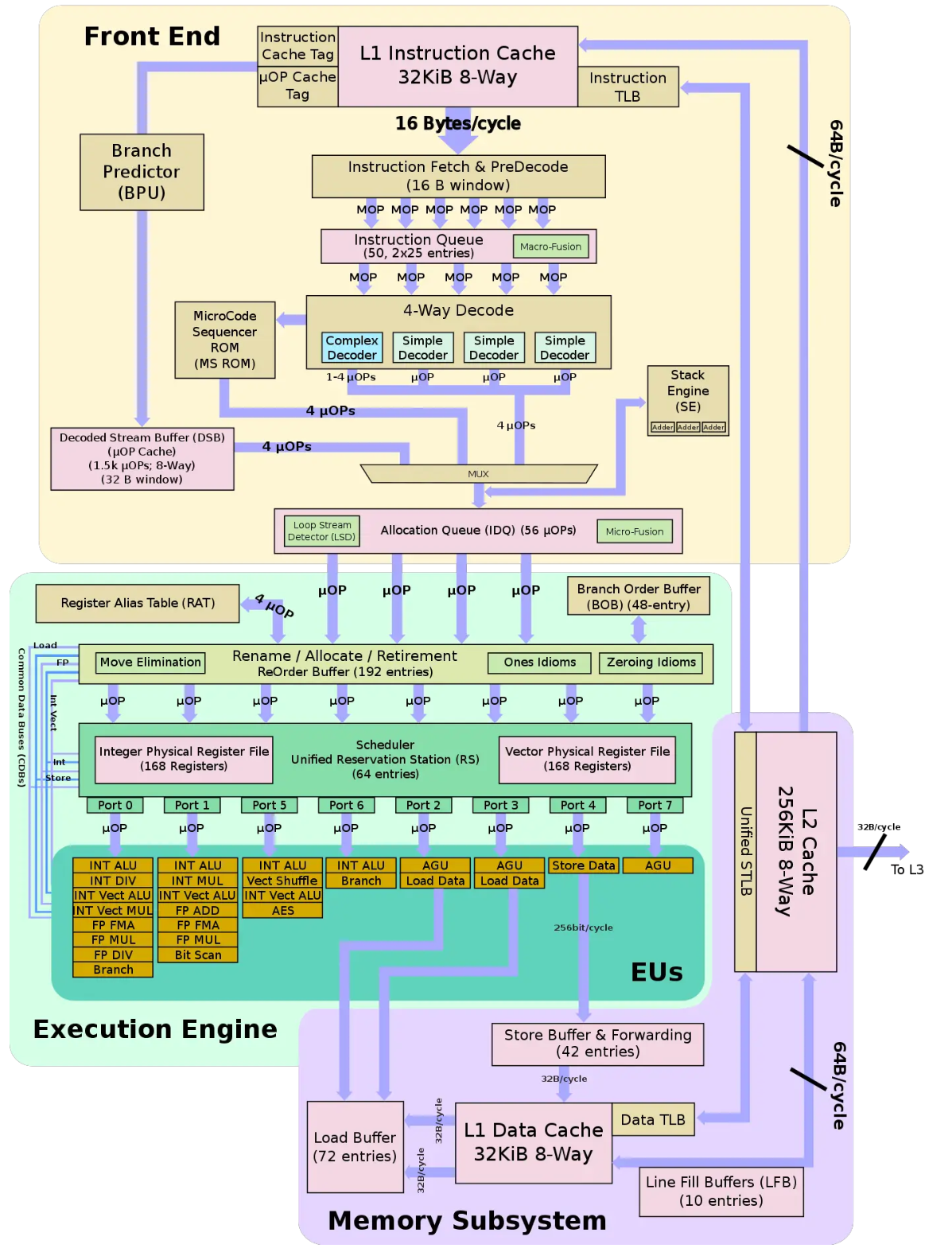

三、CPU Core架构

Broadwell

Sunny Cove

最早于2020年HOT会议上随Icelake服务器CPU一同发布3。

四、AI加速器架构

Ponte Vecchio

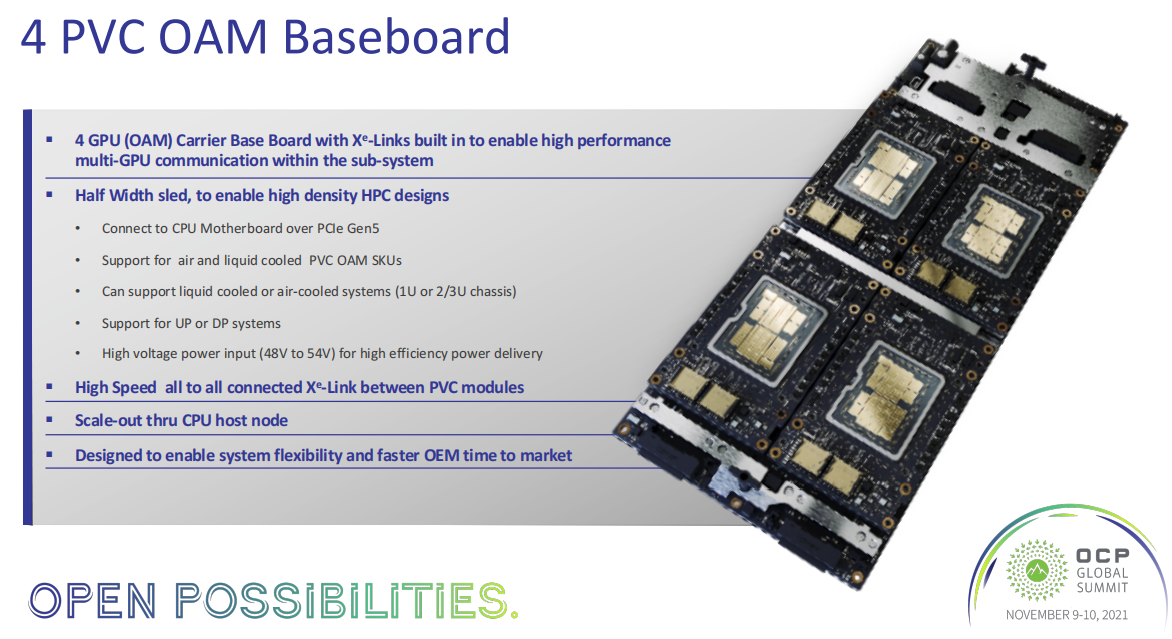

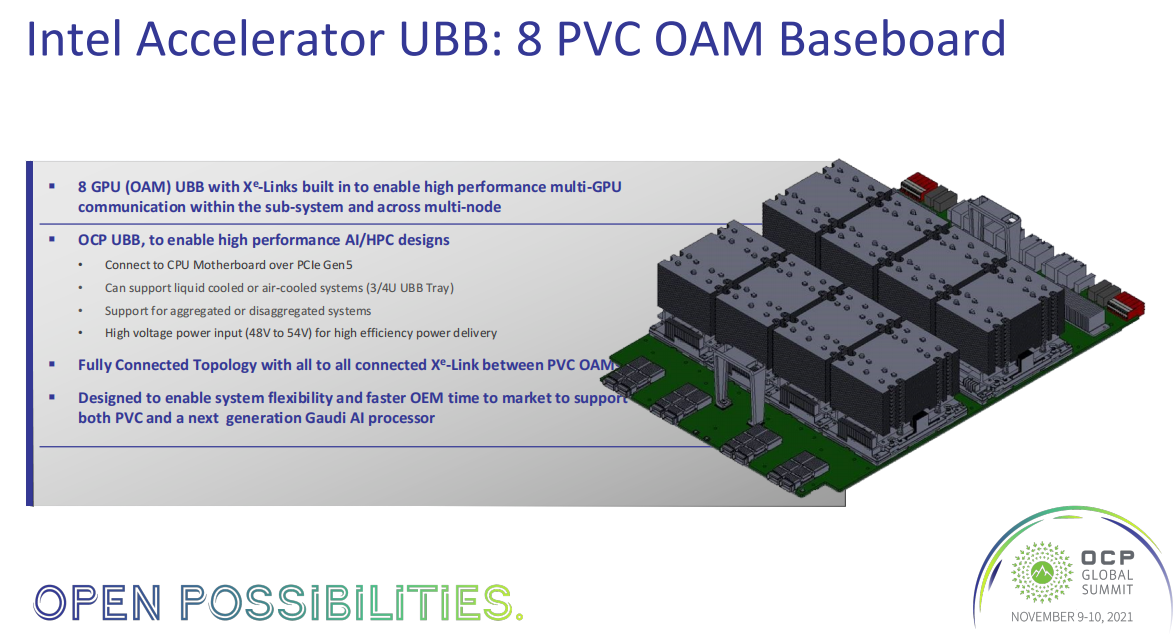

2021年Intel发布了面向OAM的通用计算加速器Ponte Vecchio。

-

45 TFLOPS @FP32

- cache 带宽 > 50 TBps

- 高速Serdes通信协议XeLink,通信带宽 > 8Tbps

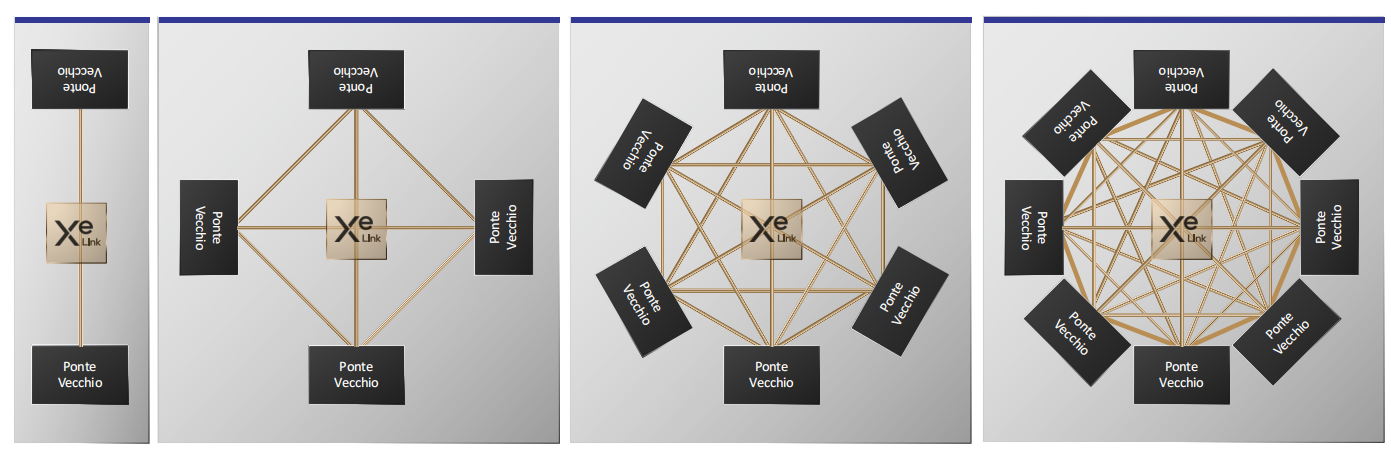

灵活的Chiplet设计

满足一致性的大量加速器组网

四板集成Baseboard

FPGA架构设计

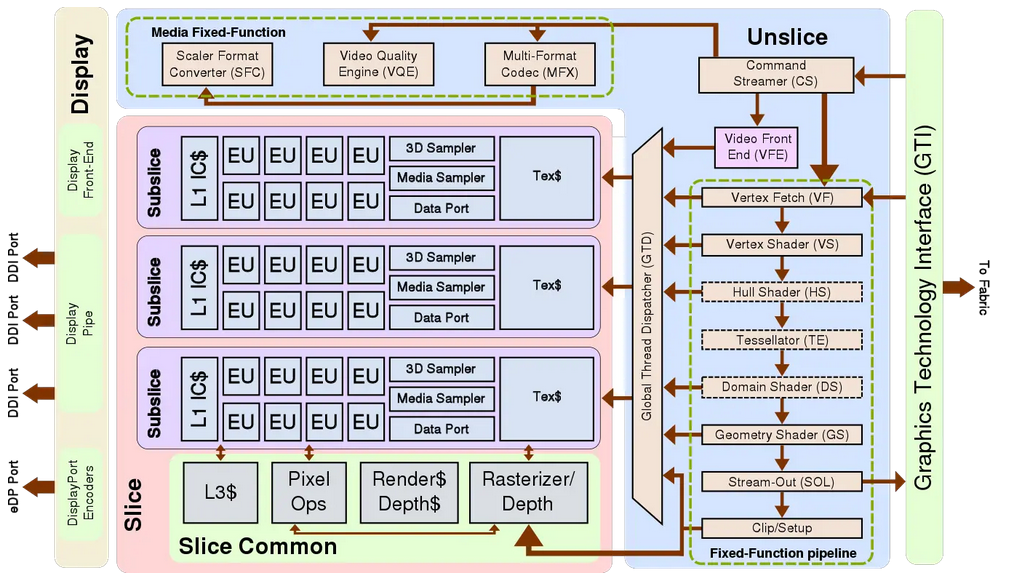

显卡架构

Gen9

- GT2

参考链接

- wikichip: skylake (server)

- A. Biswas, “Sapphire rapids,” in 2021 IEEE Hot Chips 33 Symposium (HCS). IEEE Computer Society, 2021, pp. 1–22.

- New 3rd Gen Intel® Xeon® Scalable Processor (Codename: Ice Lake-SP)

- 知乎:Alder Lake深度解析:Intel的大小核未来梦

747

747

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?