1.硬件资源

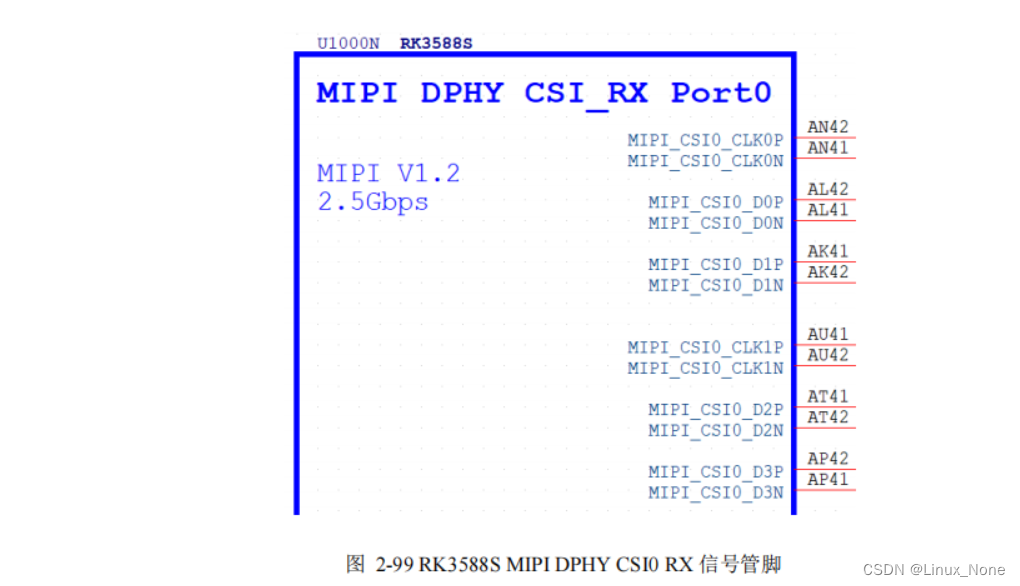

1.1 MIPI DPHY CSI RX 接口

RK3588S 有 1 个 MIPI DPHY CSI RX,都支持 MIPI V1.2 版本,每个通道最大数据传输速率为2.5Gbps。

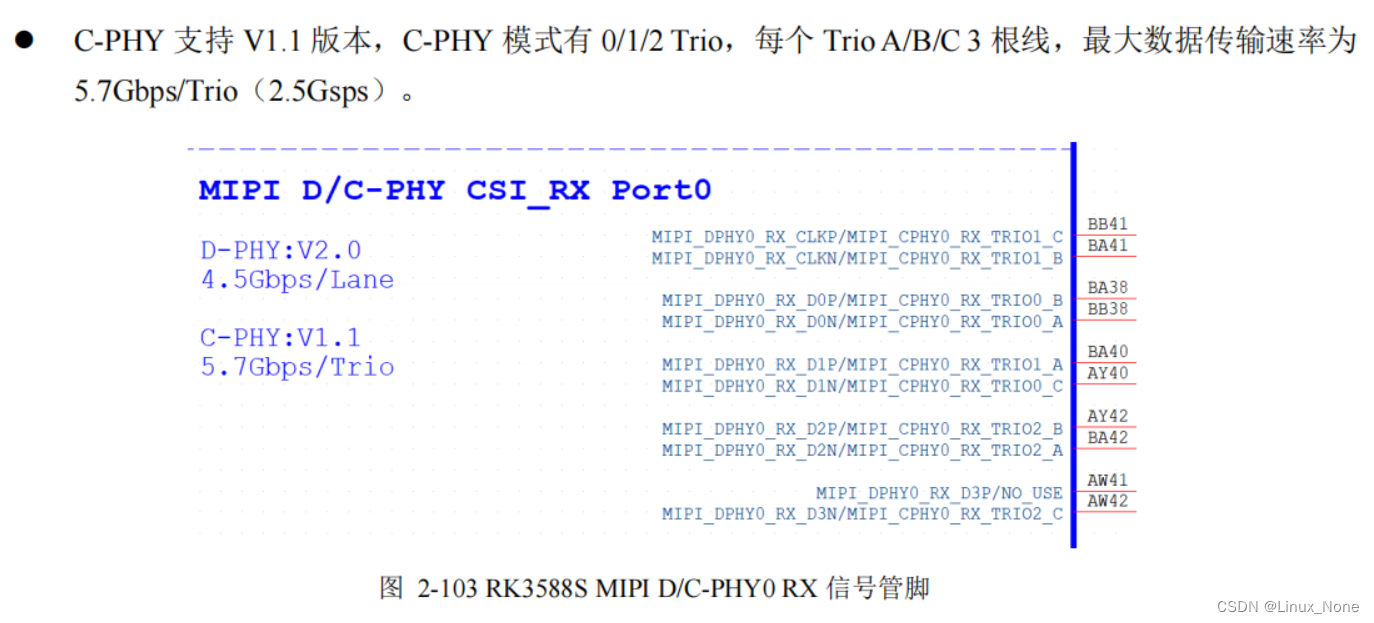

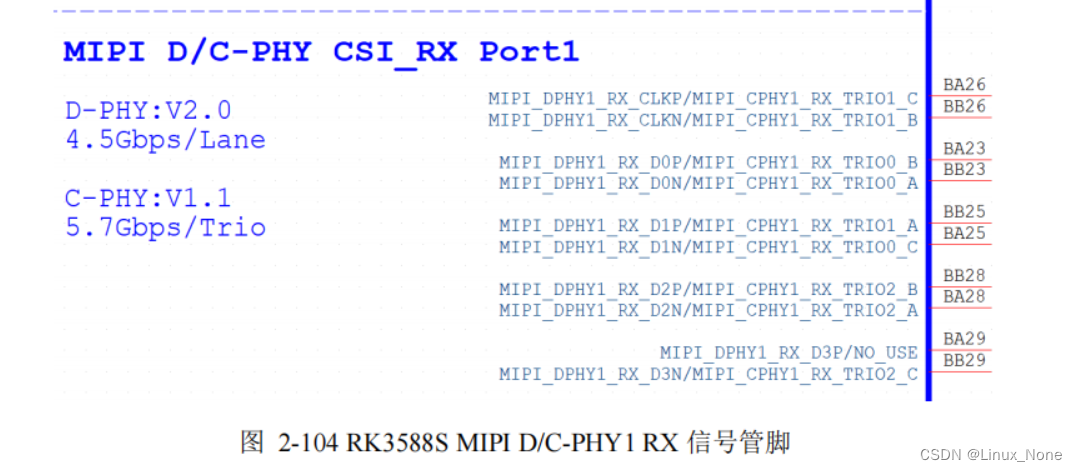

1.2 MIPI_D/CPHY_RX 接口

RK3588S 有两个 MIPI D-PHY/C-PHY CSI RX Combo 的 PHY,支持 V1.2 版本,D-PHY 模式有 0/1/2/3

Lane,每个 Lane 2 根线,最高传输速率 2.5Gbps/Lane;

- 建议使用 1 Lane or 2Lane 模式。

- 不支持 Skew calibration 功能,mipi bitrate >= 1.5Gbps/lane 的情况下,PCB 对于各 data lane 与 clk lane 之间的 skew 影响需要考虑更严格。

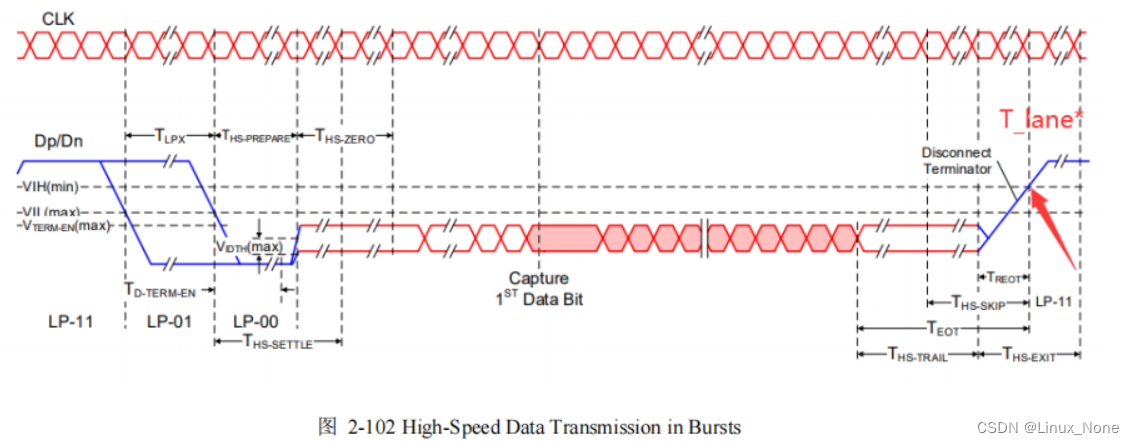

- 非必要时不建议使用 4Lane 模式,若一定要使用,对 Camera 的时序有严格要求,必须满足以下条件:

T_lane0 = T_lane1 = T_lane2 = T_lane3 或者(T_lane0 = T_lane1)> = (T_lane2 = T_lane3)

T_lane*以下图中箭头处时间点为参考:

2.实际分析

使用2个sensor, 下面是我的硬件原理图

使用的split mode: 拆分成2个phy使用,分别为csi2_dphy1(使用0/1 lane)、csi2_dphy2(使用2/3 lane),

使用的split mode: 拆分成2个phy使用,分别为csi2_dphy1(使用0/1 lane)、csi2_dphy2(使用2/3 lane),

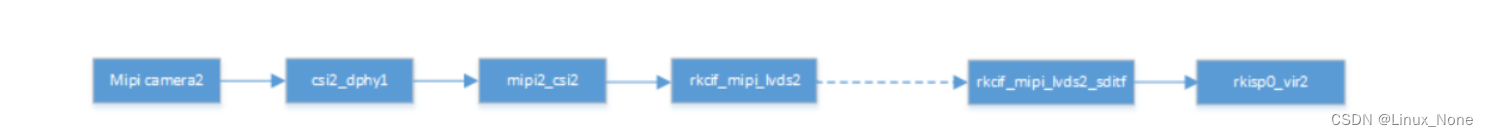

所以链路如图所示

所以链路如图所示

dphy0_hw的设备树参考:

#ifndef RP_CAMERA_XS9922B

/{

vcc_camera: vcc-camera-regulator {

compatible = "regulator-fixed";

gpio = <&gpio4 RK_PB0 GPIO_ACTIVE_HIGH>;

pinctrl-names = "default";

pinctrl-0 = <&camera_pwr>;

regulator-name = "vcc_camera";

enable-active-high;

regulator-always-on;

regulator-boot-on;

};

};

&pinctrl {

camera_pwr: camera-pwr {

rockchip,pins =

/* camera power en */

<4 RK_PB0 3 &pcfg_pull_down>;

};

};

#endif

&i2c3 {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&i2c3m1_xfer>;

imx415_2: imx415_2@1a {

compatible = "sony,imx415";

status = "okay";

reg = <0x1a>;

clocks = <&cru CLK_CIFOUT_OUT>;

clock-names = "xvclk";

power-domains = <&power RK3588_PD_VI>;

pinctrl-names = "default";

pinctrl-0 = <&cif_clk>;

rockchip,grf = <&sys_grf>;

pwdn-gpios = <&gpio1 RK_PC1 GPIO_ACTIVE_HIGH>;

reset-gpios = <&gpio0 RK_PB0 GPIO_ACTIVE_LOW>;

rockchip,camera-module-index = <0>;

rockchip,camera-module-facing = "BACK";

rockchip,camera-module-name = "CMK-OT2022-PX1";

rockchip,camera-module-lens-name = "IR0147-50IRC-8M-F20";

port

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4300

4300

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?