通过Vivado在IP Catalog选择MIPI CSI-2 Rx Subsystem IP。

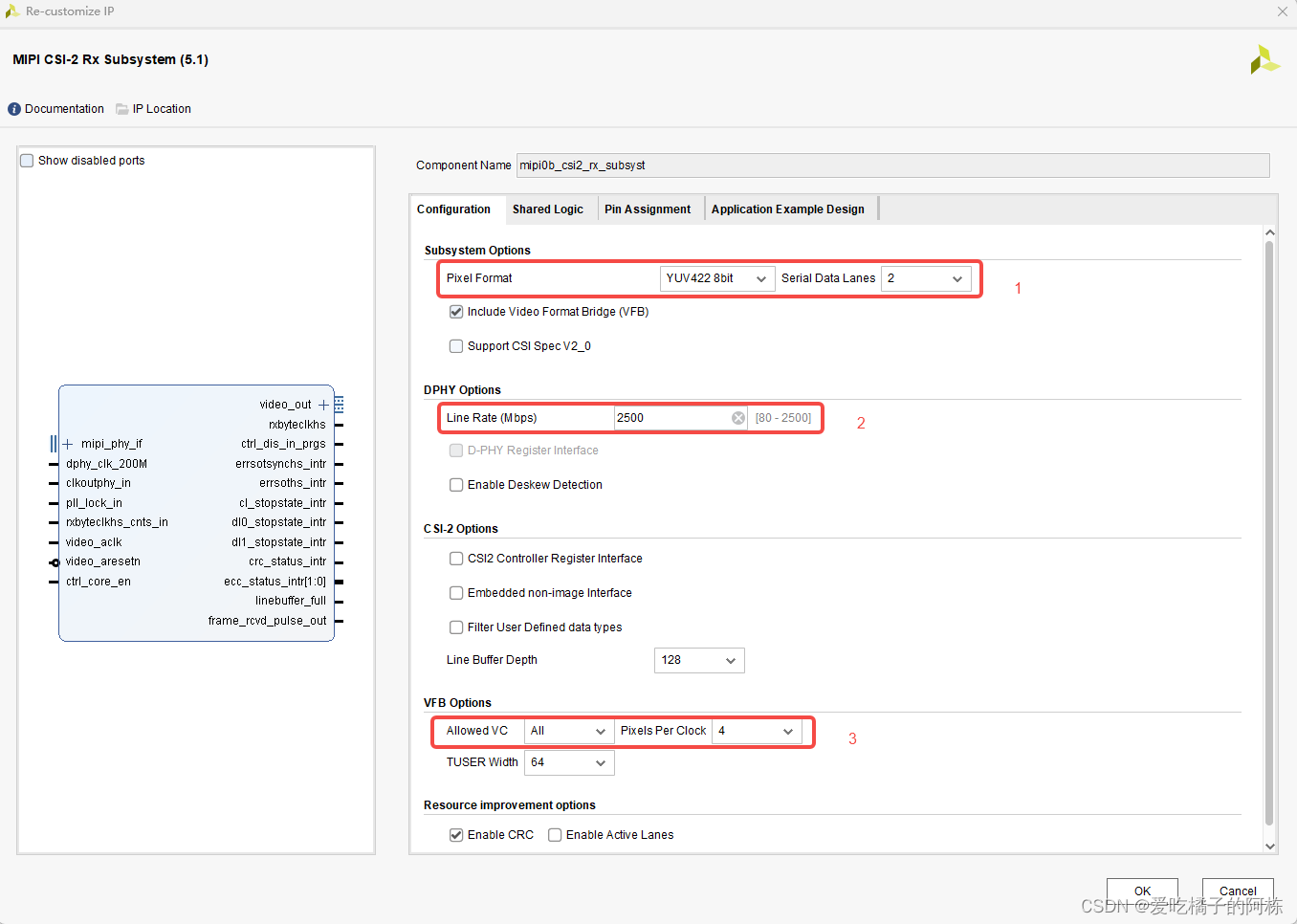

GUI中First Tab配置如下信息,

①配置图像格式及MIPI LANE数量。

②配置MIPI线速率。

③配置允许通过的虚拟通道号和每个时钟周期输出的像素数量。

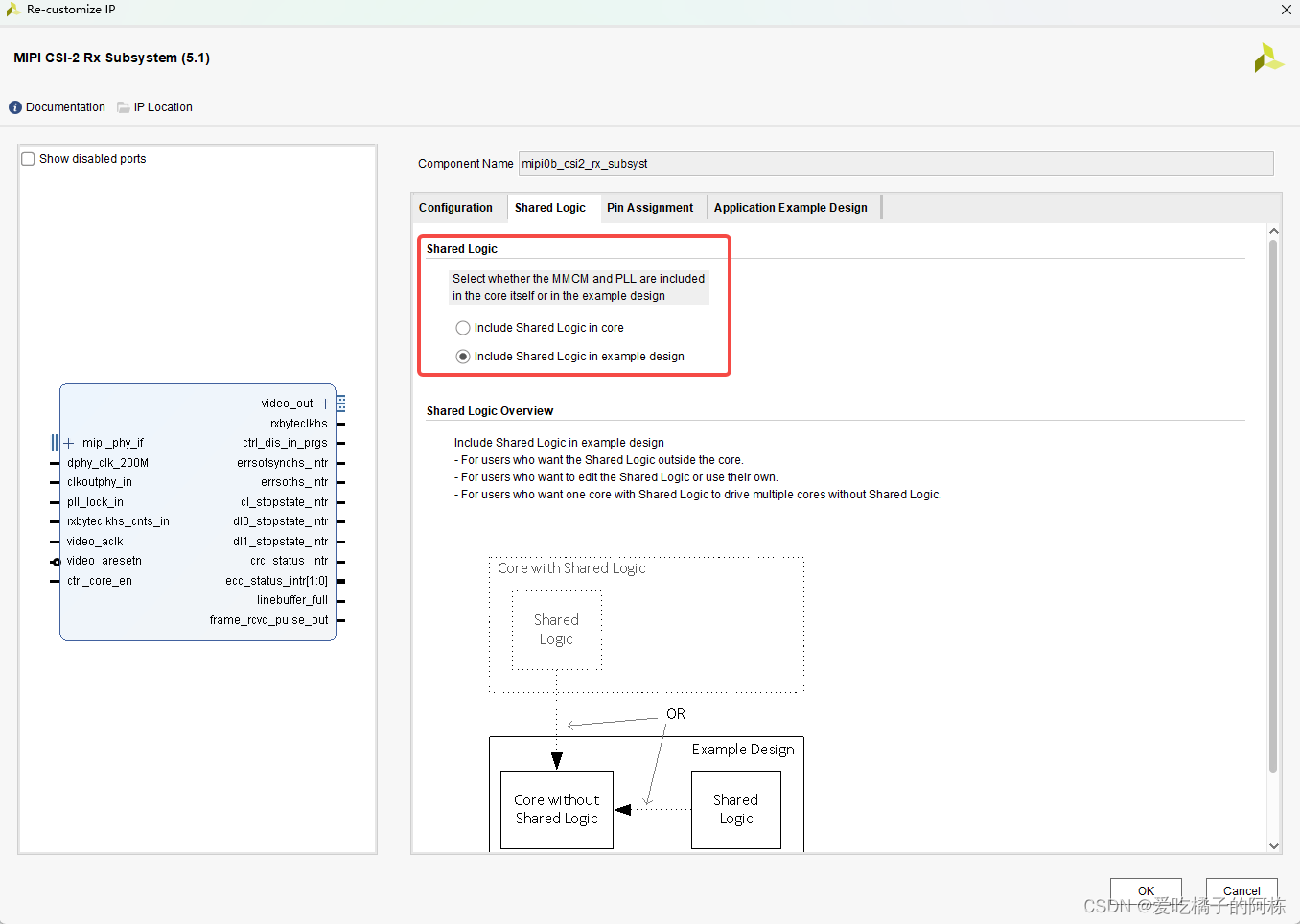

Second Tab配置IP时钟资源的来源,第一个选项表示在IP核内部生成时钟供IP使用(会消耗PLL/MMCM),第二个选项表示IP核使用其他MIPI RX IP输出的时钟(不会额外消耗时钟资源)。所以MIPI RX IP核有Master和Slave的概念,Master MIPI RX IP通过PLL/MMCM在内部生成时钟,该时钟可以提供给其他Slave MIPI RX IP使用。

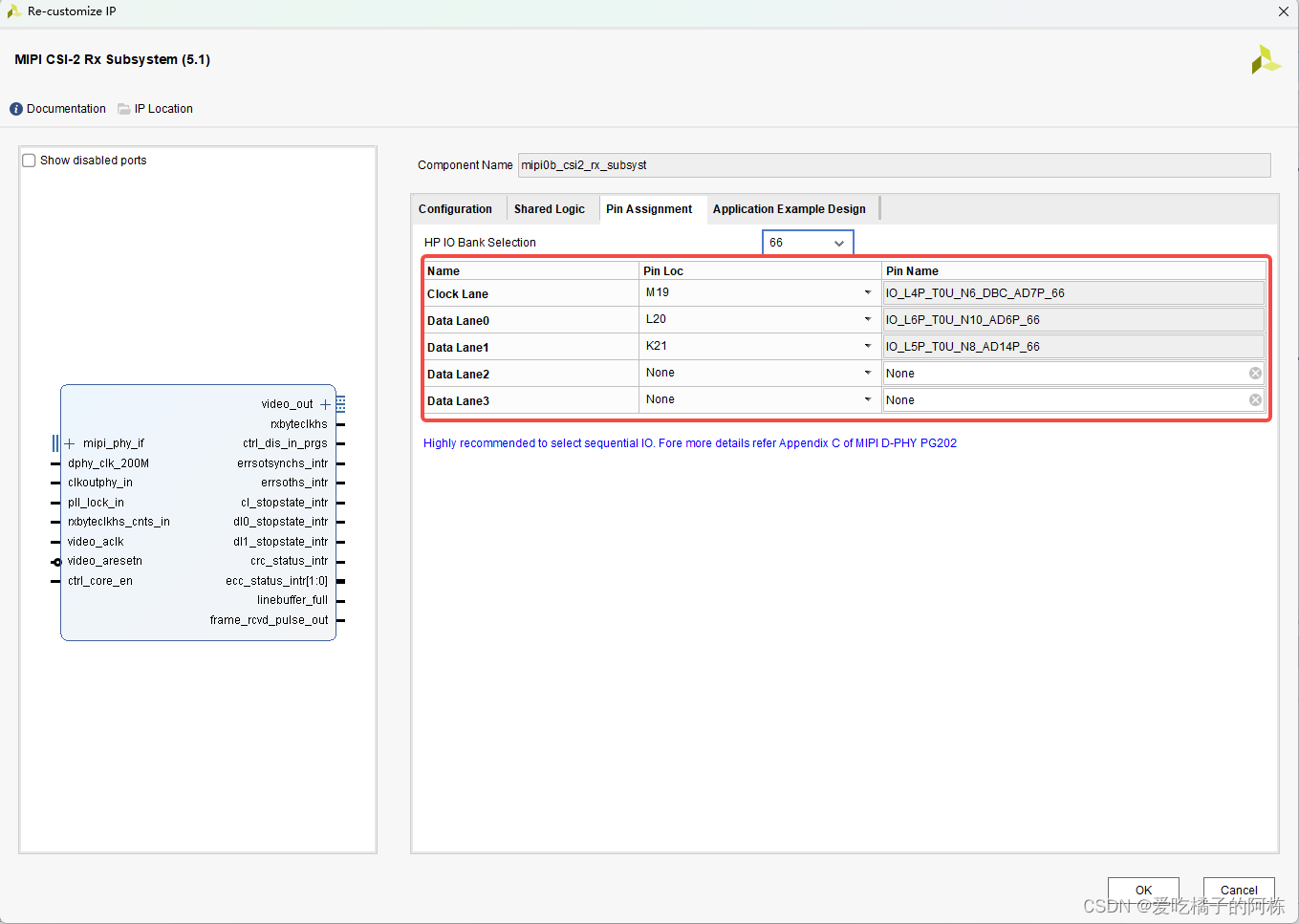

Third Tab即对MIPI管脚进行物理约束。

4936

4936

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?