BRAM写模式一共有三种,分别是write_first、read_first和no_change。

对于BRAM的一个端口,以PORTA为例,一般会有CLKA PORTA 时钟信号、WEA PORTA写使能信号、DINA PORTA写数据、ADDRA PORTA读写地址、DOUTA PORTA读输出 以及 ENA PORTA使能。

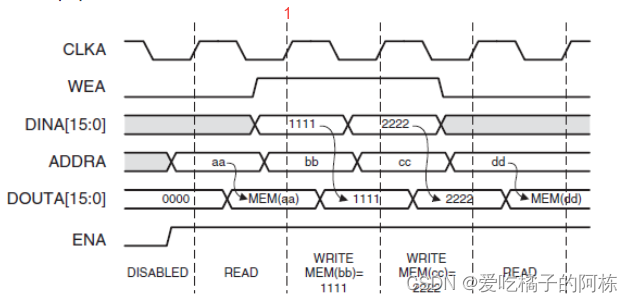

WRITE_FIRST MODE

对于write_first模式,BRAM在时钟上升沿1准备将数据16‘h1111写到地址8’hbb处,在Delay不到1个时钟周期的时间后,DOUTA变为了16'h1111,所以在时钟上升沿1,BRAM同时进行了对地址8’hbb的写操作和读操作,且读出的值为最新写入的值也就是16‘h1111。

用verilog来描述上述行为(CSDN为什么没有verilog格式!!):

always @(posedge clka) begin

if(ena) begin

if(wea) begin

BRAM[addra] <= dina;

douta <= dina;

end

else begin

douta <= BRAM[addra];

end

end

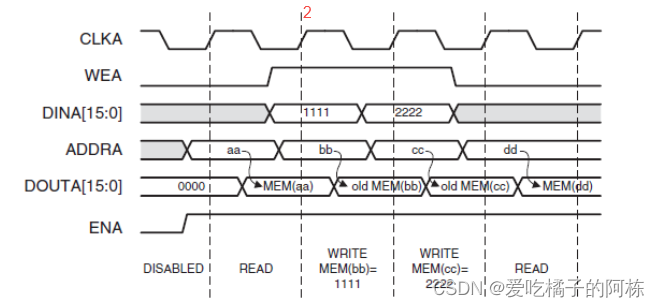

endREAD_FIRST MODE

对于read_first模式,BRAM在时钟上升沿2准备将数据16‘h1111写到地址8’hbb处,在Delay不到1个时钟周期的时间后,DOUTA变为了old MEM(bb),即地址8'hbb的旧值,所以在时钟上升沿2,BRAM同时进行了对地址8’hbb的写操作和读操作,但读出的值为先前的旧值而非最新的16'h1111。

用verilog来描述上述行为:

always @(posedge clka) begin

if(ena) begin

if(wea) begin

BRAM[addra] <= dina;

douta <= BRAM[addra];

end

else begin

douta <= BRAM[addra];

end

end

endNO_CHANGE MODE

对于no_change模式,WEA和ENA都为高时,BRAM在时钟上升沿3准备将数据16‘h1111写到地址8’hbb处,DOUTA没有变化,所以在时钟上升沿3,BRAM仅对地址8’hbb进行了写操作,只有当WEA拉低时才会进行读操作,即WEA高为写低为读。

用verilog来描述上述行为:

always @(posedge clka) begin

if(ena) begin

if(wea) BRAM[addra] <= dina;

else douta <= BRAM[addra];

end

end总结

1. write_first mode,wea拉高时,BRAM会同时执行读写操作,读出来的值为最新写入的值。

2. read_fisrt mode,wea拉高时,BRAM会同时执行读写操作,读出来的值为未更新的旧值。

3. no_change mode, wea拉高时, BRAM只会执行写操作,wea拉低时,BRAM才执行读操作。

3378

3378

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?