引言

卷积码是一种信道纠错编码,在通信中具有广泛的应用。在发送端根据生成多项式进行卷积码编码,在接收端根据维特比(Viterbi)译码算法进行译码,能够有效抵抗信道噪声的影响,在误码率门限之下可以对传输过程中发生的突发错误进行纠错。

1、编码及译码算法的基本原理

- 卷积码编码

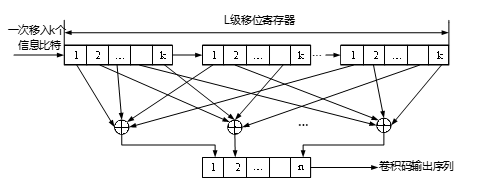

卷积码是一种纠错编码,它将输入的k个信息比特编成n个比特输出,特别适合以串行形式进行传输,时延小。卷积码编码器的一般形式如下图所示。

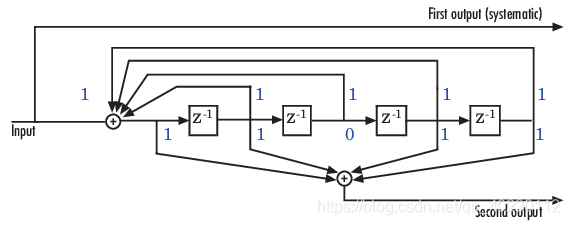

如下图所示为k=1时的编码框图,k=1也是最常用的一种编码器情形:

- 译码算法

卷积码的译码方法有两类:一类是大数逻辑译码,又称门限译码;另一类是概率译码,概率译码又能分为维特比译码和序列译码两种。维特比(Viterbi)译码和序列译码都属于概率译码。当卷积码的约束长度不太大时,与序列译码相比,维特比译码器比较简单,计算速度更快。接下来的译码算法采用的是概率译码中的维特比译码。采用概率译码的一种基本想法是:把已接收序列与所有可能的发送序列做比较,选择其中汉明码距最小的一个序列做为发送序列。

- 编码及译码算法的Matlab实现

根据如上所述的编译码基本原理,我们可以在Matlab中进行很方便的仿真,Matlab提供了集成化的函数可供调用,进行仿真,如下所示:

% 0101随机数,待编码数据

bits = randi([0 1],256,1);

% trellis = poly2trellis(7,{'1 + x^3 + x^4 + x^5 + x^6', ...

% '1 + x + x^3 + x^4 + x^6'})

% 产生生成

本文介绍了卷积码编码和维特比译码的基本原理,卷积码用于信道纠错编码,通过Matlab仿真了编码和译码过程。同时,详细阐述了卷积码编码的FPGA实现,以及如何利用Vivado的Viterbi decoder IP核实现维特比译码,并提供了输入输出数据格式和IP核配置流程。

本文介绍了卷积码编码和维特比译码的基本原理,卷积码用于信道纠错编码,通过Matlab仿真了编码和译码过程。同时,详细阐述了卷积码编码的FPGA实现,以及如何利用Vivado的Viterbi decoder IP核实现维特比译码,并提供了输入输出数据格式和IP核配置流程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7622

7622

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?