本章目录:

1. CISC/RISC

CISC 是复杂指令系统计算机(Complex Instruction Set Computer)的简称,微处理器是台式计算机系统的基本处理部件,每个微处理器的核心是运行指令的电路。指令由完成任务的多个步骤所组成,把数值传送进寄存器或进行相加运算。

RISC(reduced instruction set computer,精简指令集计算机)是一种执行较少类型计算机指令的微处理器,起源于 80 年代的 MIPS 主机(即 RISC 机),RISC 机中采用的微处理器统称 RISC 处理器。这样一来,它能够以更快的速度执行操作(每秒执行更多百万条指令,即MIPS)。因为计算机执行每个指令类型都需要额外的晶体管和电路元件,计算机指令集越大就会使微处理器更复杂,执行操作也会更慢。

2. 冯诺依曼架构/哈佛架构

冯诺依曼架构,也叫普林斯顿架构,其特点是程序空间和数据空间是一体的,数据和程序采用同一数据总线和地址总线。指令和数据地址指向同一个存储器的不同物理位置,指令和数据的宽度相同。由于冯诺依曼架构的指令和数据储存在同一存储器,而且由同一总线进行读写,因而指令和数不能同时进行操作,只能顺序执行。也是这个原因限制了计算机的性能和数据处理速度。采用冯诺依曼架构的优点是硬件简单,最典型的应用便是 intel 的 x86 微处理器。冯诺依曼架构芯片采用的是复杂指令集(CISC)。

哈佛架构,其特点则是数据和程序分别存放,存储器分为数据存储器和程序存储器,同时,总线则分为程序存储器的数据总线和地址总线以及数据存储器的数据总线和地址总线。这种总线方式也为同时对数据和程序进行操作提供了可能,因而哈佛结构具有较高的执行效率。同时,由于指令和数据分开存放,因而指令和数据可以有不同的宽度。目前,采用哈佛架构的芯片以 DSP 和 ARM 为代表。哈佛架构芯片采用的是精简指令集(RISC)。

3. 时间局部性/空间局部性

3.1 时间局部性

时间局部性是指被引用过一次的内存位置很可能在不远的将来再被多次引用。

3.2 空间局部性

空间局部性是指如果一个内存位置被引用了一次,那么程序很可能在不远的将来引用其附近的一个内存位置。

3.3 局部性原理举例

在硬件层,局部性原理允许计算机设计者通过引入小而快的高速缓存存储器来保存最近被引用的指令和数据项,从而提高对主存的访问速度。在操作系统级,局部性原理允许系统使用主存作为虚拟地址空间最近被引用块的高速缓存。类似的,操作系统用主存来缓存磁盘文件系统中最近被使用的磁盘块。在应用程序的设计,如 Web 浏览器将最近被请求的文档放在本地磁盘上,利用的就是时间局部性。大容量的 Web 服务器将最近被请求的文档放在前端磁盘高速缓存中,不需要服务器的干预就可满足对这些文档的请求。

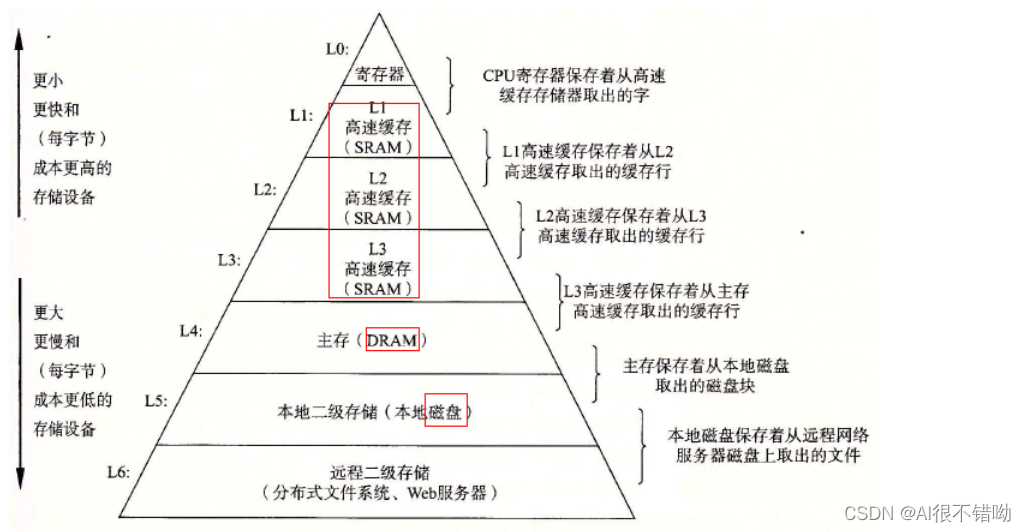

4. 计算机存储结构

5. RAM/SRAM/DRAM/SDRAM/DDR

5.1 RAM

RAM(Random Access Memory,随机存储器),存储单元的内容可按需随意取出或存入,且存取的速度与存储单元的位置无关的存储器。这种存储器在断电时将丢失其存储内容,故主要用于存储短时间使用的程序。

5.2 SRAM

SRAM(Static Random Access Memory,静态随机存取存储器),因此只要供电它就会保持一个值。一般而言,SRAM 比DRAM 要快,这是因为SRAM 没有刷新周期。每个 SRAM 存储单元由 6 个晶体管组成,而DRAM 存储单元由一个晶体管和一个电容器组成。相比而言,DRAM 比 SRAM 每个存储单元的成本要高。照此推理,可以断定在给定的固定区域内 DRAM 的密度比 SRAM 的密度要大。

5.3 DRAM

DRAM (Dynamic Random Access Memory,动态随机存储器),这是一种以电荷形式进行存储的半导体存储器。DRAM中的每个存储单元由一个晶体管和一个电容器组成。数据存储在电容器中。电容器会由于漏电而导致电荷丢失,因而 DRAM 器件是不稳定的。为了将数据保存在存储器中,DRAM 器件必须有规律地进行刷新。

SRAM 常常用于高速缓冲存储器,因为它有更高的速率;而 DRAM 常常用于 PC 中的主存储器,因为其拥有更高的密度。

5.4 SDRAM

SDRAM (Synchronous Dynamic Random Access Memory,同步动态随机存取存储器),意思是指理论上其速度可达到与 CPU 同步。

5.5 DDR

DDR SDRAM(Dual Date Rate SDRAM):简称 DDR,也就是“双倍速率 SDRAM“的意思。

DDR 可以说是 SDRAM 的升级版本,DDR 在时钟信号上升沿与下降沿各传输一次数据,这使得 DDR 的数据传输速度为传统 SDRAM 的两倍。

5.6 比较以上的不同

-

ROM和RAM指的都是半导体存储器,ROM在系统停止供电的时候仍然可以保持数据,而RAM通常都是在掉电之后就丢失数据。

-

RAM分为两大类:SRAM和DRAM。

SRAM为静态RAM(Static RAM/SRAM),SRAM速度非常快,是目前读写最快的存储设备,但是它也非常昂贵,所以只在要求很苛刻的地方使用,譬如CPU的一级缓冲,二级缓冲。

DRAM为动态RAM(Dynamic RAM/DRAM),DRAM保留数据的时间很短,速度也比SRAM慢,不过它还是比任何的ROM都要快,但从价格上来说DRAM相比SRAM要便宜很多,计算机内存就是DRAM的。RAM价格相比ROM和FLASH要高。

- LASH存储器又称闪存,它结合了ROM和RAM的长处,不仅具备电子可擦除可编程(EEPROM)的性能,还不会断电丢失数据同时可以快速读取数据(NVRAM的优势),U盘和MP3里用的就是这种存储器。

声明

本人所有系列的文章,仅供学习,不可商用,如有侵权,请告知,立删!!!

本人主要是记录学习过程,以供自己回头复习,再就是提供给后人参考,不喜勿喷!!!

如果觉得对你有用的话,记得点赞+收藏+评论!!!

全网各平台同名===> “IC二舅”

下一期如果有大家想看的或者哪块不懂想学习的,可以私聊或在群里提问都可以,“二舅”肯定是知无不言言无不尽!!!

“二舅”博客: https://blog.csdn.net/qq_40549426?spm=1019.2139.3001.5343

二舅"公众号": “IC二舅”

“二舅”精神内耗学习群:878501676

325

325

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?