1. 什么是分频

分频就是生成一个新时钟,该新时钟的频率是原有时钟频率的整数分之一倍,新周期是原有周期的整数倍。再简单来说,让你手撕一个四分频电路,就是写代码生成一个周期是原来四倍的时钟,如果手撕一个三分频电路,就是写代码生成一个周期是原来三倍的时钟。但是奇数分频会比偶数分频复杂一些。

2. 偶数分频

2.1 怎么实现二分频呢?

检测参考时钟,每一个上升沿到来时,新的时钟翻转一次。

2.2 代码实现:

module div_2(

input clk,

input rst_n,

output reg clk_out

);

parameter n_div = 2;

reg [2:0] cnt;

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

clk_out <= 1'b0;

cnt <= 3'b0;

end

else begin

if(cnt == n_div/2 - 1) begin

clk_out <= ~clk_out;

cnt <= 3'b0;

end

else begin

cnt <= cnt + 1'b1;

end

end

end

endmodule

2.3 testbench文件

`timescale 1 ns/ 1 ps

module div_2_tb();

reg clk;

reg rst_n;

// wires

wire clk_out;

div_2 i1 (

.clk(clk),

.clk_out(clk_out),

.rst_n(rst_n)

);

initial

begin

clk <= 0;

rst_n <= 1;

#50

rst_n <= 0;

#50

rst_n <= 1;

#50000;

$stop;

end

always

begin

#10 clk = ~clk;

end

endmodule

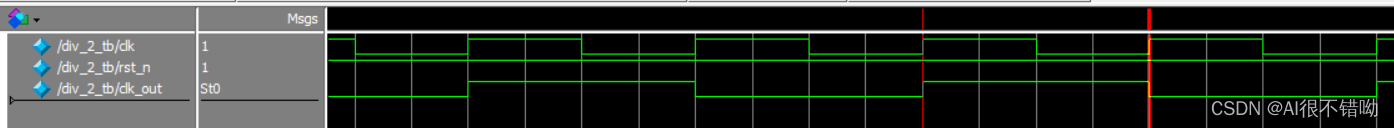

2.4 仿真波形

搞定!从图中可以看到,clk_out每过两个clk时钟上升沿就flip-flop一次,这样一个clk_out的周期就是clk周期的两倍,也即实现了二分频。

那如果是任意偶数分频呢,这就得数经过了多少上升沿,如果是四分频,那就每过两个时钟上升沿(两周期),新信号flip-flop一次,flip-flop两次为新信号的一个周期,即是周期是原时钟的四倍。同理,8分频就是每数4个上升沿,flip-flop一次,以此类推,可以实现任意偶数分频了。

2.5 笔试面试变式题

占空比分析:我们上面写的任意偶数分频代码的占空比都是50%,实际上面试手撕代码不会让你50%占空比,那怎么办?

答:进行计数,对于一个八分频,开始就把时钟设为高电平,我用cnt 计数到两个时钟上升沿后再把它拉低,计数到7后cnt 拉低 时钟拉高,这样就实现了两个周期高,六个周期低,占空比为2/8 即 25% 的八分频。

参考文献:分频器

3. 奇数分频(除了1分频)

怎么写一个三分频呢?一个占空比不是50%的三分频是好写的,同样利用一个cnt变量对上升沿计数来实现。比如实现占空比为1/3的三分频,那么只要数一个上升沿,输出高电平,数两个上升沿输出低电平就能解决。

3.1 代码实现(3分频,非50%占空比)

module odd_div (

input clk,

input rst_n,

output reg clk_out,

output reg [1:0] cnt

);

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

clk_out <= 1'b0;

cnt <= 2'b00;

end

else begin

if(cnt == 0) begin

clk_out <= 1'b0;

cnt <= cnt + 1'b1;

end

else if(cnt == 2) begin

clk_out <= 1'b1;

cnt <= 2'b00;

end

else begin

cnt <= cnt + 1'b1;

end

end

end

endmodule

3.2 testbench文件

`timescale 1ns/1ps

module odd_div3_tb ();

reg clk;

reg rst_n;

wire clk_out;

wire [1:0] cnt;

initial begin

clk <= 0;

rst_n <= 1;

#50

rst_n <= 0;

#50

rst_n <= 1;

#1000

$stop;

end

always begin

#10 clk = ~clk;

end

odd_div div3 (

.clk(clk),

.rst_n(rst_n),

.clk_out(clk_out),

.cnt(cnt)

);

endmodule

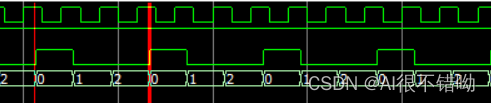

3.3 仿真

这里抛出一个小问题,3分频之后为什么有延时呢?

我觉得应该是我用的门级仿真,所以会有一定的延时存在。

3.4 那么如何实现一个占空比50%的三分频呢?

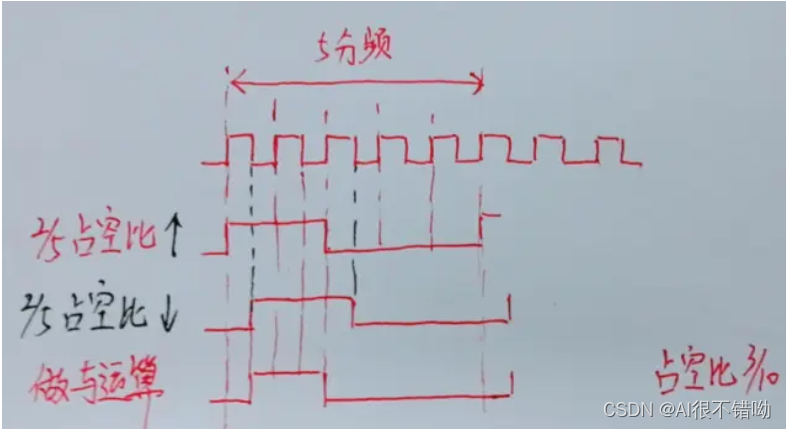

答:将一个占空比1/3 上升沿采样的三分频和一个占空比1/3下降沿采样的三分频结果,做或运算。

什么意思?怎么想到这样做的?下面来解答!

任何奇数 2N-1 (除1分频外)分频都可以表示由 N-1个高电平周期和 N个低电平周期组成。(占空比最接近50%,但小于50%)

写两个这样的分频器,一个上升沿采样的分频器——div1,一个下降沿采样的分频器——div2,在相同 cnt 判断切换高低电平的条件下,就一定有 div1 领先(或滞后)于 div2 半个参考周期,这样他们相或后会使得新的结果还是 2N-1 分频,但是高电平周期变为 N-1+1/2=N-1/2,低电平周期变为 N-1/2,从而高低电平持续时间相等,实现50%占空比的任意奇数分频器。

3.4.1 代码实现(以50%占空比的七分频举例)

module odd_div7_half (

input clk,

input rst_n,

output reg [2:0] cnt1,

output reg [2:0] cnt2,

output reg clk_out1,

output reg clk_out2,

output clk_out

);

localparam div_cnt = 7;

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

clk_out1 <= 1'b0;

cnt1 <= 3'b000;

end

else begin

if(cnt1 == (div_cnt-1)/2) begin

clk_out1 <= 1'b1;

cnt1 <= cnt1 + 1;

end

else if(cnt1 == div_cnt-1) begin

clk_out1 <= 1'b0;

cnt1 <= 3'b000;

end

else begin

cnt1 <= cnt1 + 1;

end

end

end

always @ (negedge clk or negedge rst_n) begin

if(!rst_n) begin

clk_out2 <= 1'b0;

cnt2 <= 3'b000;

end

else begin

if(cnt2 == (div_cnt-1)/2) begin

clk_out2 <= 1'b1;

cnt2 <= cnt2 + 1;

end

else if(cnt2 == div_cnt-1) begin

clk_out2 <= 1'b0;

cnt2 <= 3'b000;

end

else begin

cnt2 <= cnt2 + 1;

end

end

end

assign clk_out = clk_out1 | clk_out2;

endmodule

3.4.2 testbench文件

`timescale 1ns/1ps

module div7_half_tb();

reg clk;

reg rst_n;

wire [2:0] cnt1;

wire [2:0] cnt2;

wire clk_out1;

wire clk_out2;

wire clk_out;

initial begin

clk <= 0;

rst_n <= 1;

#50

rst_n <= 0;

#50

rst_n <= 1;

#1000

$stop;

end

always begin

#10 clk = ~clk;

end

odd_div7_half u0(

.clk(clk),

.rst_n(rst_n),

.cnt1(cnt1),

.cnt2(cnt2),

.clk_out1(clk_out1),

.clk_out2(clk_out2),

.clk_out(clk_out)

);

endmodule

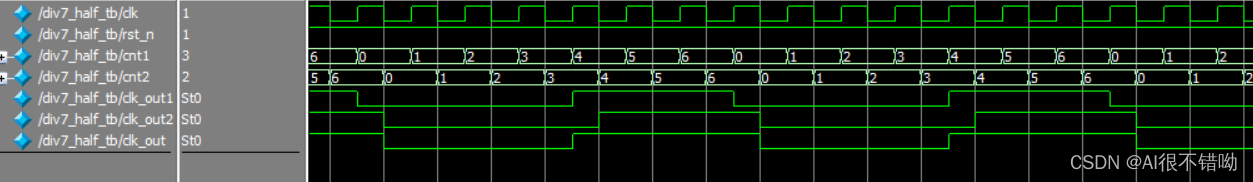

3.4.3 仿真结果

到此,我们就实现了任意50%占空比的奇数分频器,总结一下。说了那么多我们已经可以独立写出任意合理占空比的偶数分频器,以及任意50%占空比的奇数分频器。但是,如果让手撕一个不是50%占空比的奇数分频器怎么办???

到此,我们就实现了任意50%占空比的奇数分频器,总结一下。说了那么多我们已经可以独立写出任意合理占空比的偶数分频器,以及任意50%占空比的奇数分频器。但是,如果让手撕一个不是50%占空比的奇数分频器怎么办???

3.5 如何实现一个非常规占空比的奇数分频器

2022数字IC秋招面经,面试被问了一个非常规占空比的奇数分频器,比如 3/10占空比的五分频, 5/18占空比的九分频?怎么做呢。

这个和上面实现50%任意奇数分频器的原理是类似的,但是采用与运算。用占空比为 2/5 上升沿采样的信号和 2/5占空比下降沿采样的信号相与,这样由于下降沿采样信号滞后上升沿采样信号半个参考周期。

所以相与后,占空比就为 2/5 - 1/10 = 3/10 ,示意图如下:

3.5.1 代码实现

module div5_3to10_half(

input clk,

input rst_n,

output reg clk_out1,

output reg clk_out2,

output clk_out,

output reg [2:0] cnt1,

output reg [2:0] cnt2

);

localparam div_cnt = 5;

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

clk_out1 <= 1'b0;

cnt1 <= 3'b0;

end

else begin

if(cnt1==(div_cnt/2)-1) begin

clk_out1 <= 1'b0;

cnt1 <= cnt1 + 1;

end

else if(cnt1==div_cnt-1) begin

clk_out1 <= 1'b1;

cnt1 <= 3'b0;

end

else begin

cnt1 <= cnt1 + 1;

end

end

end

always @ (negedge clk or negedge rst_n) begin

if(!rst_n) begin

clk_out2 <= 1'b0;

cnt2 <= 3'b0;

end

else begin

if(cnt2==(div_cnt/2)-1) begin

clk_out2 <= 1'b0;

cnt2 <= cnt2 + 1;

end

else if(cnt2==div_cnt-1) begin

clk_out2 <= 1'b1;

cnt2 <= 3'b0;

end

else begin

cnt2 <= cnt2 + 1;

end

end

end

assign clk_out = clk_out1 & clk_out2;

endmodule

3.5.2 testbench文件

`timescale 1ns/1ps

module div_3to10half_tb();

reg clk;

reg rst_n;

wire clk_out1;

wire clk_out2;

wire clk_out;

wire [2:0] cnt1;

wire [2:0] cnt2;

initial begin

clk <= 0;

rst_n <= 1;

#50

rst_n <= 0;

#50

rst_n <= 1;

#10000

$stop;

end

always begin

#10 clk = ~clk;

end

div5_3to10_half u0(

.clk(clk),

.rst_n(rst_n),

.clk_out1(clk_out1),

.clk_out2(clk_out2),

.clk_out(clk_out),

.cnt1(cnt1),

.cnt2(cnt2)

);

endmodule

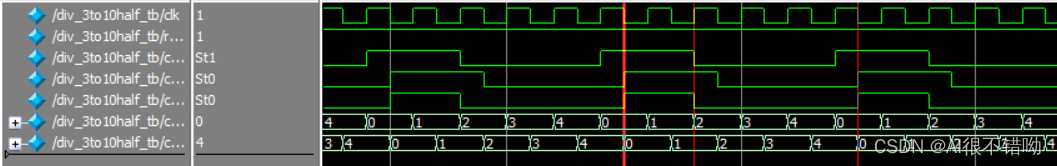

3.5.3 仿真结果

不论之后遇到让你实现什么样子的奇数分频,具体修改只需要改cnt判断数值以及把clk_out 的赋值从clk_out1,clk_out2相或改成相与。 大功告成!!!

参考文献:2

4. 小数分频

上边讲完了任意占空比任意偶数分频器,以及任意占空比任意奇数分频器后,下面讨论更加夸张的小数分频。什么是小数分频?以及怎么实现 9/4,17/3 ,6.3 等任意小数分频??

编码小数分频,就不能看微观了,要用宏观的眼界去看,比如实现一个 17/3 分频,表达成:17 除以 3 得商为 5 余2。

那么我们就可以通过5(商)分频和7(商+余数)分频 来实现 17/3 分频。

现在我们来确定5分频和7分频的次数,设:

5分频的次数为a , 7分频的次数为b;

那么应该有:

a+b=3(除数)

5a+7b = 17(被除数)

解得a=2,b=1,也就是说通过2次5分频和1次7分频可得到 17/3 分频。

这样编程完之后就实现了17/3分频,那么自然会有个疑问,为什么这样就实现了?详细看,仍然是五分频管五分频的,七分频管七分频的,大家各管各的,这算哪门子的小数分频啊??

所以就要提到我们前面说的宏观来看。宏观来看,总共是17个时钟周期,由三个分频器均分,那么平均每个分频器就是分到17/3了,这就是小数分频,这是一个宏观的平均概念。解释完概念,我们下面开始手撕代码。

4.1 代码实现

module div_decimal(

input clk,

input rst_n,

output reg clk_out,

output reg [4:0] cnt,

output reg [2:0] cnt_2to5,

output reg [2:0] cnt_1to7

);

//17/3 小数分频

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

clk_out <= 0;

cnt <= 5'b0;

cnt_2to5 <= 3'b0;

cnt_1to7 <= 3'b0;

end

else begin

//2次5分频

if(cnt<10) begin

if(cnt_2to5==0) begin

clk_out <= 0;

cnt_2to5 <= cnt_2to5 + 1;

end

else if(cnt_2to5==4) begin

clk_out <= 1;

cnt_2to5 <= 3'b0;

end

else begin

cnt_2to5 <= cnt_2to5 + 1;

end

cnt <= cnt + 1;

end

//1次7分频

else if(cnt>9 && cnt<17) begin

if(cnt_1to7==0) begin

clk_out <= 0;

cnt_1to7 <= cnt_1to7 + 1;

end

else if(cnt_1to7==6) begin

clk_out <= 1;

cnt_1to7 <= 3'b0;

cnt <= 5'b0;

end

else begin

cnt_1to7 <= cnt_1to7 + 1;

end

cnt <= cnt + 1;

end

end

end

endmodule

4.2 testbench文件

`timescale 1ns/1ps

module div_decimal_tb();

reg clk;

reg rst_n;

wire clk_out;

wire [4:0] cnt;

wire [2:0] cnt_2to5;

wire [2:0] cnt_1to7;

initial begin

clk <= 0;

rst_n <= 1;

#20

rst_n <= 0;

#20

rst_n <= 1;

#5000

$stop;

end

always begin

#10 clk = ~clk;

end

div_decimal u0(

.clk(clk),

.rst_n(rst_n),

.clk_out(clk_out),

.cnt(cnt),

.cnt_2to5(cnt_2to5),

.cnt_1to7(cnt_1to7)

);

endmodule

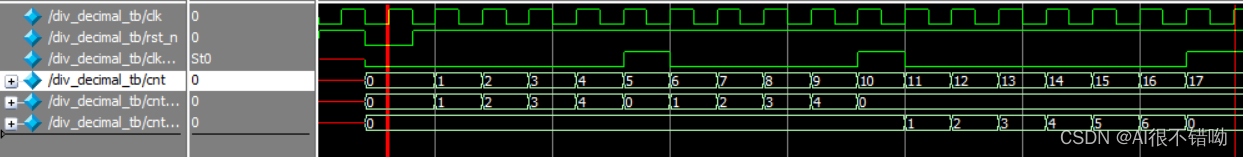

4.3 仿真结果

如同我们分析的一样,两个五分频,一个七分频,每十七个周期循环一次。即每十七个周期有三个分频器,平摊下来就是 17/3 。

小数分频的缺点就是 占空比不为50%,要想实现50%占空比的小数分频,涉及很多算法,具体算法十分复杂,一般不会作为手撕代码题。

参考文献:3

若有同学对工程文件感兴趣的,可以后台私信我发送工程文件。如有错误,及时更正,本资料仅提供学习,不可做为商业用途,因为我是一个菜鸡!!!

==========================================================================

声明

本人所有系列的文章,仅供学习,不可商用,如有侵权,请告知,立删!!!

本人主要是记录学习过程,以供自己回头复习,再就是提供给后人参考,不喜勿喷!!!

如果觉得对你有用的话,记得收藏+评论!!!

本文详细介绍了数字电路中分频器的设计,包括偶数分频、奇数分频(50%占空比及非常规占空比)和小数分频。通过Verilog代码实现,讲解了如何通过计数和条件判断来生成不同占空比的时钟信号,例如二分频、三分频、七分频等,并通过testbench文件进行仿真验证。此外,还探讨了如何通过组合不同占空比的分频器实现任意小数分频,如17/3分频。

本文详细介绍了数字电路中分频器的设计,包括偶数分频、奇数分频(50%占空比及非常规占空比)和小数分频。通过Verilog代码实现,讲解了如何通过计数和条件判断来生成不同占空比的时钟信号,例如二分频、三分频、七分频等,并通过testbench文件进行仿真验证。此外,还探讨了如何通过组合不同占空比的分频器实现任意小数分频,如17/3分频。

9743

9743

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?