0. 前言

今天分享的是芯海的关于IC验证的笔试部分题目!!!

名称如标题所示,希望大家正确食用(点赞+转发+评论)

本次笔试题一共四部分:单选、多选、填空和简答。

下边是具体的题目,仅仅是回忆,哈哈哈!!!

注意:答案中可能涉及到很多知识点没有同步到博客这边,之后会慢慢同步过来的,这里给出答案链接,大家可以先看看公众号那边的答案,谢谢!

公众号链接:

https://mp.weixin.qq.com/s/WHhzZElJPUXQiRVw9cN2sQ

1. 题目 & 答案

选择题&填空题

单选多选填空都很简单,基础基础基础!!!重要的事情说三遍!!!

好好看看书,或者一些博客什么的问题不大,就是注意一些小细节就行,比如initial只执行一次,从0时刻开始,是一个过程语句块等等等!

笔试完之后这些小的具体细节已经记不清了,但基本都是基础知识,可以到我的博客下边看看,也可以到其他好的文章下边学习学习,反正,只要能学到自己手里的东西才是最好的!!!

简答题

问题1:

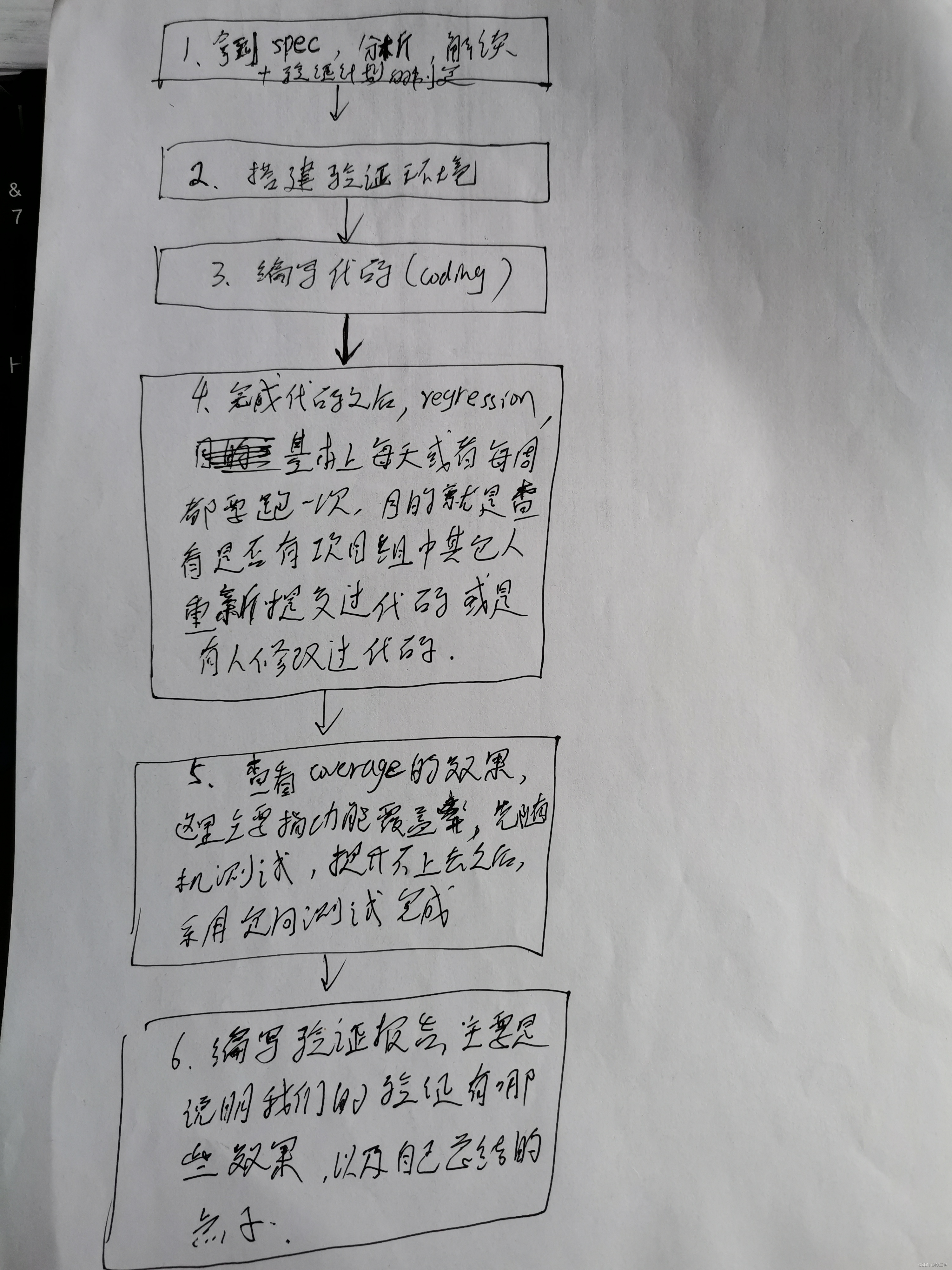

第一个简答就让你说说验证的步骤以及每一步的详细操作

解析1:

这个题目属于那种基本上必考的简答题了,只要把这个流程图顺下来基本没有什么问题,剩下的就是你个人怎么理解了。有时候在面试的时候也会遇到这类问题,我觉得follow in your heart即可!所谓说,言之有理即可,哈哈哈!

问题2:

给了一个UART,包括APB总线当作其寄存器的值,tx作为信号的输入,rx作为信号的输出,让你画出完整的验证框图,并给出说明。

解析2:

当时这个项目没做过,更没有自己做过验证啦!只是简单的了解过UART的协议,这个题可以参照一下网上的关于一些UART验证的文章,这里我也大概了解了一下,贴上一个链接供大家参考吧!

UART模块验证-面试总结

https://blog.csdn.net/kobetriumph/article/details/126056448

问题3:

是一个代码编写的题,动态数组,先初始化动态数组,之后for循环,交换位置,最后打印一下信息。

解析3:

这个题目主要考察的是对sv中的动态数组是否了解,对于他的语法和sv中的其他数组有什么区别?这些都需要在学习的时候了解到,下边给出链接,有需要的可以参照一下!

链接界面搜索《SystemVerilog 之数据类型》

https://blog.csdn.net/qq_40549426?type=blog

总体的话,题量还可以,但是前提是比较熟悉知识点,前边大概用了半小时,后边简答用了半小时。

声明

本人所有系列的文章,仅供学习,不可商用,如有侵权,请告知,立删!!!

本人主要是记录学习过程,以供自己回头复习,再就是提供给后人参考,不喜勿喷!!!

如果觉得对你有用的话,记得收藏+评论!!!

全网各平台同名===> “IC二舅”

下一期如果有大家想看的 或者 哪块不懂想学习的,可以私聊或在群里提问都可以,“二舅” 给你安排上!!!

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?