1 概述

随着 IC 芯片时钟信号频率的增加、信号边沿的减小,由此带来的信号完整性问题已经越来越凸显。 PCB 信号完整性问题主要包括由阻抗不匹配引起的信号过冲、相邻不同网络之间由于各种耦合产生的信号串扰、有损传输线造成的信号边沿退化等问题。信号完整性问题不仅会造成电路功能错误,也会造成各种电磁兼容问题。

在高速 PCB 设计过程中,为了能够使 PCB 一次设计成功的同时又能确保板级辐射发射不超标,板级信号完整性仿真分析已经成为一种重要不可缺少的手段。信号完整性仿真的模型主要有 IBIS 模型、 SPICE 模型、 VHDL_AMS 模型、Verilog_AMS 等等。其中 IBIS 模型是 PCB 设计业界中最常用的、最流行的信号完整性仿真模型。板级信号完整性仿真工具有 Mentor Graphics 的 Hyperlynx、Cadence 公司的 SPECCTRAQuest 等等。下面以 Hyperlynx 为例说明板级信号完整性仿真的方法及具体过程。

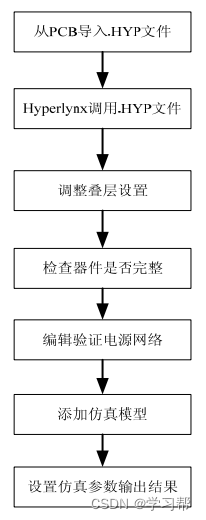

图 1 基于 Hyperlynx 的板级 SI 仿真流程图

2 生成*.HYP 格式文件

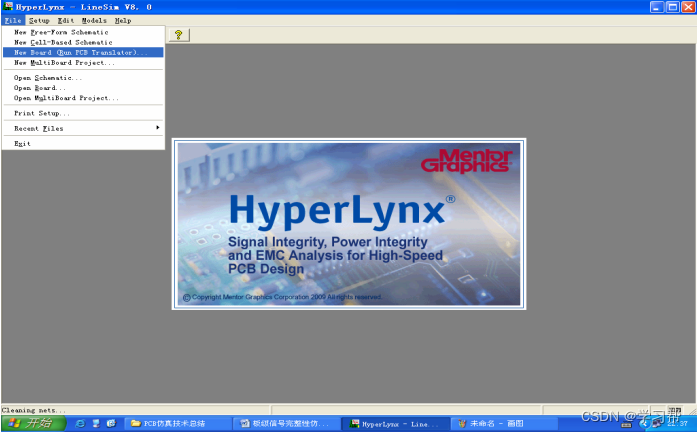

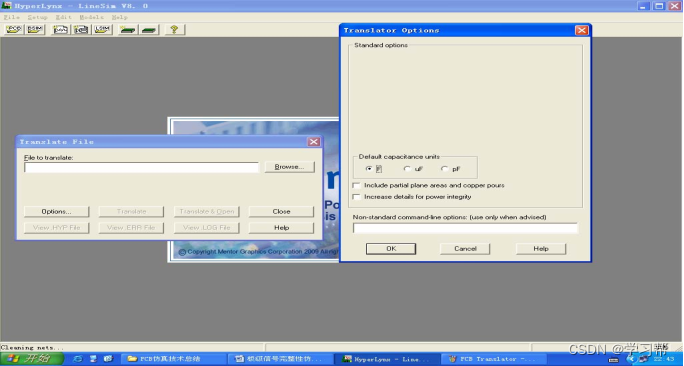

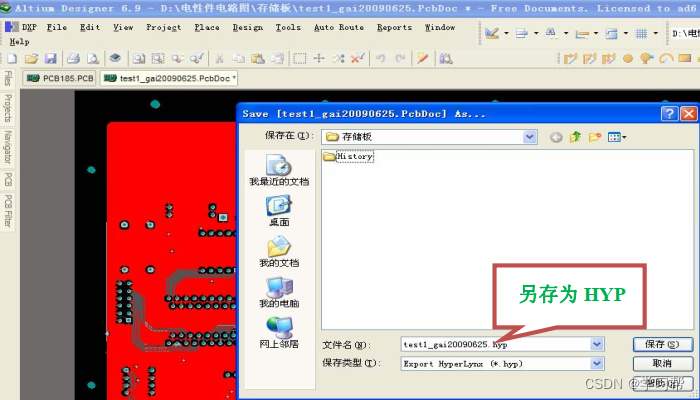

Mentor Graphics 的 Hyperlynx 软件可以支持当前较流性的 PCB 设计软件生成的 PCB 文件格式,不仅能和 Mentor 公司自己的 Expedition、 PADS、 BoardStation 等 PCB 设计软件进行无缝链接,还可以和其他 PCB 设计软件,比如Altium 公司的 Protel(高版本为 designer)、 Cadence 公司的 Allegro 软件及株式会社公司的 Zuken 软件通过接口进行链接。一般得到*.HYP 格式文件有两种方法:第一种是利用 PCB 设计软件本身自带的和第三方 EDA 软件的接口(这里是指 PCB 设计软件和 Mentor 公司的 Hyperlynx 软件之间的借口),比如在 Protel软件中,其 PCB 文件本身就可以导出 Hyperlynx 可以读取的.HYP 格式的文件;第二种是利用 Hyperlynx 软件自带的 PCB 转换工具,将目标 PCB 文件直接转换成仿真所需的.HYP 文件, Hyperlynx8.0 支持转换的 PCB 格式有以下几种:Cadence 公司的*.DSN、 *.brd 文件、 Accel 公司的*.PCB 文件、以及株式会社的*.PCF 文件等。图 2、图 3 是使用 Hyperlynx 自带的 PCB 转换工具来生成.HYP 文件;图 4

则是在第三方 EDA 软件 Protel 中生成.HYP 文件。

图 2 Hyperlynx 的 PCB translator 菜单

图 2 Hyperlynx 的 PCB translator 菜单

图 3 PCB translator 选项设置

图 4 Protel 导出 HYP 格式文件

图 4 Protel 导出 HYP 格式文件

注意事项:在对 PCB 文件进行 HYP 格式转换前要指定 PCB 文件中的各平面层(如果不指定 Plane 面则转换时会报错),且 Plane 层的命名要符合一般通用规则(比如电源层名字使用关键字 VCC 开头,地层名字使用 GND 关键字开头等);无源器件如电阻、电容、电感器以及磁珠等的取值信息尽量详细。

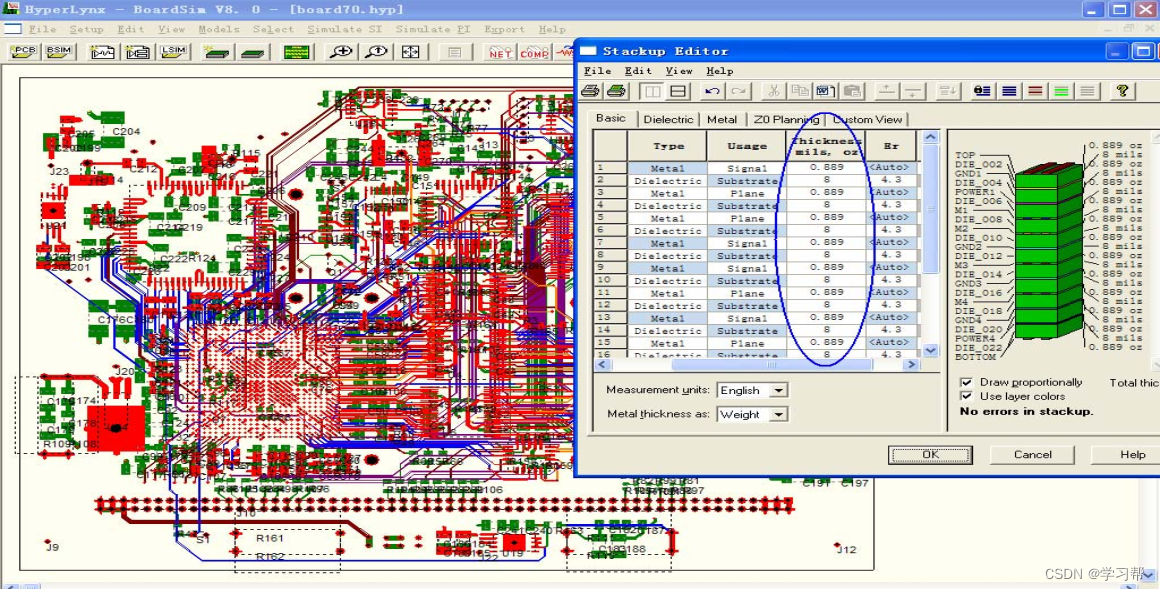

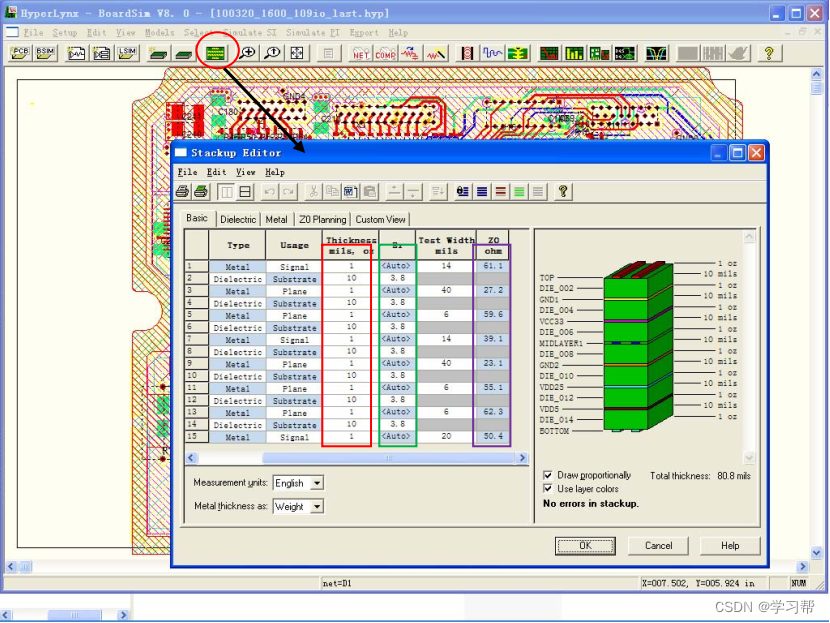

3 导入*.HYP 格式文件设置叠层

当导入一个 HYP 文件后首先要做的就是要对 PCB 的叠层作修改, 如介质厚度、平面层厚度、介质的介电常数及特征阻抗等等,使其符合实际的 PCB 加工情况。 HyperLynx 对由 PCB 文件转换导入的 HYP 文件有一个默认的叠层设置,这个默认值一般不能直接使用,需作修改。

图 5 调整叠层设置

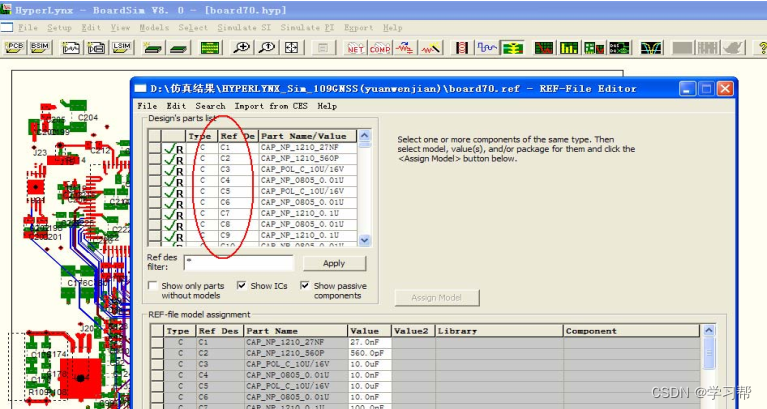

4 检查元器件的命名

打开 HYP 文件后要先检查 PCB 中的元器件是否都已完全无误的导入到 HYP文件中了,检查元器件的标号是否缺失、完整,如图 6 所示。

图 6 检查元器件编号

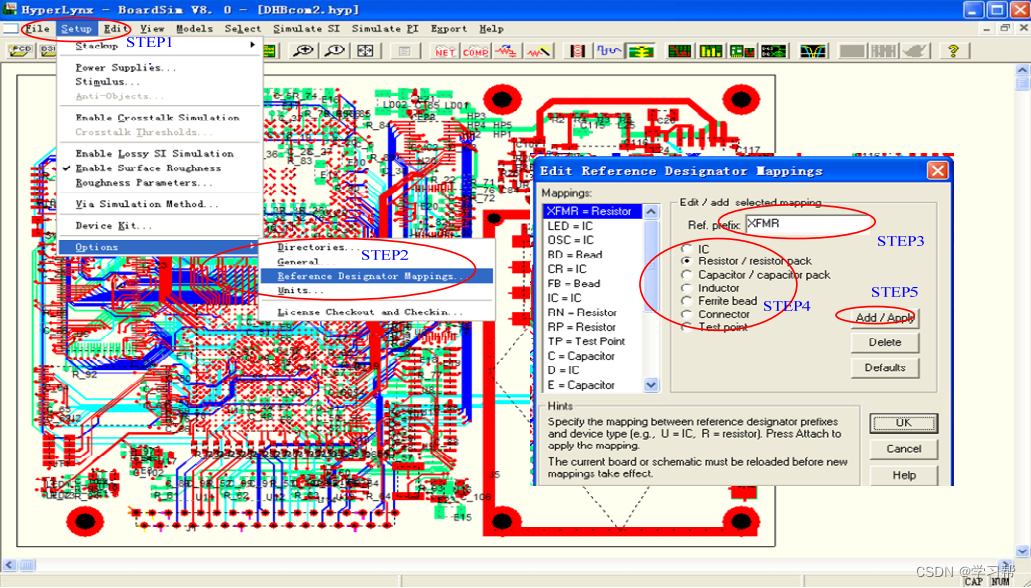

如果有部分元器件因为标号命名方式不符合一般命名规则而未被软件所识别,则可修改软件中的器件命名规则方式,从而使得器件能够被软件所识别。

点击SETUPÆOPTIONÆREFERENCE DESIGNATOR MAPPING 选项,即弹出器件标号映射修改对话框,如图 7。在对话框中选择所要映射器件标号的首字母以及将该器件所要映射的类别后,点击 Add 按钮即可新建一标号映射规则。

图 7 修改元器件标号映射规则

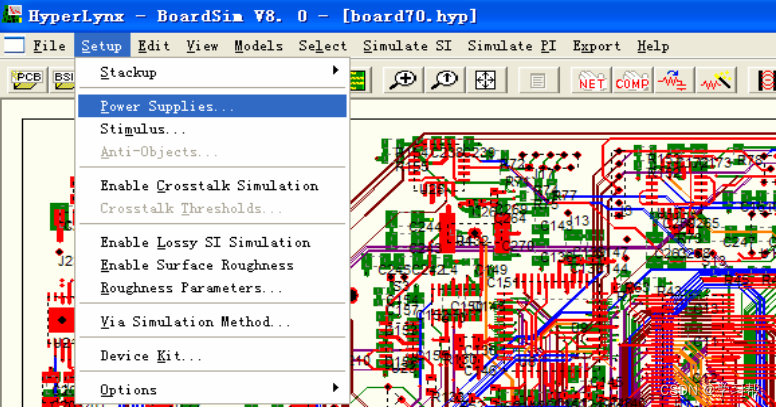

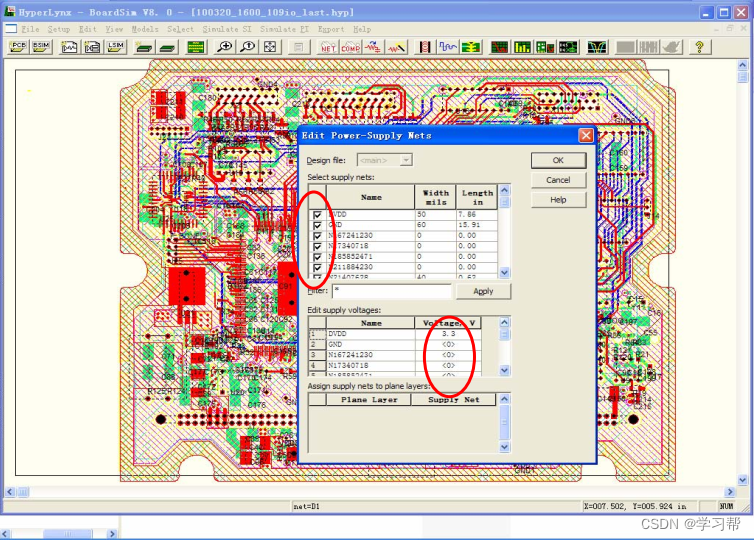

5 定义电源网络

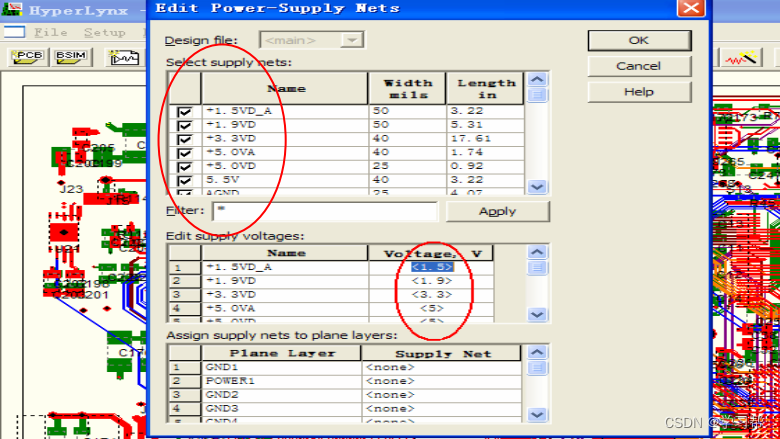

Hyperlynx 在计算网络的过冲及串扰时不考虑周围电源网络的影响,默认电源网络上是静态的直流信号。所以为了避免不必要的计算量,仿真前应该对所有直流电源网络赋予直流电源特性,使 Hyperlynx 能识别出 PCB 网络中所有的电源网络,以避免不必要的计算。点击 SETUPÆPOWER SUPPLIES,如图 8 所示,弹出图 9 所示界面,先在 NET 里选择电源网络的,再为已选电源网络赋予直流电压和所属叠层。

图 8 编辑电源网络

图 8 编辑电源网络

图 9 给电源网络赋电源值

图 9 给电源网络赋电源值

6 加载仿真模型

6.1 仿真器设定

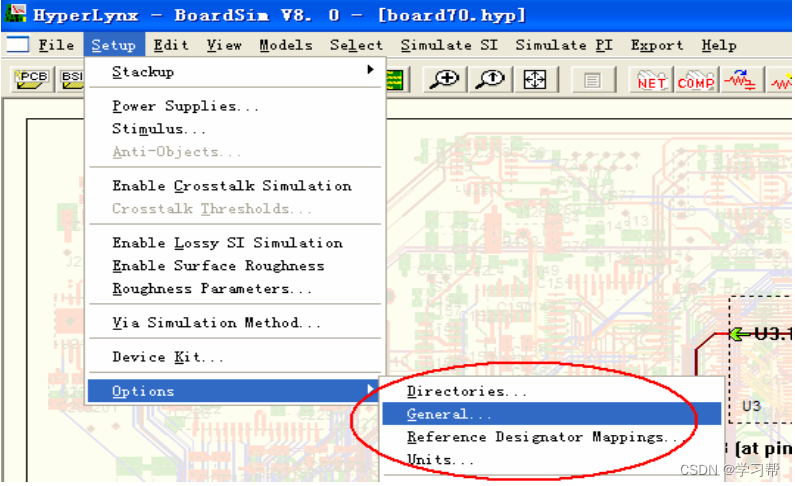

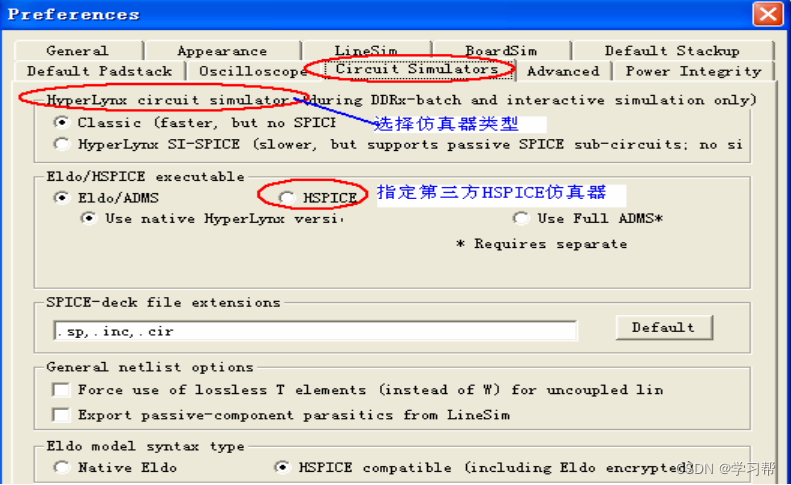

Hyperlynx 支持的主要仿真模型类型有 IBIS 模型、 MOD 模型、 SPICE 模型,仿真时应根据器件所加载的模型类型选择合适的仿真器,否则会出错。一般若文件中模型均是 IBIS 模型、或者 MOD 等模型而无 SPICE 模型,则 Hyperlynx 会自动直接调用 Hyperlynx 仿真器; 对于 SPICE 模型, Hyperlynx 可调用自带的 Eldo仿真器或者由操作者指定第三方 HSPICE 仿真器。 具体设置方法如图 10、 图 11。

图 10 SETUP 选项

图 11 仿真器设置

图 11 仿真器设置

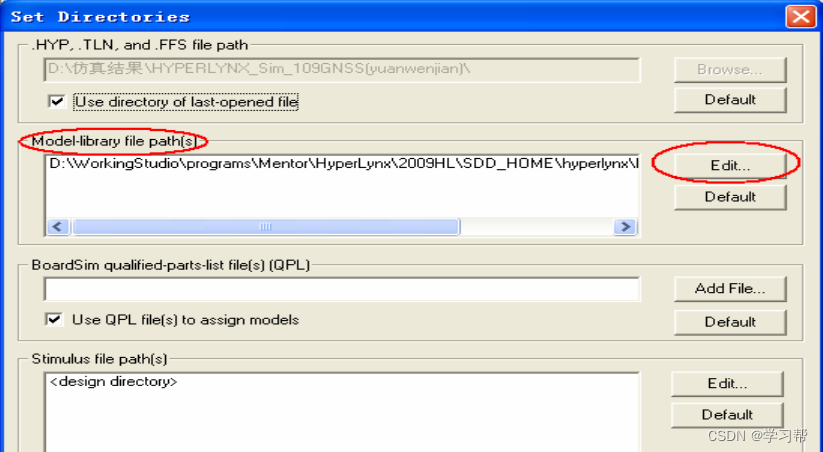

6.2 加载模型库

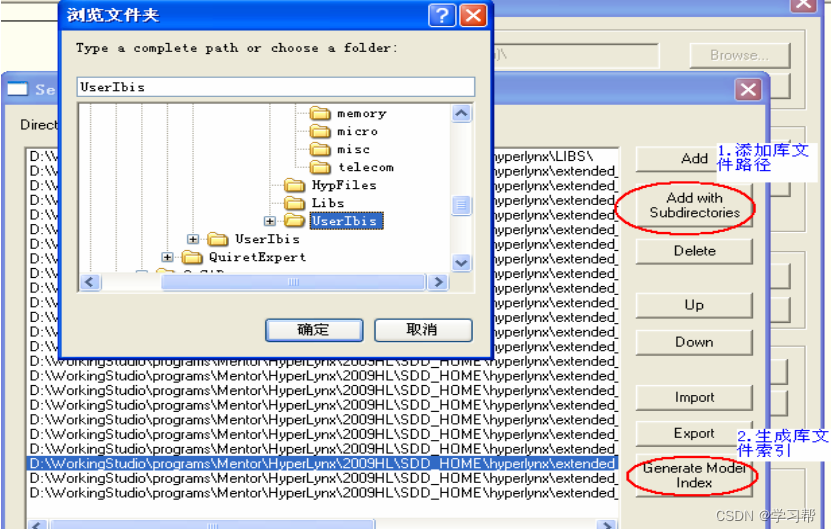

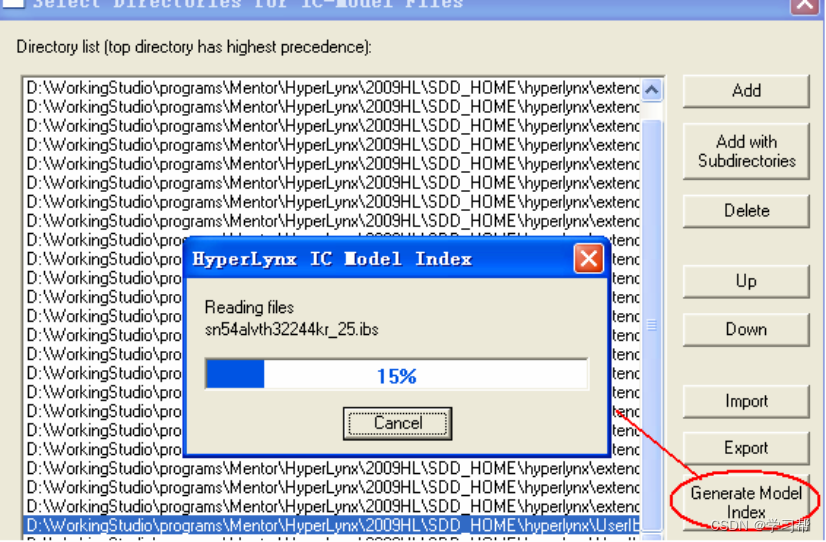

在加载模型之前,用户可将自己模型整理好放在指定的文件夹,并在软件的仿真库路径选项中添加该文件夹的路径。然后生成模型文件查询索引,以便在给器件赋模型时便于器件模型查询、搜索。点击 SETUPÆ OPTIONÆDirectories 子选项中,弹出仿真模型库文件夹路径编辑选项,如下图图 12、图 13 所示。

图 12 系统文件夹选项

图 13 添加库文件路径

在添加完库文件路径后要重新生成新的库文件索引, 便于在给器件赋模型时进行搜索和查找,如图 14 点击对话框右下角生成模型索引按钮生成索引。

图 14 生成模型库文件索引

6.3 添加器件模型

仿真前加必须为器件添加行为模型,为器件赋予仿真模型的方法有多种。根据仿真的实际需要可选择合适的模型加载方法。 Hyperlynx 中常用模型加载方法有以下三种:

- 交互式模型添加方法

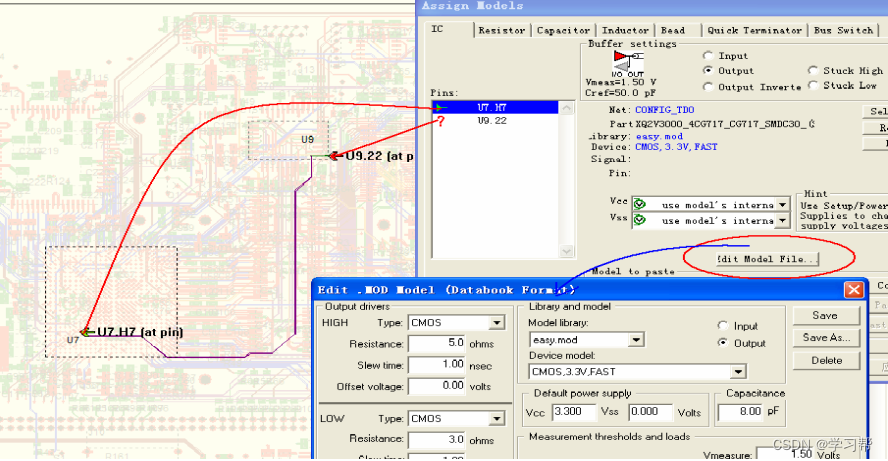

在没有大部分器件的模型情况下,只针对特定网络进行信号完整性仿真时,可先选定该特定网络然后对与该网络相连的各器件管脚一一进行模型赋值。 这种交互式模型赋值方法快捷、 灵活、 简单, 可以只给一个器件的某几个管脚赋模型,适合在没有整个器件模型的情况下使用; 而且可以使用.MOD( model of databook)模型,很容易对器件某一管脚的驱动器模型的上升沿时间、下降沿时间、管脚寄生电容、电阻参数做修改。选中待仿真的信号,点击快捷工具栏中的 COMP 选项,弹出管脚模型赋予界面。如图 15 所示,可为管脚选择.MOD 模型。

图 15 部分管脚模型赋值

- 使用.REF 文件的模型添加方法

使用.REF 文件的模型添加方法可以一一为每个器件赋予 IBIS 模型,这需要各个器件都有 IBIS 模型文件。这种模型赋值方法的好处是只需指定器件模型的IBIS 文件,就可以将文件中的管脚模型自动映射到实际器件的管脚上,无需再为每个管脚一一赋模型。当给所有器件均赋予了模型后,就可以选定任意网络进行交互式型号完整性仿真, 也可选定几个网络或所有网络进行信号完整性批处理模式仿真,这种情况下仿真具有很高的精度和真实性。

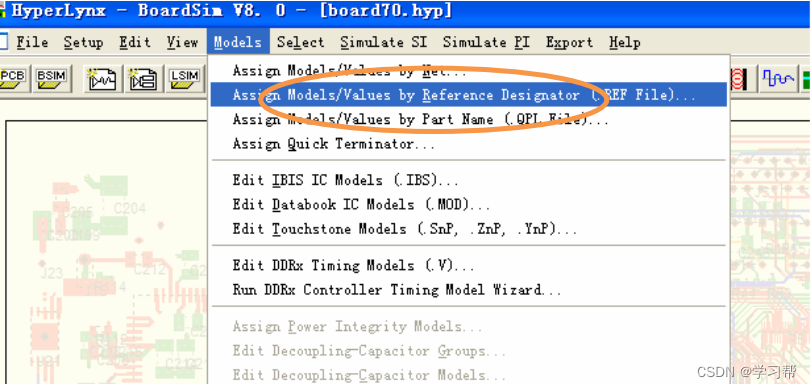

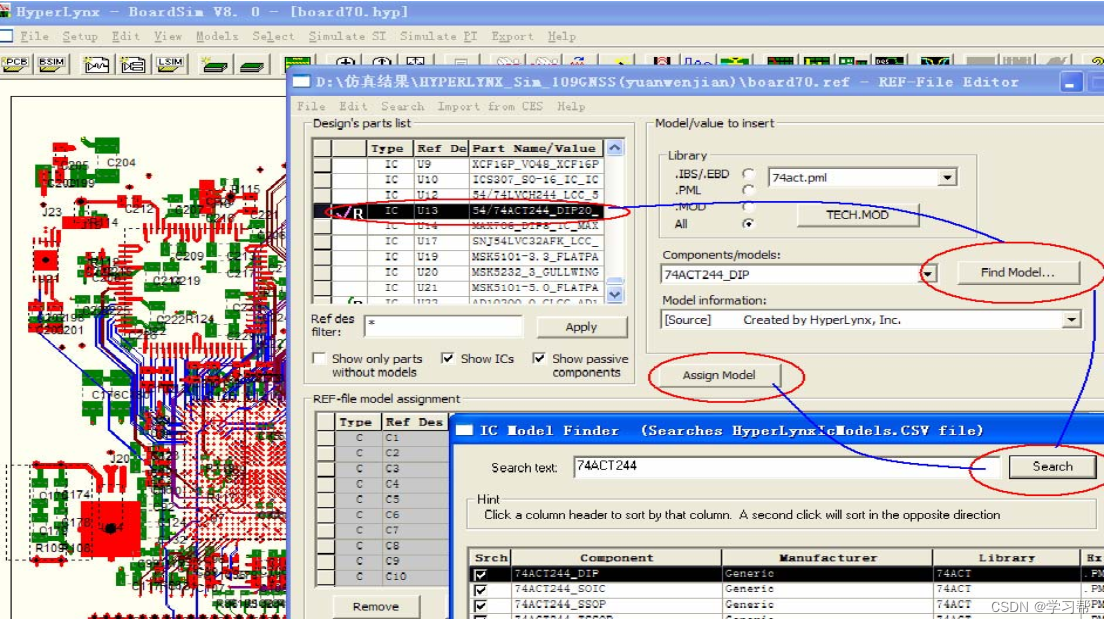

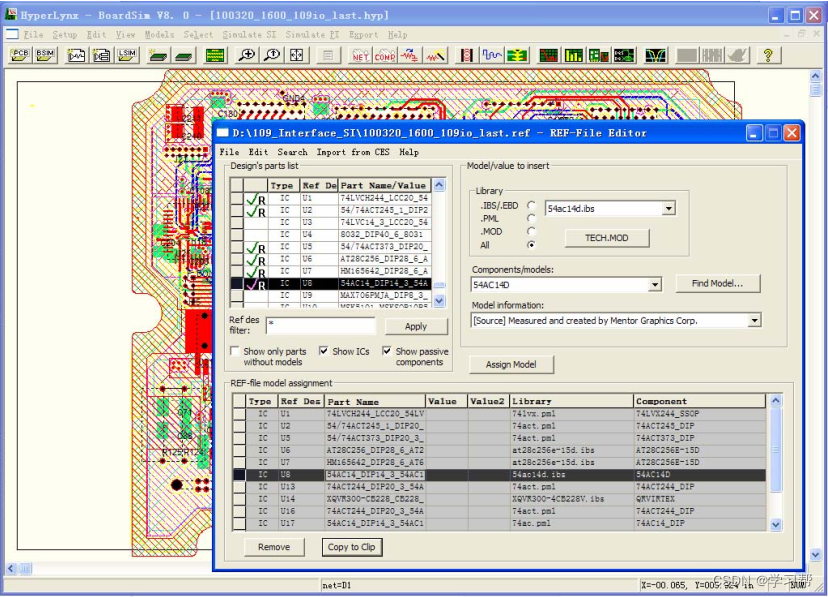

在 菜 单 栏 选 择 MODELÆASSIGN MODEL BY REFERENCEDESIGNATOR,如图 16 所示。然后弹出图 17 所示界面,在元器件一栏选中某一元器件,然后点击 Find Model 按钮,弹出器件模型搜索对话框。在搜索栏中键入器件名称(因为一般器件模型名字均保存为器件名字),为了进行模糊搜索可以只键入器件名字的部分字。在搜索结果中选择正确的器件模型,然后点击ASSIGN 进行模型赋值。对于其他器件可以依次使用这种方法进行模型赋值。

图 16 模型添加方法选择

图 17 基于器件标号的模型添加方法

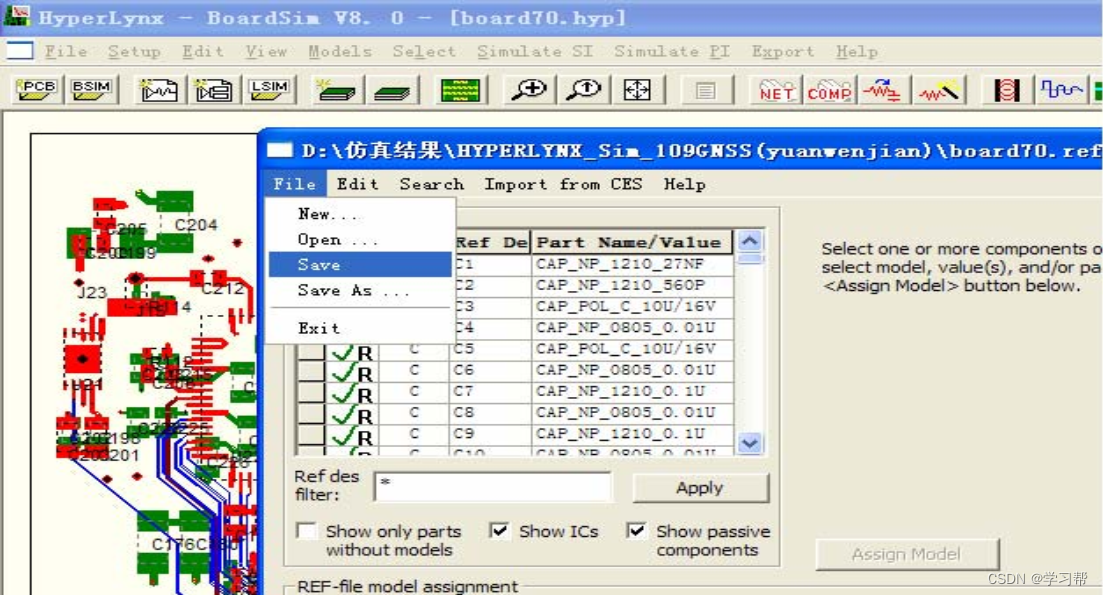

当对模型赋值操作完毕后,点击文件中的保存选项,如图 18 所示。保存当前的模型赋值信息,以便在下次调入 HYP 文件时自动加载模型,避免再次模型赋值。文件名默认与 HYP 文件同名,后缀为.REF。

图 18 保存 REF 文件

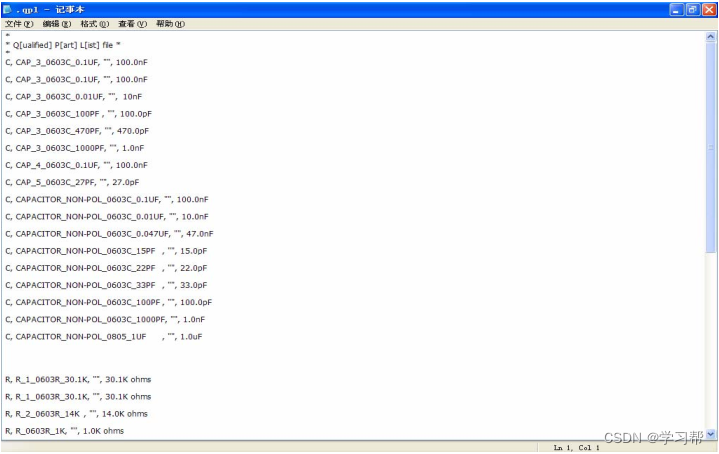

- 使用.QPL 文件的模型添加方法

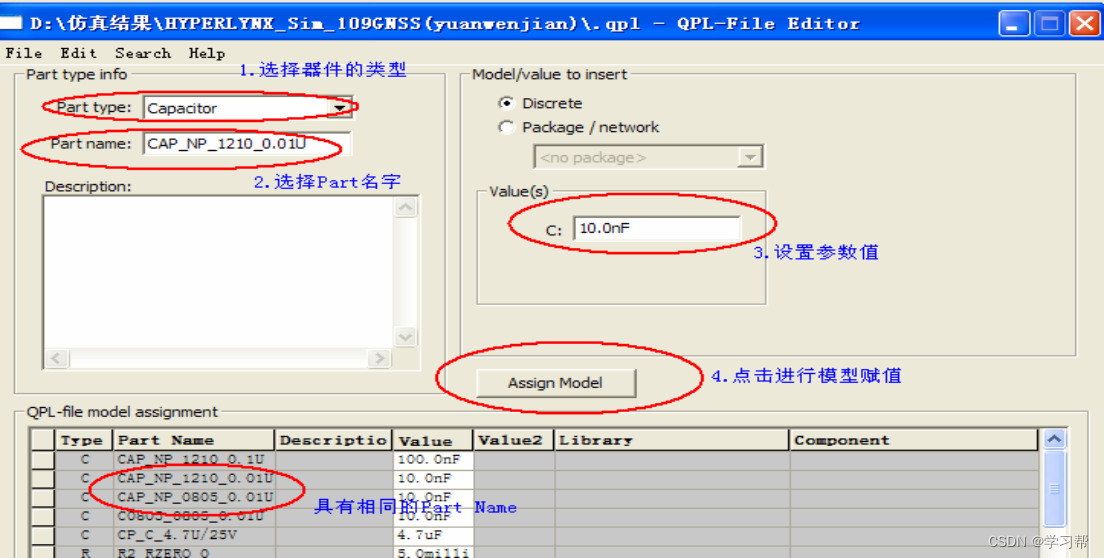

另外一种方法是使用 QPL 文件一次为一批具有相同取值的元件赋值。这种方法适合为许多相同的无源器件,如具有相同取值的电容、电阻等器件进行快速赋值。

在菜单栏选择 MODELÆASSIGN MODEL BY PART NAME, 如图 16 所示。弹出如图 19 所示界面。 依次选择器件的 PART TYPE、 PART NAME 以及 VALUE后,点击 ASSIGN MODEL 按钮则具有该 PART NAME 的器件全部被赋予了VALUE 值或者模型。

图 19 使用交互界面编辑.QPL 文件

图 20 使用文本编辑器编辑.QPL 文件

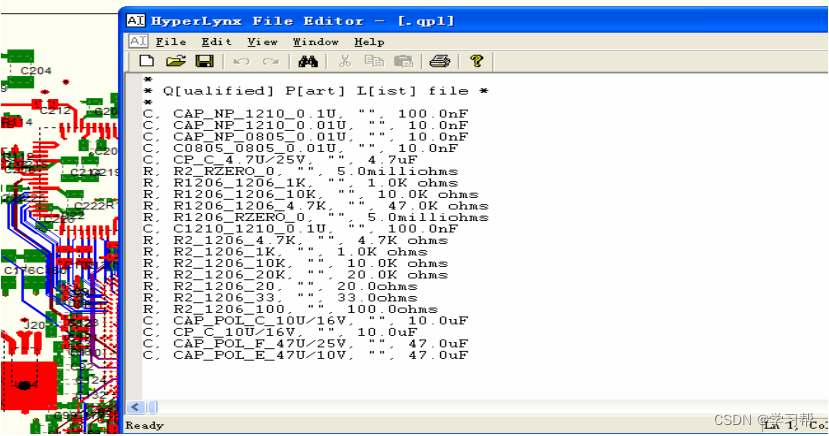

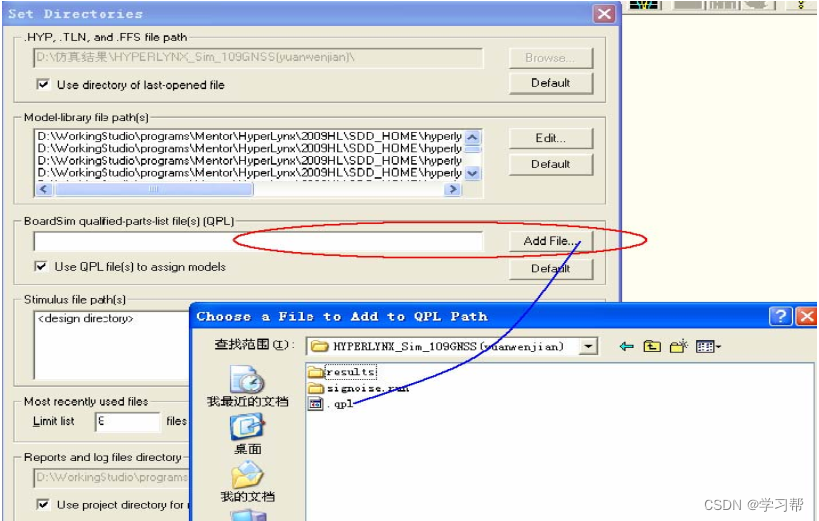

也可以使用文本编辑器直接打开.QPL 对其进行编辑,格式如图 20 所示。在使用“ *.QPL”文件为器件模型赋值前,需在 SETUPÆ OPTIONÆDirectories选项中添加 QPL 文件,如图 21 所示。一般 QPL 文件的位置在 HYP 源文件的文件夹中。

图 21 QPL 文件加载设置

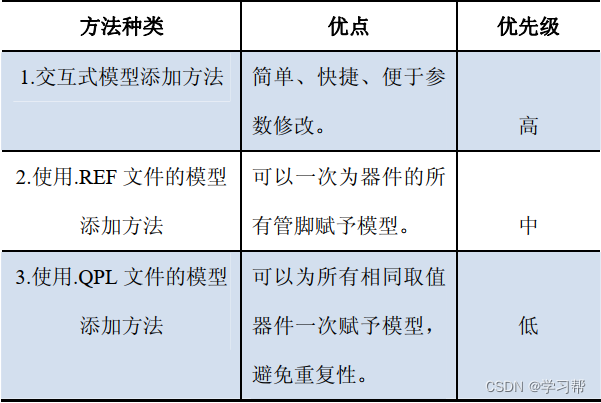

对三种添加器件模型的方法进行比较,结果如下表所示:

表格 1 三种添加器件模型方法比较

7 交互式 SI 仿真模式

Hyperlynx 信号完整性仿真模式有两种, 一种是基于界面交互式的仿真模式,另外一种是基于批处理的仿真模式。交互式仿真一次只能仿真一个网络。

7.1 过冲仿真

过冲是信号完性的重要内容,由过冲引起的振铃效应可能会产生严重的EMI。通过过冲仿真,优化布线阻抗或者端接阻抗,可最小化过冲,从而减小PCB 的辐射发射,改善电路板的电磁兼容性。

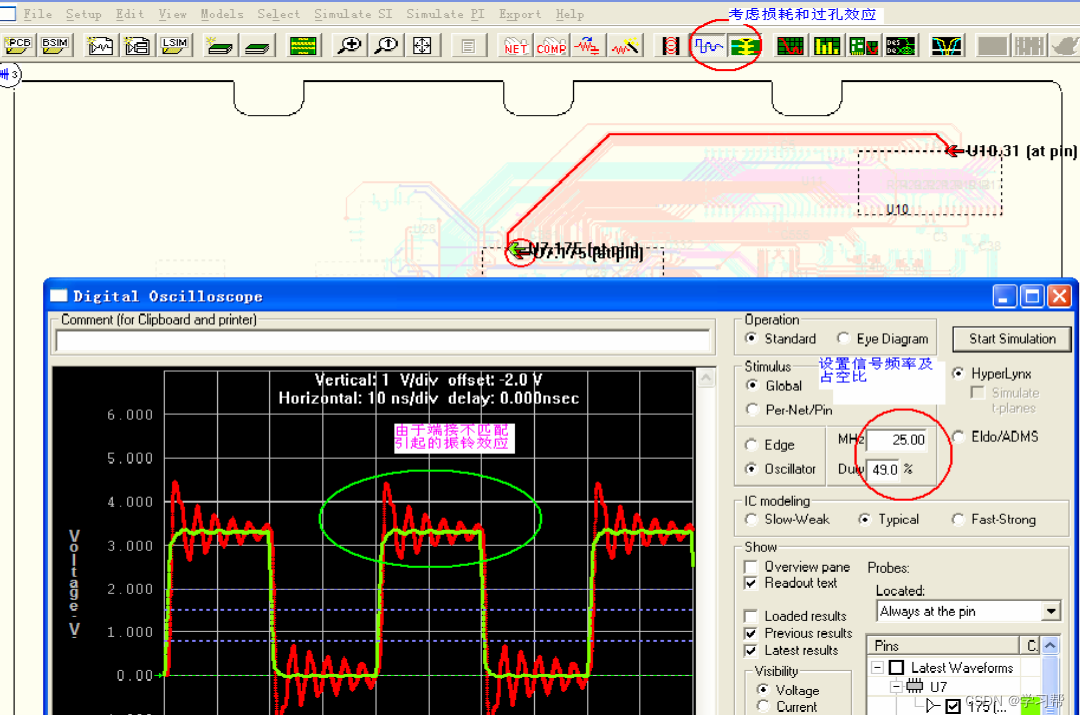

过冲仿真只涉及单个网络,选定待仿真的网络后,根据实际情况为网络上各个管脚赋予驱动器或者接收器模型,然后点击菜单 SIMULATE SIÆRUNINTERACTIVE SIMULATION,打开仿真示波器,设置信号频率及占空比。如果要考虑传输线和介质的损耗及过孔效应,可以在工具栏选项中点击选中![]() 和

和 ![]() 两项选项。

两项选项。

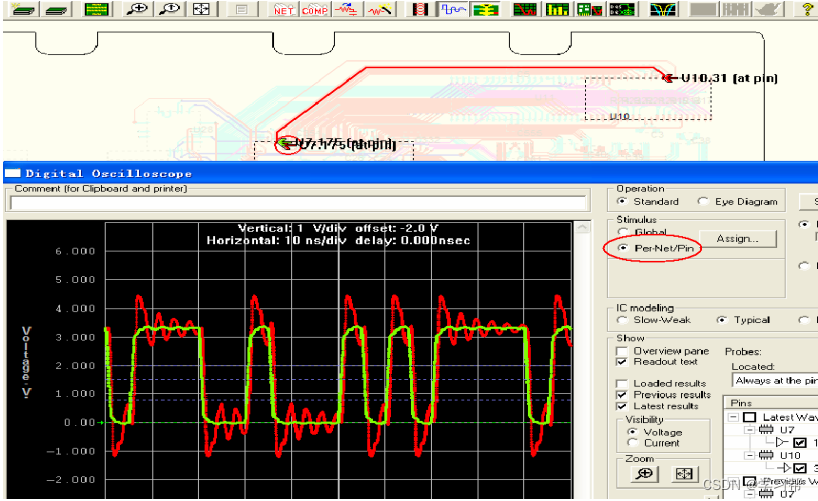

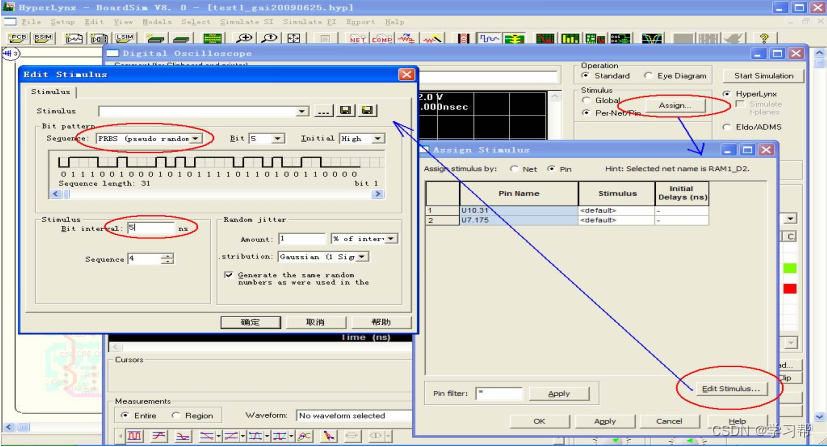

仿真激励设置方式有两种, 一种是将激励设置为标准的具有一定占空比的周期脉冲信号,对应 Global 选项;另外一种是将激励源设置为常用的数字比特流激励,对应 Per-Net/Pin 选项。

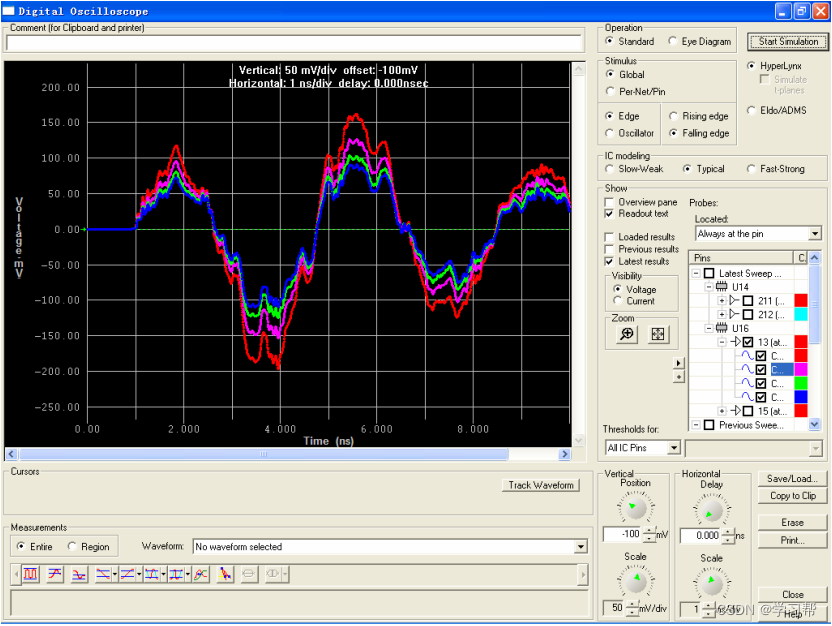

仿真结果查看方式可以选择查看信号的边沿或者信号的完整振荡周期, 如图22 所示,绿色的是驱动器输出端信号,红色的是接收器输入端信号。

图 22 Global 激励源下的过冲仿真

图 23 是采用一种常用的伪随机激励源信号, 比特流间隔为 5ns 的仿真结果。其中数字激励的设置方法如图 24 所示。

图 23 伪随机比特流激励下的过冲仿真

图 24 Stimulus 选项设置

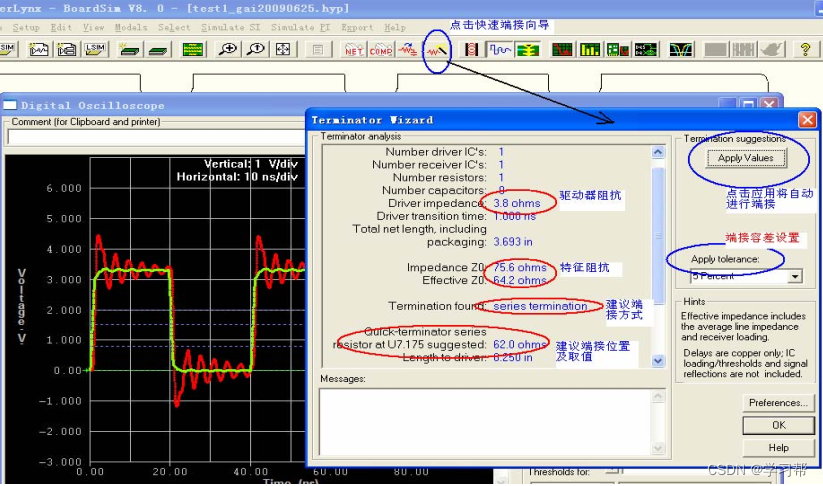

针对信号过冲问题 Hyperlynx 中提供了一种快速端接措施。 Hyperlynx 能根据元器件布局、布线拓扑结构、布线特性阻抗、驱动器输出阻抗、接收器输入阻抗等参数自动计算出最佳的端接阻抗及端接位置。

点击工具栏的快速端接向导,弹出如图 25 所示界面。向导左边框显示为驱动器及布线阻抗特性、端接以及建议的端接方式和电阻取值。点击 Apply Value选项后,软件会自动实施端接措施。

图 25 端接向导设置

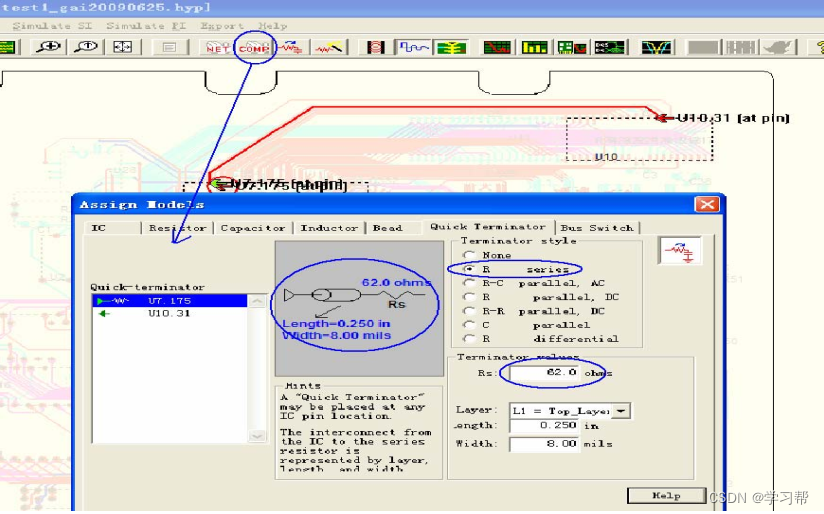

点击 COMP 工具选项,可以看到在 U7.175 管脚的 Quick Terminator 选项中出现了一个端接选项,如图 26 所示。这个就是上面使用快速端接向导产生的端接措施。

图 26 查看端接情况

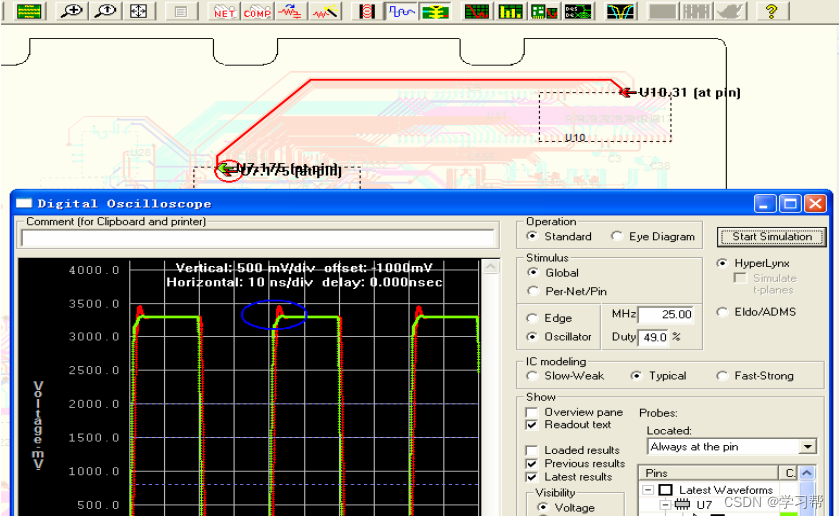

再次仿真,对比前次仿真结果(如图 22)可以发现信号过冲明显减弱,如图 27 所示。

图 27 优化后的信号过冲

7.2 串扰仿真

串扰是多个不同网络间的相互干扰,其机理是传输线之间的容性和感性耦合。当某一网络上信号变化时(信号上升边沿或下降边沿),该变化会反映到其他网络上,造成其他网络上产生串扰噪声。

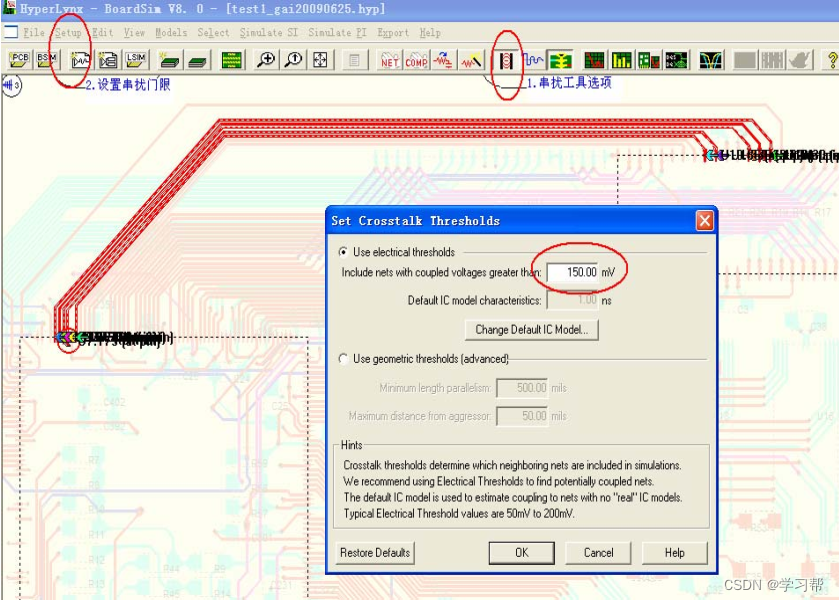

图 28 串扰仿真门限设置

仿真串扰前先设定串扰门限,点击 SETUPÆCROSSTALK THRESHOLDS合理设置串扰的门限值,一般建议将串扰门限设置为器件逻辑高电平的 5%。

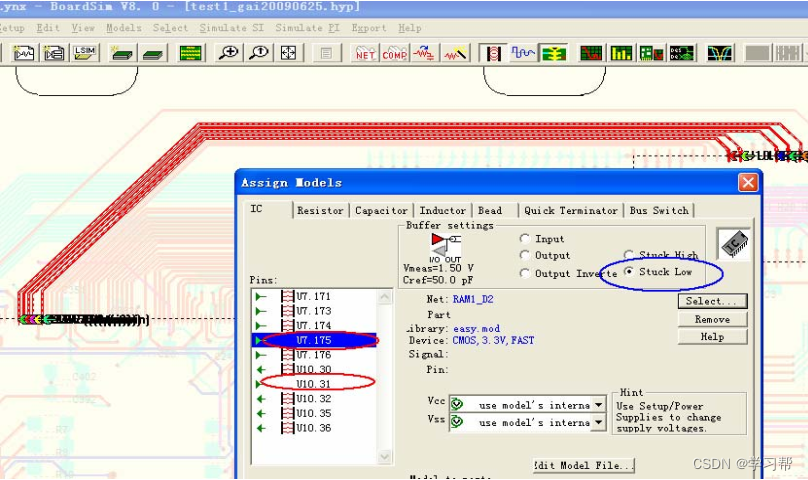

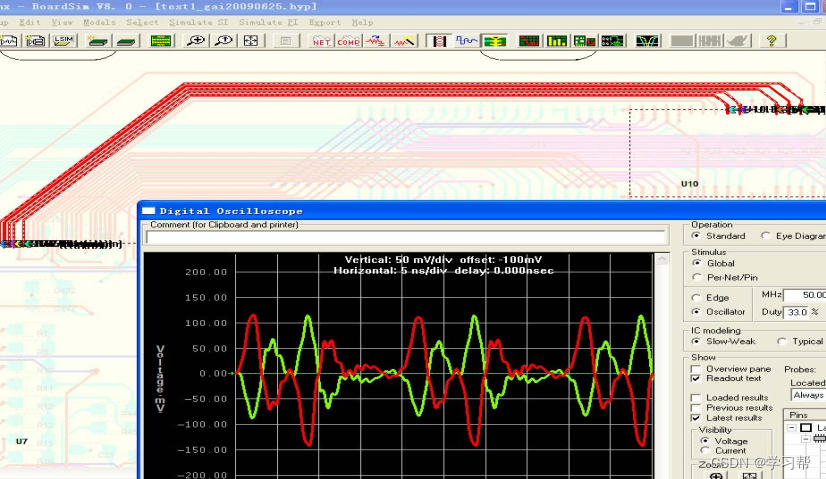

然后选定被攻击网络,在工具栏选中串扰选项,则在选定的被攻击网络周围会出现一些攻击网络。 如图 28 所示, 在版图中待仿真的被攻击网络用实线表示,其周围四个的攻击网络用虚线表示。将被攻击网络上的各个器件管脚设置为STUCK LOW 状态,其他攻击网络上的器件管脚设置为正常工作状态,设置如图29。查看被攻击网络上由于串扰引起的噪声干扰信号,结果如图 30 所示。

图 29 被攻击网络上管脚设置

图 30 串扰仿真结果

通过串扰仿真可以发现 PCB 上有问题的布线网络, 如布线间隔太近的网络、走线过长的网络等。针对串扰较严重的网络可以采取适当的措施减小串扰,如缩短走线长度、增加线距、增加隔离布线并端接等措施。图 31 为增加防护布线后的串扰仿真结果(将被攻击线临近的两根走线当作隔离防护布线),对比图 30可以看出增加防护布线后能够有效地减小串扰。

图 31 增加隔离布线后串扰仿真结果

7.3 辐射仿真

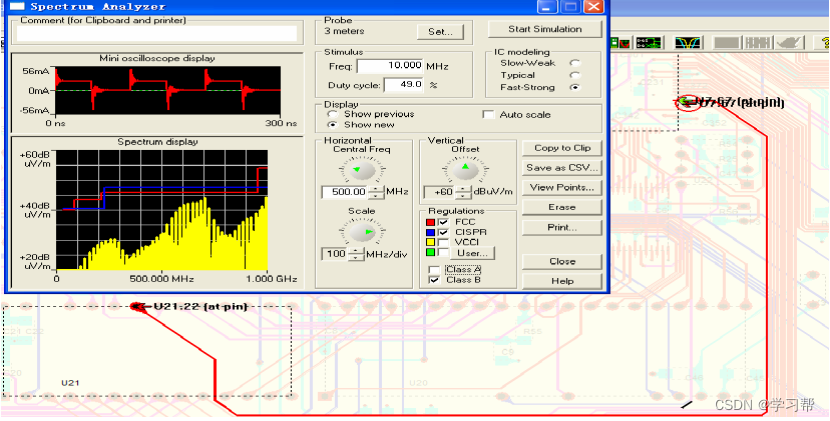

Hyperlynx 提供了一个 EMC 仿真工具,可以查看只含单一驱动输出网络的辐射情况,可以模拟天线测量辐射发射场强值(也可模拟近场电流探头)。 图 32所示为单个网络的辐射发射仿真,天线距 PCB 距离为 3m。

图 32 EMC 仿真结果

8 批处理仿真模式

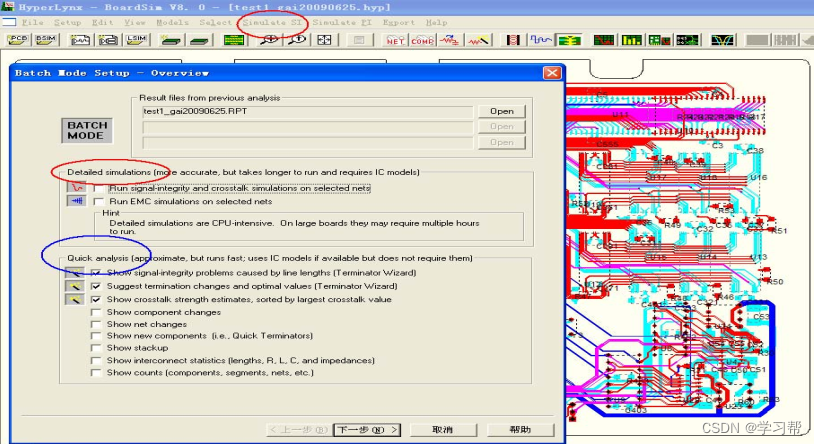

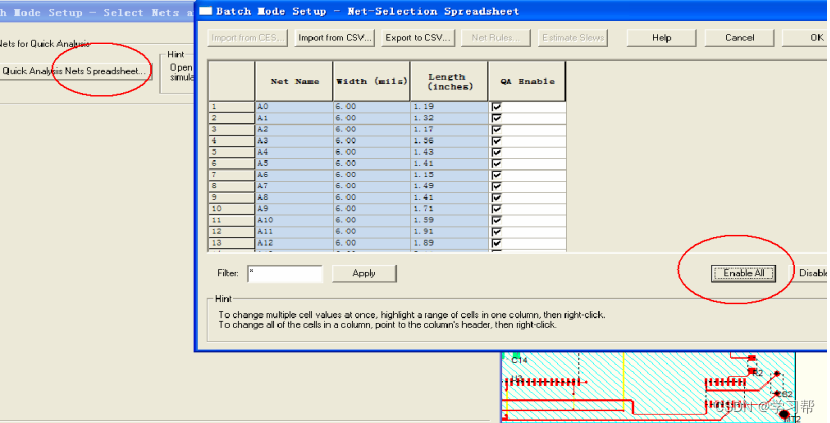

交互式仿真模式一次只能对一个网络进行过冲仿真或者是串扰仿真; 批处理仿真模式一次可以对多个网络或者所有网络进行信号完整性分析或者 EMC 分析,但是仿真时间较长,速度较慢。批处理仿真模式的仿真结果保存在.RPT 格式或者是 CSV 格式文件中,不如交互式仿真模式结显示那样直观。在菜单SIMULATE SI 中选择 RUN GENERIC BATCH SIMULATION,弹出如下仿真设置向导,如图 33 所示。

图 33 批处理模式仿真设置向导

向 导 中 可 选 择 两 种 仿 真 , 即 DETAILED SIMULATION 和 QUICKANALYSIS。 其中 DETAILED SIMULATION 包括信号完整性分析和 EMC 分析,要求所选网络都有仿真模型; 而 QUICK ANALYSIS 无需所有仿真网络都有仿真模型,只是从信号完整性和 PCB 设计规则的角度快速分析所选网络是否有潜在的问题,如是否布线长度过长、终端有无匹配端接、网络间串扰是否严重等,并将这些将结果进行分类、汇总和排序。

8.1 QUICK ANALYSIS 分析

进入批处理仿真模式,点击进入下一步选择待分析的网络,如图 34 所示,选择所有网络进快分析。

图 34 选择待分析网络

图 35 控制报告显示的内容

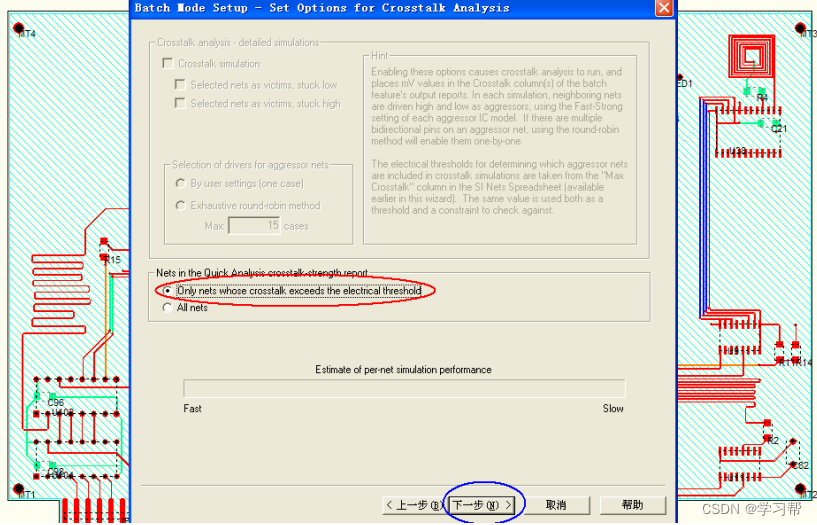

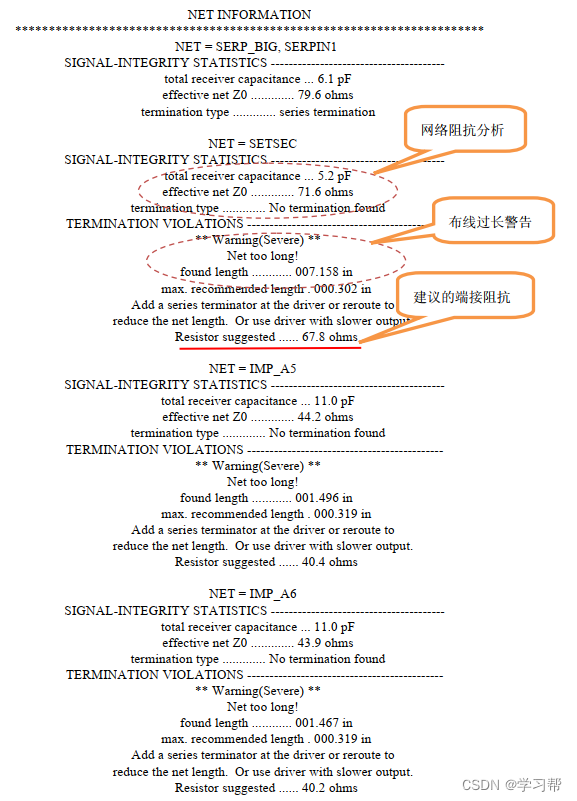

依次点击下一步,进行各种设置,最终得到一个文本结果报告。下面是QUICK ANALYSIS 分析的部分串扰仿真结果显示。

下面是 QUICK ANALYSIS SI 分析的部分结果显示:

8.2 DETAILED SIMULATION

使用仿真设置向导,设置步骤如上,在此不再赘述。仿真结束后最终得到如下内容的文本报告:

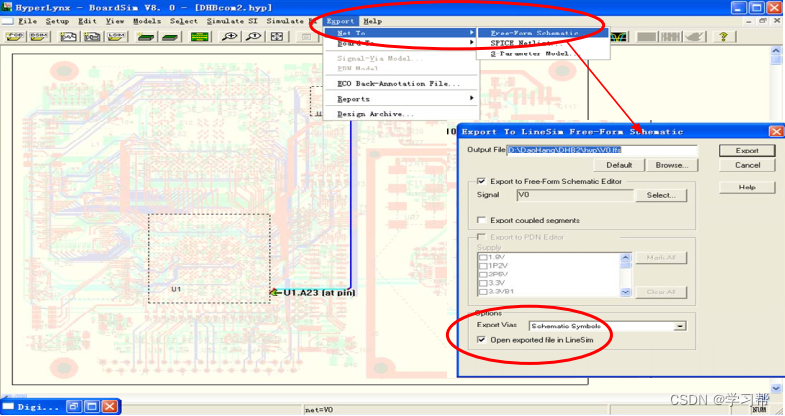

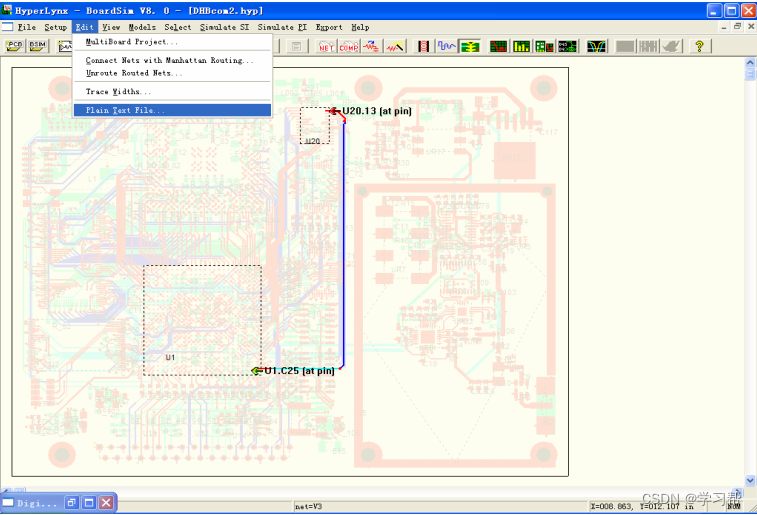

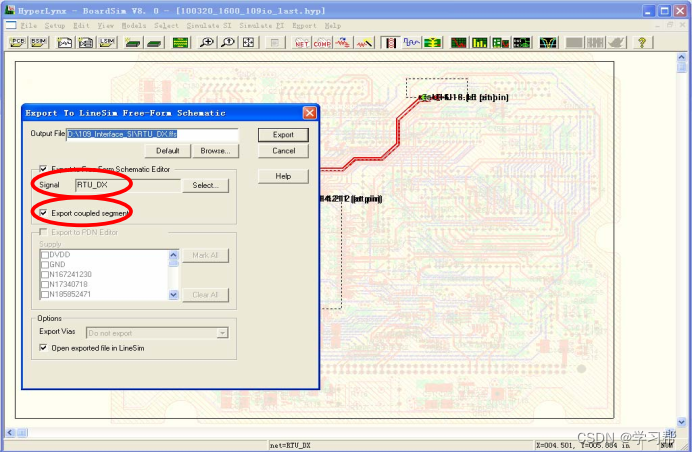

9 导出到 LineSim 中进行前仿真

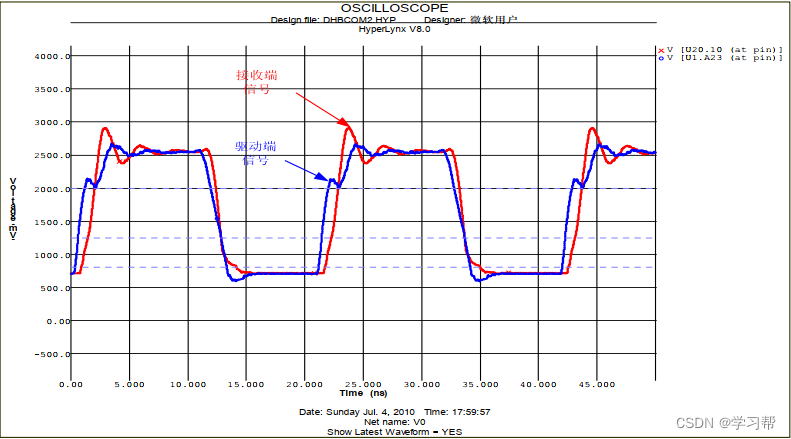

在 BoradSim 中可以将待仿真的信号网络导出到前仿真工具 LineSim 中进行仿真。因为在 BoardSim 中网络的布线长度、线间距以及过孔模型都无法改动,无法进行改进后分析。导入到 LineSim 中后网络的布线长度、线间距以及过孔模型都可以灵活改动,而且可以对这些参数进行扫描分析。从而寻找到最优改进措施。 选中待仿真的网络点击 EXPORTÆNET TO FREE FORM SCHEMATIC 菜单,弹出如图 36 所示的界面。图 37 是其在 BoardSim 中仿真结果。

图 36 信号网络导出到 LineSim 中

图 37 所选信号网络过冲仿真结果

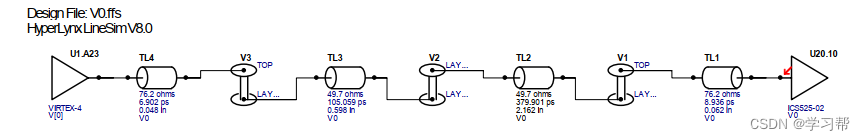

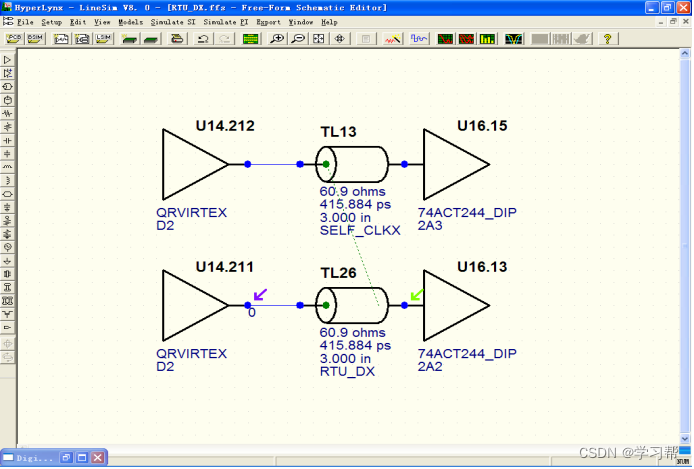

点击 EXPORT 按钮后, Hyperlynx 将调用 LineSim 模块打开导出的 LineSim格式文件,导出模型如下图所示:

图 38 网络导出的信号完整性电路仿真模型

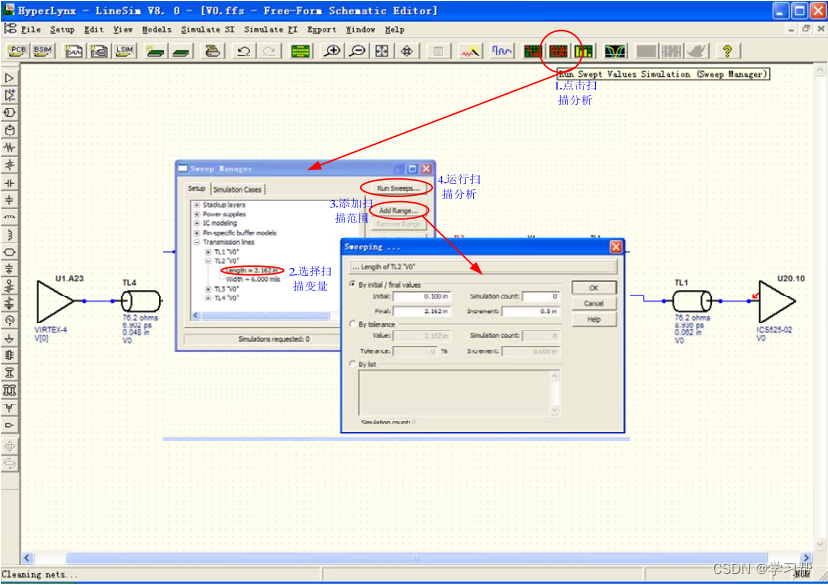

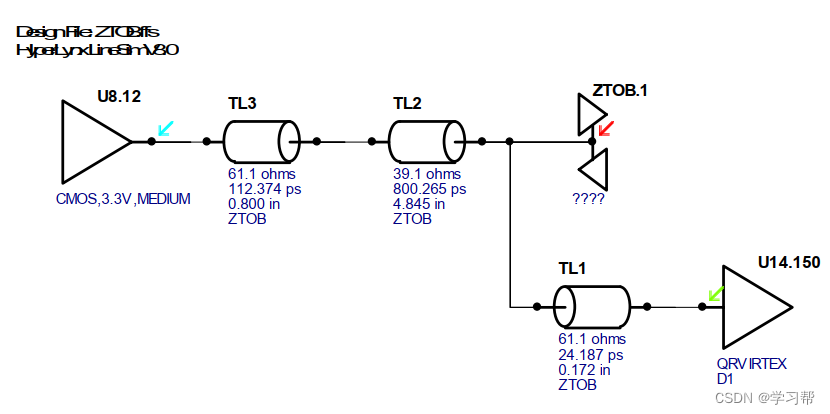

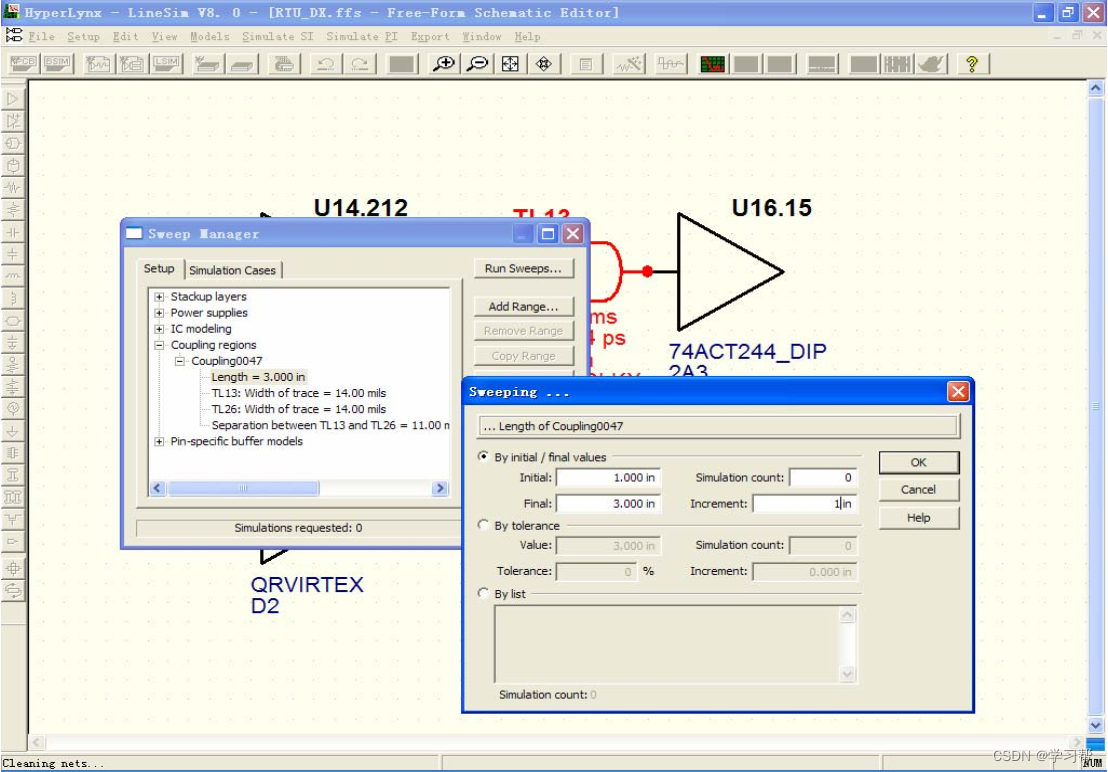

针对信号过冲现象,采取缩短布线长度措施,对图 38 中布线 TL2 的长度进行扫描分析。详细步骤见图 39 所示。

图 39 参数扫描分析设置

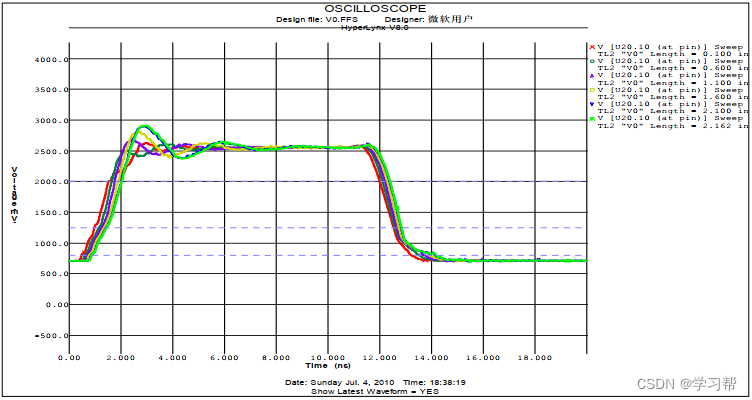

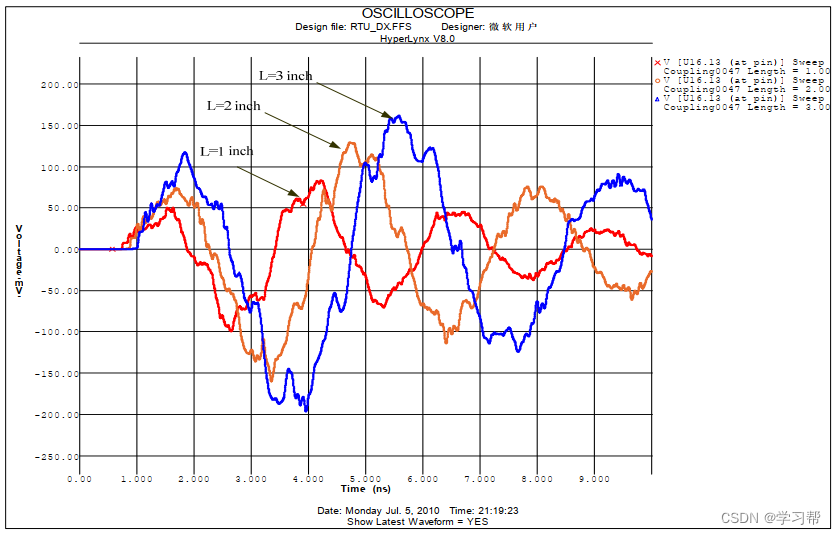

当参数扫描范围设定后,点击 OK 并。然后点击 Run Sweeps,弹出扫描分析结果,如图 40 所示。从图中可以看出随着布线长度的减小,信号过冲明显下降。

图 40 参数扫描分析结果

10 模型文件结构及模型创建

Hyperlynx 中支持的信号完整性模型有*.SnP 模型(即 S 参数模型), SPICE模型、 MOD 模型、 IBIS 模型和 EBD 模型等。在此以 IBIS 和 MOD 这两种最常用的模型为例,简要说明其模型的结构和特点及创建过程。

10.1 .MOD 模型

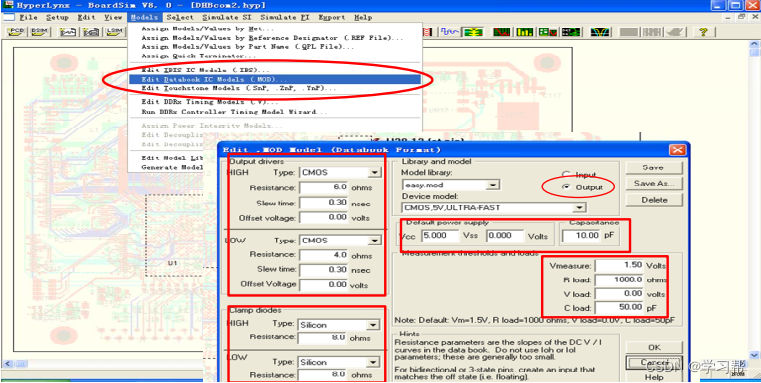

MOD 模型是由 Mentor Graphics 公司定义的一种简单信号完整性模型, 是单一特定管脚的驱动器或者接收模型,只能用于赋予某一管脚,不能适用于整个器件。点击 MODELSÆEDIT DATABOOK IC MODELS 弹出如下界面。

图 41 MOD 驱动模型模型编辑

如图 41 所示,输出驱动器的 MOD 模型参数有四类:

输出特性( ouput driver) :包括驱动输出级所用工艺技术类型(如晶体管、 CMOSFET 等)、高低逻辑电平状态下的直流输出电阻、边沿时间、驱动内部的偏置电压;

钳位二极管特性: 包括二极管的类型、直流电阻( V-I 曲线斜率);

器件供电电压和输出电容: 包括 VCC 和 VSS 的直流电压值以及驱动总的输出电容值;

测试门限和负载: 指以上各种数据在何种测试条件得到的,具体包括测试的参考电压、输入电压、直流负载、交流负载参数。

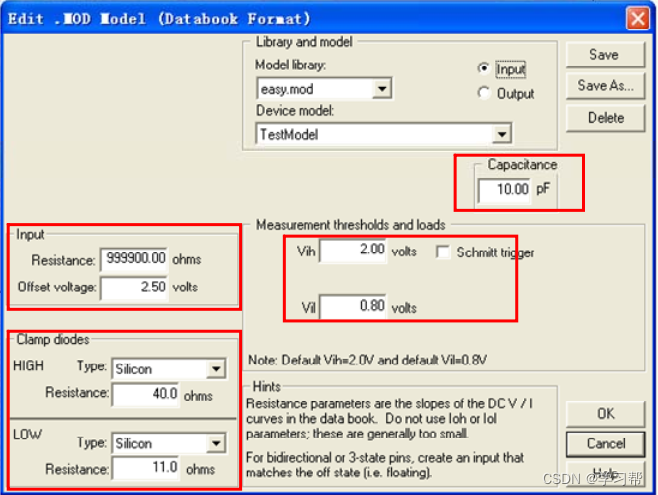

图 42 接收器 MOD 模型编辑

接收器的 MOD 模型参数如图 42 所示,也有四类参数:

输入特性( input) :包括输入电阻、接收器输入级的等效偏置电压; 钳位二极管特性: 包括二极管的类型、直流电阻( V-I 曲线斜率);

输入电容: 接收器总的输入电容值;

测试门限和负载: 输入为逻辑高电平的最低门限值和输入为逻辑低电平的最高门限值。

以上各种 MOD 模型参数一般可以在器件的 DATASHEET 上 DC 特性和 AC特性信息中找到。

10.2 IBIS 模型

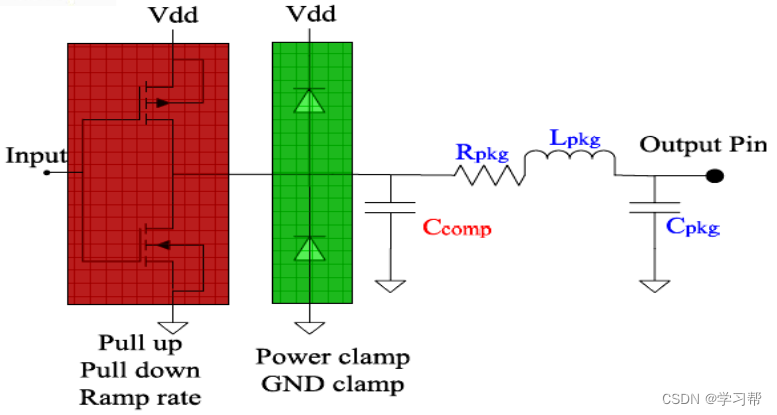

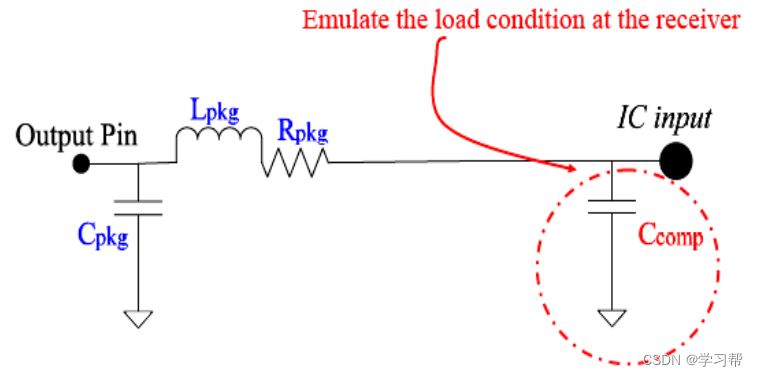

IBIS 模型是一种信号完整性模型,模型内有详细的数据来描述驱动器或者接收器的行为特性,如上升沿过程、管脚封装的影响、逻辑电压值等。

图 43 驱动器的 IBIS 等效模型

图 44 接收器的 IBIS 等效模型

IBIS 文件格式如下:

Keyword

[IBIS ver]

[File name]

[File Rev]

[Date]

[Source]

[Notes]

[Disclaimer]

[Copyright]

[Component]

[Manufacturer]

[Package]

[Pin] signal_name model_name

[Model]

[Voltage Range]

[Pullup]

[Pulldown]

[Ramp]

[Rising Waveform]

[Falling Waveform]

[End]

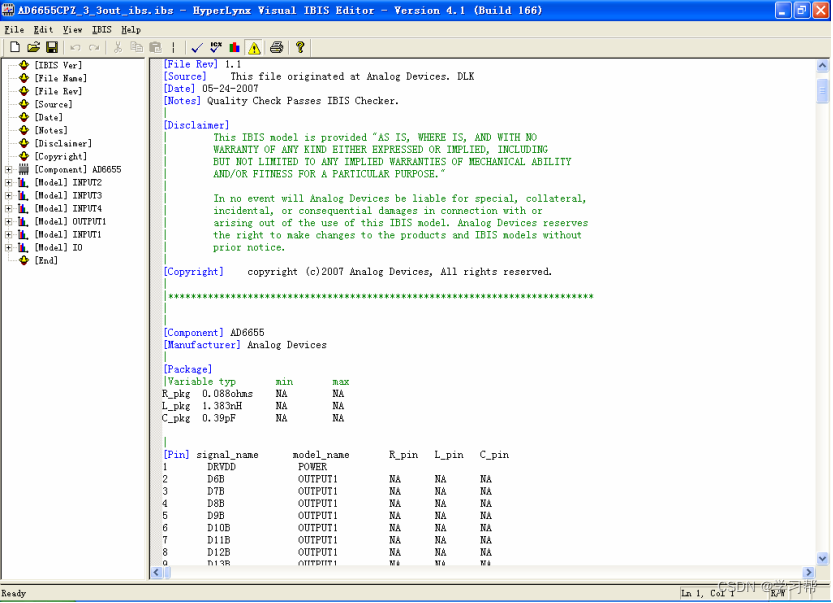

图 45 打开 IBIS 文本编辑器

如图 45 在 Edit 菜单栏下启动 IBIS 文本编辑器, 并打开任意一个 IBIS 文件,结果如图 46 所示。从文本编辑器的左边导航栏可以清楚的看到该文件中包含了几个器件以及每个器件的管脚模型映射等信息。由于 IBIS 文件中需要有大量的V-I 数据和 V-t 数据来描述器件的模型行为,而这些数据一般是由实测或者由SPICE 仿真得到。故对整个器件进行 IBIS 文件建模难度很大,一般只能由器件厂商提供。

图 46 IBIS 文件结构显示

11 仿真实例

下面以一块具体的 PCB 为例,来说明如何使用 Hyperlynx 进行板级的信号完整性分析。

11.1 导入 PCB、设置叠层

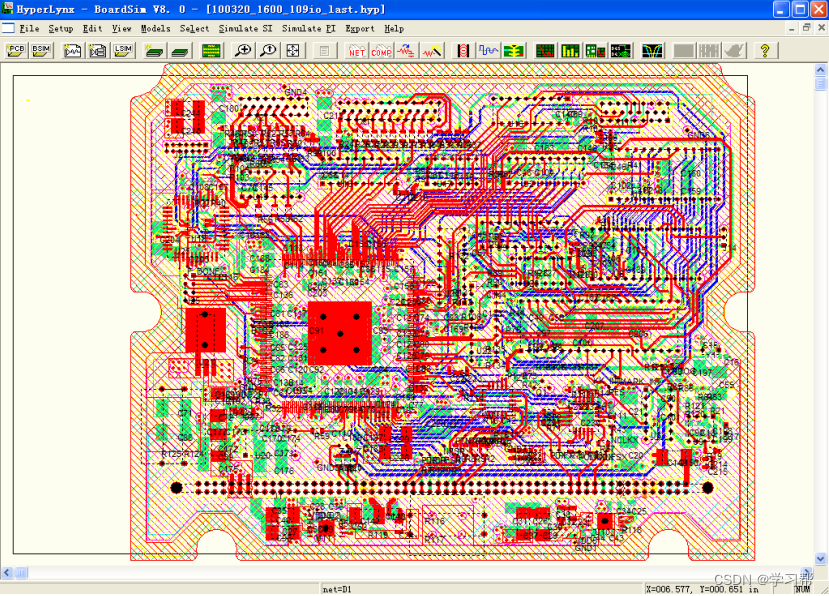

本 PCB 板是一块 Cadence 格式的 PCB 板,可以直接由 Hyperlynx 导入。导入后结果如图 47 所示, 图中各层信号线均以不同颜色表示。 点击叠层设置按钮,进叠层的修改设置,如图 48,将实际的板层厚度、介电常数等信息填入表格中。

图 47 PCB 导入到 Hyperlynx 后显示结果

图 48 修改叠层

11.2 设定电源网络

设定所有电源网络,并为它们赋予直流电压值,如图 49 所示。

图 49 赋予电源网络直流电压

10.3 器件模型赋值

对于无源器件如电阻和电容采用.QPL 文件进行赋值, 对于集成 IC 采用.REF文件进行模型赋值。

图 50 使用 QPL 文件为无源器件赋值

图 51 使用 REF 为 IC 器件赋模型

12 仿真分析结果

- ZTOB 逻辑信号过冲分析

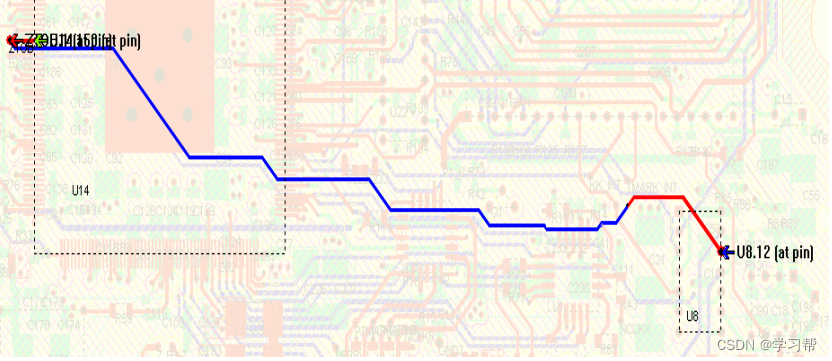

图 52 所示是 FPGA( U14)和逻辑芯片( U8)之间的互联网络( ZTOB),信号由逻辑器件输出至 FPGA。将 U8.12 设置为驱动输出, U14.150 设置为接收器输入端。

图 52 ZTOB 信号网络

点击菜单 EXPORTÆNET TOÆFREE FORM SCHEMATIC, 得到如图 53 所示的模型。

图 53 ZTOB 信号网络导出模型

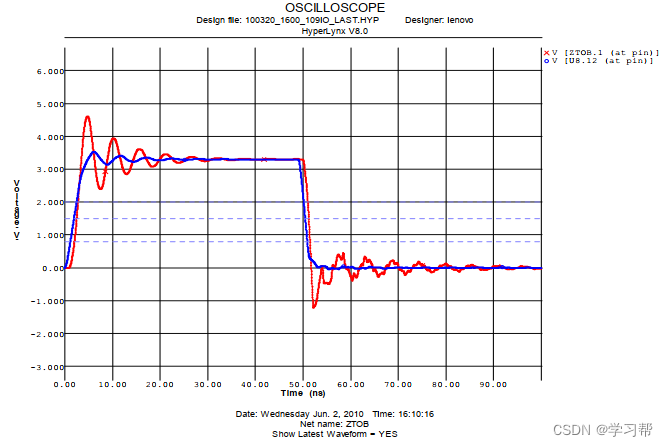

点击 SI 交互式仿真快捷按钮![]() ,仿真类型设置振荡模式,频率为 10MHz。图 54 是 ZTOB 信号仿真结果,其中红色的是驱动输出端信号,蓝色是 FPGA 接收端信号。由图可以明显看出上升沿过冲为 1.3V,下降沿过冲为 1.19V,信号质量很差,过冲很严重。

,仿真类型设置振荡模式,频率为 10MHz。图 54 是 ZTOB 信号仿真结果,其中红色的是驱动输出端信号,蓝色是 FPGA 接收端信号。由图可以明显看出上升沿过冲为 1.3V,下降沿过冲为 1.19V,信号质量很差,过冲很严重。

图 54 ZTOB 信号过冲

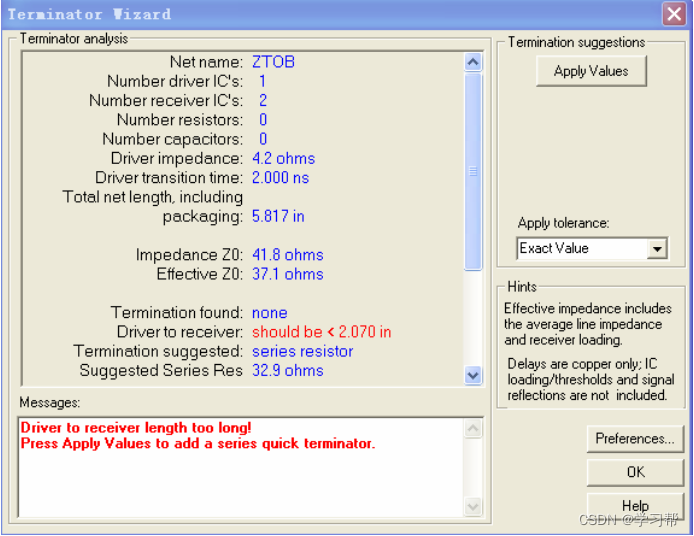

针对信号过冲较为严重情况,采取端接措施进行改进。利用终端向导,可以发现,驱动端到接收端建议的走线长度应该小于 2in,或者串入 32 欧姆左右的电阻,如图 55 所示。

图 55 端接向导

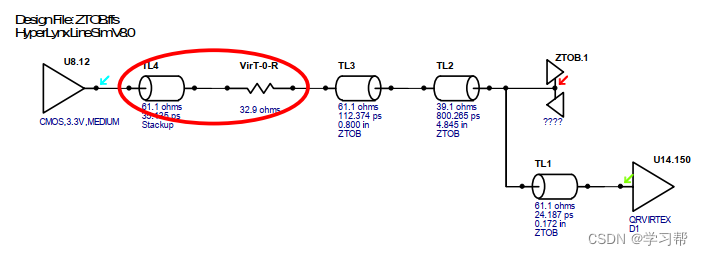

改进后的 PCB 布线网络导出模型如图 56 所示。

图 56 端接改进示意图

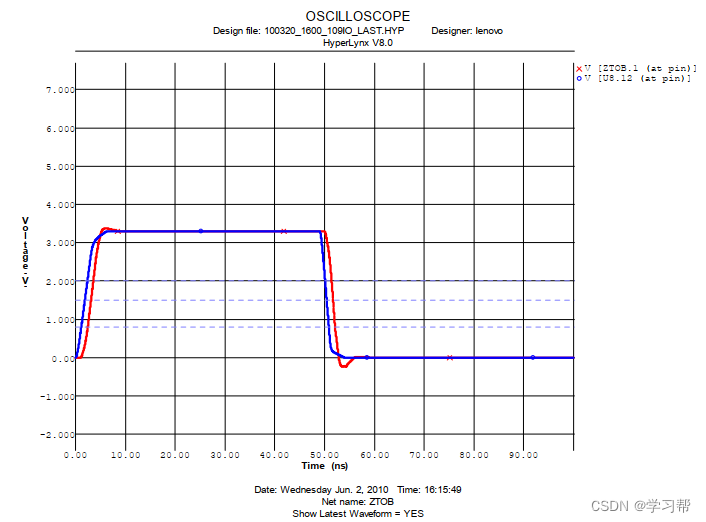

改进后的上升沿过冲为76.83mV,下降沿过冲为 239.4mV;但时钟信号的边沿变缓了。

图 57 采取端接措施后

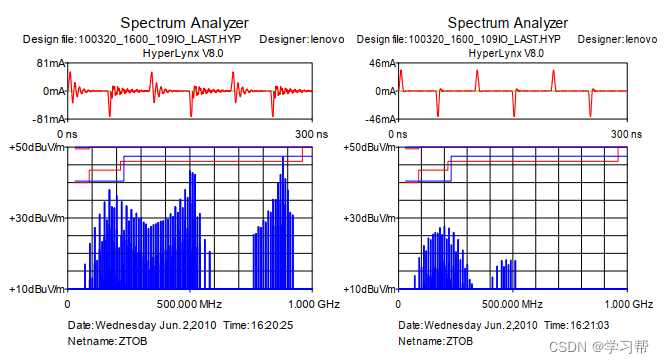

下图为采取端接措施前、后辐射频谱对比情况,由图可以明显看到端接后的辐射大大减小了。

图 58 端接为前的辐射频谱 图 59 端接后的辐射频谱

- RTU_DX 与 SELF_CLKX 网络间串扰分析

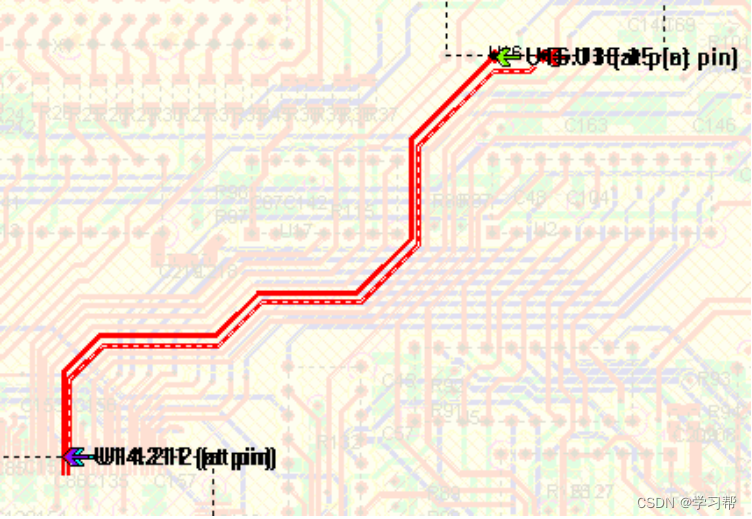

下图是相邻较近的两个信号网络。将 RTU_DX 信号网络设置为受害网络并选中,然后点击![]() 按钮,将在 RTU_DX 信号网络周围出现攻击线(虚线显示,即 SELF_CLKX 网络)。

按钮,将在 RTU_DX 信号网络周围出现攻击线(虚线显示,即 SELF_CLKX 网络)。

图60 相互干扰的两个网络

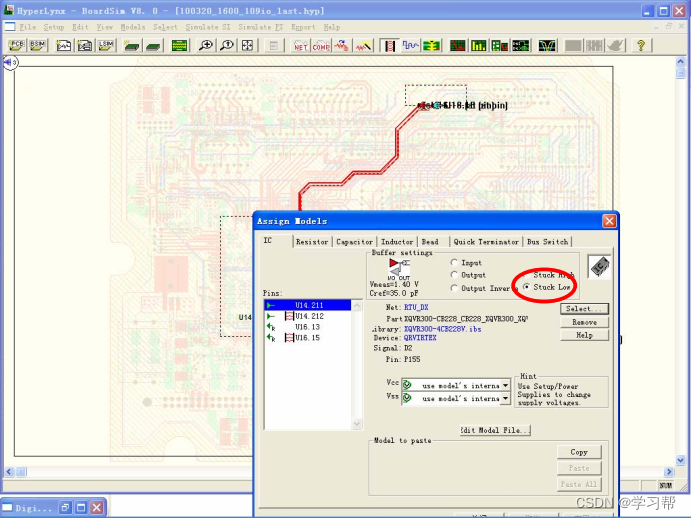

点击 COMP 按钮 ![]() ,将受害线上的驱动输出端管脚设置为 Stuck Low 状态,接收端管脚设置为输入状态;将攻击线上的器件管脚设置为正常工作状态,具体设置如图 61 所示。

,将受害线上的驱动输出端管脚设置为 Stuck Low 状态,接收端管脚设置为输入状态;将攻击线上的器件管脚设置为正常工作状态,具体设置如图 61 所示。

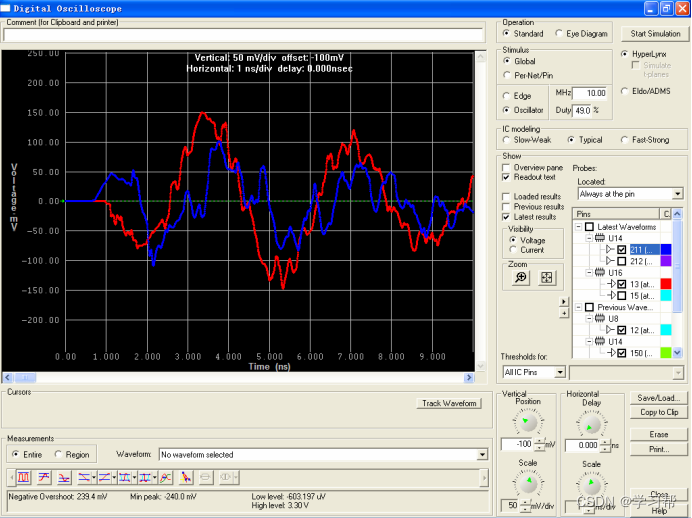

图 62 是受害线上的串扰电压值,由图观察可知最大串扰噪声达到 150mV左右。

图 61 串扰仿真设置

图 62 串扰仿真结果

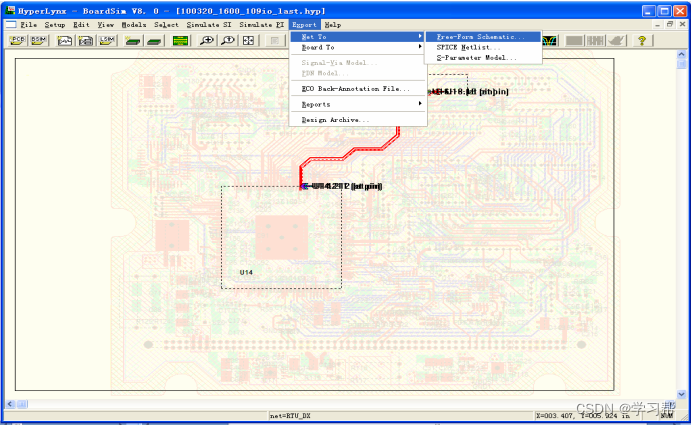

将其导入到 LineSim 中进行前仿真优化分析。选中待仿真的网络(受害网络),点击 EXPORTÆNET TO FREE FORM SCHEMATIC 菜单,如图 63 所示。

图 63 将 NET 导出到前仿真中

弹出如下所示的界面:

图 64 导出设置

最终弹出如下界面:

图 65 串扰模型导出

点击![]() 快捷按钮,对布线长度进行扫描分析。扫描范围为 1 inch~3 inch,步长为 1 inch,具体设置如图 66 所示。

快捷按钮,对布线长度进行扫描分析。扫描范围为 1 inch~3 inch,步长为 1 inch,具体设置如图 66 所示。

图 66 长度扫描设置

长度扫描分析结果如图 67 所示,由结果可知当布线长度减小到 2 inch 以下时串扰基本可以控制在 100mV 以下。

图 67 布线长度扫描情况下的远端串扰对比

点击![]() 快捷按钮,对布线间距进行扫描分析,扫描范围为 11mil~25mil,步进为 5mil,具体设置如图 68 所示。

快捷按钮,对布线间距进行扫描分析,扫描范围为 11mil~25mil,步进为 5mil,具体设置如图 68 所示。

图 68 布线间距扫描设置

布线间距扫描分析结果如图 69 所示,由结果可知当布线间距增加到 21mil以上时串扰基本可以控制在 100mV 以下。

图 69 布线间距扫描分析

3620

3620

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?