目录

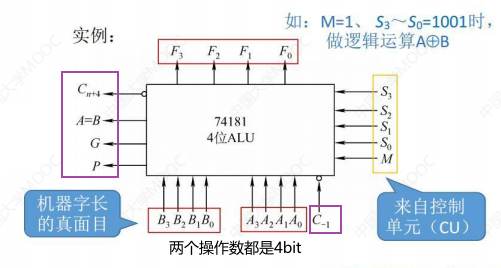

算数逻辑单元ALU

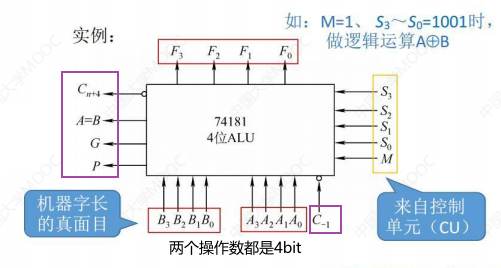

ALU:1.输入信号A0~A3、B0~B3

2.输出信号F0~F3

3.控制信号S0~S3

4.M表示执行的 算术运算/逻辑运算

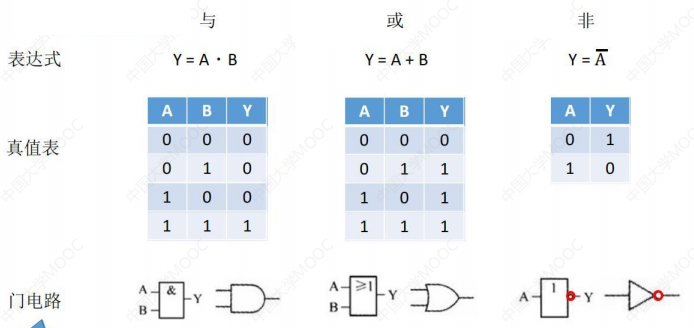

ALU最基本的逻辑运算(逻辑表达式是对电路的数字化描述)

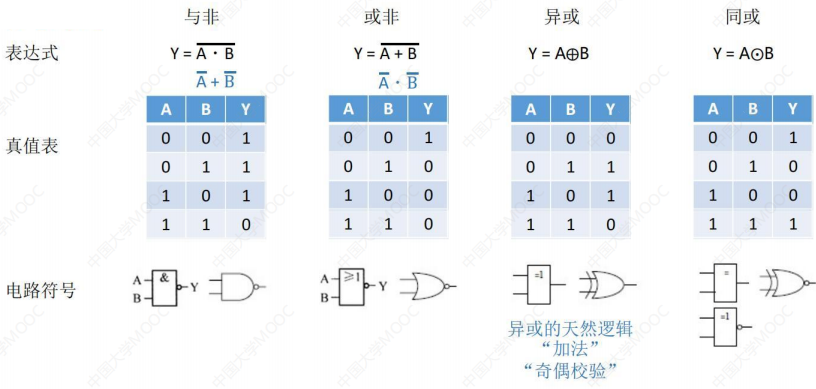

ALU复合逻辑运算(逻辑表达式是对电路的数字化描述)

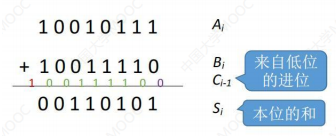

加法器的实现(异或运算实现加法器)

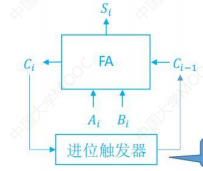

一位全加器

对应ALU两个输入信号和来自低位的进位

串行加法器(利用一位全加器逐位相加实现加法)

串行加法器:只有一个全加器,数据逐位串行送入加法器中进行运算,一次只能运算一位,效率低

进位触发器:保存寄存进位信号

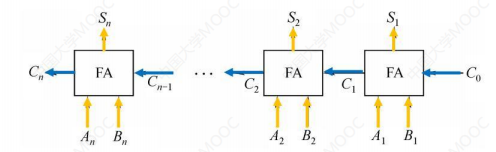

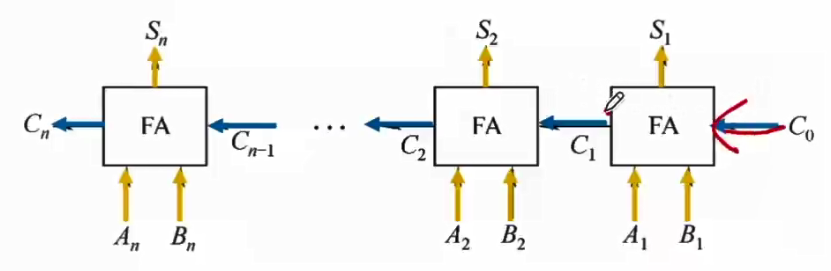

并行加法器(对串行加法器的改进)

串行进位的并行加法器

串行进位的并行加法器:把n个全加器串接起来,可以对两个n位数的相加

缺点:AB两个操作数很快运算,但进位需要等(多米洛骨牌)

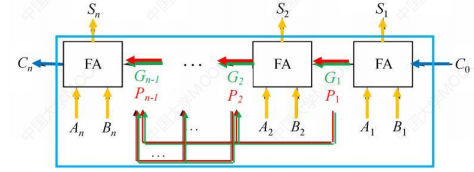

并行进位的并行加法器(对串行进位加法器的优化)

C1 = A1 * B1 +(A1 ⊕ B1)* C0 ①

C2 = A2 * B2 +(A2 ⊕ B2)* C1 ②

C3 = A3 * B3 +(A3 ⊕ B3)* C2 ③

C4 = A4 * B4 +(A4 ⊕ B4)* C3 ④

化简Gn = An * Bn Pn = An ⊕ Bn

把C1带入C2,C2带入C3,C3带入C4最后得

C1 = G1 + P1 * C0 ①

C2 = G2 + P2 * (G1 + P1 * C0 ) ②

C3 = G3 + P3 * ( G2 + P2 * (G1 + P1 * C0 )) ③

C4 = G4 + P4 * ( G3 + P3 * ( G2 + P2 * (G1 + P1 * C0 ))) ④

观察G1和P1在C1、C2、C3、C4的运算都会用到,减少重复计算

观察G2和P2在C2、C3、C4的运算都会用到,减少重复计算

观察G3和P3在C3、C4的运算都会用到,减少重复计算

C4 = G4 + P4 * ( G3 + P3 * ( G2 + P2 * (G1 + P1 * C0 ))) ④

化简得

C4 = G4 + P4 G3 + P4 P3 G2 + P4 P3 P2 G1 + P4 P3 P2 P1 C0

而Gn = An * Bn Pn = An ⊕ Bn正是我们输入的运算数,C0也是已知的,因此可以在从右到左第4个加法器直接算出C4的值,每个加法器的进位几乎是同时产生的,不需要等待后面的进位才能运算,对ALU而言

可以同时支持4位 加 4位的运算

文章详细介绍了算数逻辑单元ALU的基本结构和功能,包括其输入、输出和控制信号。接着讨论了加法器的实现,从一位全加器到串行加法器,再到并行加法器和优化后的并行进位加法器,强调了如何通过异或运算和并行处理提高运算效率。

文章详细介绍了算数逻辑单元ALU的基本结构和功能,包括其输入、输出和控制信号。接着讨论了加法器的实现,从一位全加器到串行加法器,再到并行加法器和优化后的并行进位加法器,强调了如何通过异或运算和并行处理提高运算效率。

2077

2077

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?