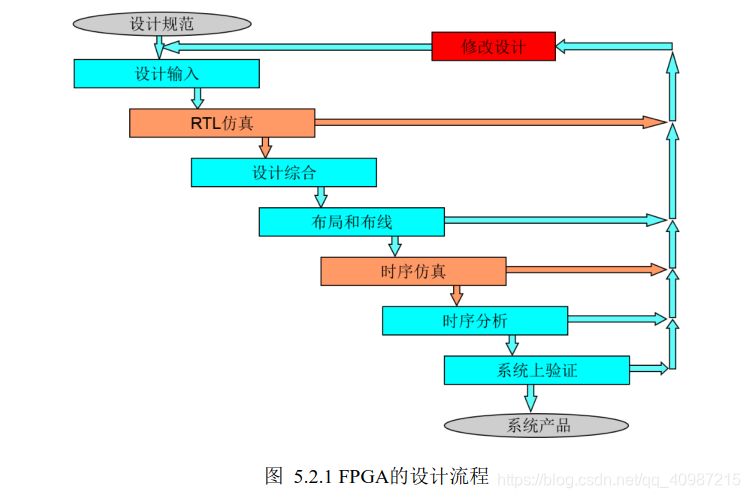

1. FPGA设计流程如下:

在设计输入之后,设计综合前进行RTL级仿真,称为综合前仿真,也称为前仿真或功能仿真。前仿真也就是纯粹的功能仿真,主旨在于验证电路的功能是否符合设计 要求,其特点是不考虑电路门延迟与线延迟。在完成一个设计的代码编写工作之后,可以直接 对代码进行仿真,检测源代码是否符合功能要求。这时,仿真的对象为HDL代码,可以比较直 观的观察波形的变化,在设计的最初阶段发现问题,节省大量的精力。

在布局布线后进行的仿真称为布局布线后仿真,也称为后仿真或时序仿真。时序仿真可以 真实地反映了逻辑的时延与功能,综合考虑电路的路径延迟与门延迟的影响,验证电路能否在 一定时序条件下满足设计构想的过程,是否存在时序违规。

2. ModelSim使用

ModelSim的使用主要分为两种情况,第一种就是 直接使用ModelSim软件进行仿真,也就是手动仿真;第二种情况就是通过其它的EDA工具如 Quartus II调用Modelsim进行仿真,这种情况也就是我们通常所说的自动仿真或者联合仿真。

不管是手动仿真还是自动仿真,它们都遵循以下5个步骤:

(1) 新建工程。

(2) 编写Verilog文件和Testbench仿真文件。 (3) 编译工程

(4) 启动仿真器并加载设计顶层

(5) 执行仿真。 当我们执行了仿真以后,ModelSim软件会根据我们的设计文件和仿真文件生成波形图,最

后,我们观察波形并判断设计的代码功能是否正确。前仿真完成以后,接下来我们就可以根据 需要进行后仿真了,后仿真与前仿真的步骤大体相同,只不过中间需要添加仿真库、网表和延 时文件等步骤。

3.模块结构

如果这个条件是时钟的上升沿或下降沿,那么这个硬件模型就是一个触发器;如果这个条件是某一信号的高电平或低电平,那么这个硬件模型就是一个锁存器;

每个模块的Verilog程序包括4个部分:

- 端口定义

- IO说明

- 内部信号声明(reg [23:0] counter;)

- 功能定义

在IO说明时如果未定义端口的数据类型,那么默认为wire类型(input a,b;)。

4.信号通过模块端口在模块之间的传递(例化)

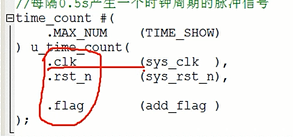

左边是子模块信号,右边是顶层模块信号。

5.状态机

- 概念:

- 在有限个状态之间按一定规律转换的时序电路。

- 有限状态机,简称"FSM”。

2. 模型:

- Moore型状态机:下一状态只由当前状态决定,即次态=f(现状,输入),输出=f(现状);

- Mealy 型状态机:下一状态不但与当前状态有关,还与当前输入值有关,即次态=f(现状,输入),输出=f(现状,输入);

3. 设计:(四段论)

- 状态空间定义;(parameter play =4'b0001 ;)

- 状态跳转;(时序逻辑电路)

- 下个状态判断;(组合逻辑)

- 各个状态下的动作;(组合逻辑,最后加一级时序逻辑电路)

- 注意:If / else ,case / default 要配对以避免latch锁存器的产生,即毛刺的产生。

7571

7571

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?