VLSI数字信号处理系统——第五章展开

作者:夏风喃喃

参考:

(1) VLSI数字信号处理系统:设计与实现 (美)Keshab K.Parhi/著

(2) socvista https://wenku.baidu.com/u/socvista?from=wenku

一.引言

展开:展开用于产生一个新的程序来描述原有程序的多次迭代。更具体的说,以展开因子

J

J

J展开一个DSP程序,就会产生一个以原程序连续迭代

J

J

J次的新程序。在保证功能不变的提前下,可以对内部的数据存储和计算流程进行重新的安排,以便达到各个性能指标之间的折中。

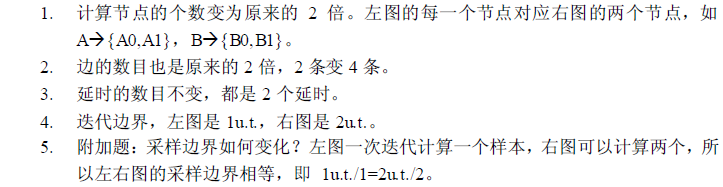

展开后的DFG,迭代边界为原始的

J

J

J倍,采样边界不变,都不比原来的小,而且还消耗了更多的计算节点和边。但需注意,此处为边界,是DSP能达到的最快的运行速度和最大的吞吐率。对于任意的一个迭代DFG,一般是不能达到这个极限速度的,展开就可以消除一些制约系统运行速度的限制,使得新的DFG运行速度逼近或者完全达到这个极限。

二.一种展开算法

两步实现J阶展开算法:

1)节点的

J

J

J倍复制。对于原始DFG中任意一个节点U,在新的DFG中对应

J

J

J个新的节点,分别记为

U

0

,

U

1

,

…

.

,

U

J

−

1

U_0,U_1,….,U_{J-1}

U0,U1,….,UJ−1。

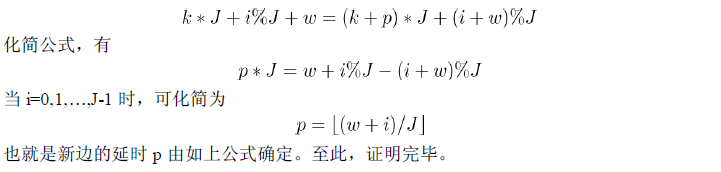

2)对原始DFG中每一条有

w

w

w延迟的边

U

→

V

U→V

U→V,画

J

J

J条有

⌊

i

+

w

J

⌋

\lfloor\frac{i+w}{J}\rfloor

⌊Ji+w⌋延迟的

U

i

→

V

(

i

+

w

)

%

J

U_i→V_{(i+w)\%J}

Ui→V(i+w)%J边,

i

=

0

,

1

,

…

,

J

−

1

i=0,1,…,J-1

i=0,1,…,J−1。

两步实现J阶展开算法的原理(理解):

三.展开的属性

性质一:展开算法保持DFG中的延时数目不变。

性质二:原始DFG中延时为

w

l

w_l

wl 的环路

l

l

l的

J

J

J阶展开,得到展开后的DFG中的

g

c

d

(

w

l

,

J

)

gcd(w_l,J)

gcd(wl,J)(gcd为最大公约数)个环路,

g

c

d

(

w

l

,

J

)

gcd(w_l,J)

gcd(wl,J)个环路中的每个环路包含

w

l

/

g

c

d

(

w

l

,

J

)

w_l/gcd(w_l,J)

wl/gcd(wl,J)个延时以及环路

l

l

l中出现的每个节点的

J

/

g

c

d

(

w

l

,

J

)

J/gcd(w_l,J)

J/gcd(wl,J)个拷贝。

性质二告诉我们三个内容:

- 一个环路展开会得到若干个环路,也就是说环路展开后得到的仍然是环路。

- 原始环路的延时会平分到新的环路中。

- 对于任一个原始节点U的新复制得到的J个节点也会平分到新的环路中。

性质三:展开一个迭代边界为 T ∞ T_{\infty} T∞的DFG,会得到一个迭代边界为 J ∗ T ∞ J*T_{\infty} J∗T∞的 J J J阶展开DFG。

虽然展开后系统的迭代边界扩大 J J J倍,但是由于新系统可以同时处理 J J J个样本点,所以采样边界为 J ∗ T ∞ / J = T ∞ J*T_{\infty}/J=T_{\infty} J∗T∞/J=T∞,也就是说展开不改变系统的极限吞吐率。

四.关键路径、展开和重定时

当

w

≥

J

w≥J

w≥J,也就是展开阶数

J

J

J不大于路径延时

w

w

w时,将不会导致更长的关键路径出现。

性质四:考虑原始DFG中延时为w的路径,当w<J 时,该路径的J 阶展开将得到J-w个无延时路径和w个延时为1的路径。

性质四给出了原始DFG中延时为w的边展开后得到新边中,延时为0的新边数目为J-w条,如果不想这些边成为关键路径中的边,就必须限制J-w<=0,也就是J<=w。

性质五:任何通过重定时J阶展开DFG得到的

G

J

G_J

GJ所能得到的可行时钟周期,都可以通过直接对原始DFG的G重定时和以J为展开因子的展开来得到。先展开再重定时和先重定时再展开存在一一对应关系,如果使用先展开后重定时得到一个新的DFG,那么这个DFG肯定可以通过某种重定时再展开来得到。

五.展开的应用

1.采样周期的缩短

从迭代边界的理论中可知,即使经过重定时,一个DFG的实际运行速度往往没有达到其理论上可以到达的极限速度,往往是因为存在以下2个方面的限制因素:

- DFG中存在某些节点计算时间大于迭代边界。

- 迭代边界不是整数时间单位。

- DFG中存在某些节点计算时间大于迭代边界且迭代边界不是整数时间单位。

第一个限制,存在一个节点的计算时间大于迭代边界 T ∞ T_\infty T∞,那么该DFG不可能以迭代周期来运行,否则这个节点可能不能在一个周期内完成计算任务。由展开性质三会得到一个迭代边界为 J ∗ T ∞ J*T_\infty J∗T∞的J阶展开DFG,通过展开增大新DFG的迭代边界,就可以去除这个限制。。如果新DFG能以迭代边界为周期运行,虽然新DFG迭代边界比原始DFG迭代边界大,但是新DFG可以同时处理多个(J个)样本,采样边界不变,也就是说新DFG吞吐率达到理论最大。

为了解除第一个限制因素,只需进行 ⌈ ( t u / T ∞ ) ⌉ \lceil(t_u/T_\infty)\rceil ⌈(tu/T∞)⌉阶展开即可,其中 t u t_u tu为最耗时的节点计算时间, T ∞ T_\infty T∞为原始DFG的迭代边界。

展开解决限制一,如下图所示:

第二个限制,首先假设DFG中任意节点的计算时间都是整数个单位时间。如果迭代边界不是整数,也就是说以带小数的单位时间为周期驱动系统,这个小数部分的单位时间,对任何一个节点来说都是不足以完成任何任务。因此,实际的运行时钟为整数个单位时间才“可能”是最合理的。

为了解除第二个限制因素,如果关键环路边界的形式为 t l / w l t_l/w_l tl/wl,其中 t l t_l tl和 w l w_l wl互为素数,则应采用 w l w_l wl阶展开。

展开解决限制二,如下图所示:

第三个限制,结合了第一个与第二个限制的解释。

为了解除第二个限制因素,最小展开因子是能使 J ∗ T ∞ J*T_\infty J∗T∞成为整数时J的最小值。

2.并行处理

展开是构造并行处理电路的方法之一。

(1) 字级并行处理:

字级并行处理,指的是以字为处理单位进行展开。比如图19中,假设输入x就是一个w位的字,在字的层次对图19左图DFG进行J阶展开(J=3),得到一个字级3路并行处理DFG如右图示。

(2) 位级并行处理(重点在开关边的展开):

- 位串行处理(bit-serial processing):一个时钟周期处理一位,一个完整的字在W个时钟周期内处理完。

- 位并行处理(bit-parallel processing):一个W位的字在一个时钟周期内处理完成。

- 数字串行处理(digital-serial processing):一个时钟周期处理N位,一个字在W/N个时钟周期内处理完成。参数N称为数字尺寸。

以加法器为例,图21为位级并行处理的加法器:

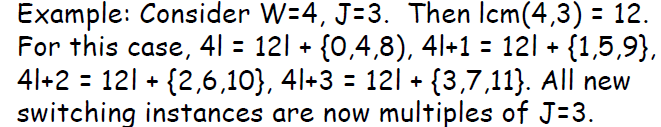

如图22所示,一个4位的串行加法器。图中大方框内的Bit-serial adder其实就是一个全加器,两个输入端和一个进位输入端,一个输出端和一个进位输出端。开始计算,输入a0和b0,进位输入为0,输出s0,并将进位输出保持到D中;接下来,输入a1和b1,进位输入为D中保持的值,输出为s1,且进位输出又保持到D中;等等。全加器的进位输入端在每一个4l+0周期总是输入0值,而在4l+1,+2,+3周期输入寄存器D中的值。对该位串行DFG进行展开就能得到位并行或者数字串行系统。

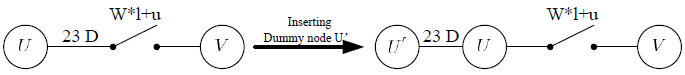

(重点)开关支路的展开方法:

预处理:如图23 示的开关支路,其中 W ∗ l + u W*l+u W∗l+u表明在第 W ∗ l + u W*l+u W∗l+u次迭代开关闭合,其他次迭代开关断开,W 为字长,l为自然数 ,u=0,1,…,W-1。如果开关支路包含延时,可以插入一个哑巴节点从而改造成没有延时的开关支路,如下图示,U’和V之间的支路就符合通用形式。

两个基本假设: - 字长W是展开因子J的倍数,即W=W’J。 (若W不是J的倍数,可以修改开关闭合时刻如下图所示,再实现开关展开)

- 所有进出开关的边都不包含延时。

展开步骤:

- 将原DFG闭合时刻改写为: W l + u = J ( W ′ l + ⌊ u / J ⌋ ) + ( u % J ) Wl+u=J(W'l+\lfloor u/J \rfloor)+(u\%J) Wl+u=J(W′l+⌊u/J⌋)+(u%J)

- 展开后的图中,从节点 U u % J U_{u\%J} Uu%J到节点 V u % J V_{u\%J} Vu%J画一条不带延时的边,它在 ( W ′ l + ⌊ u / J ⌋ ) (W'l+\lfloor u/J \rfloor) (W′l+⌊u/J⌋)时刻闭合。

展开的例子如下图24、25、26:

六.结论

展开变换可以揭示隐藏在用DFG描述数字信号处理系统中的并发性。因此,展开技术可以用来在无法细粒度与迭代周期非整数情况下提高采样周期。展开可以用来生成高速低功耗应用中的字级与位级并行型架构。

679

679

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?