A 20GS/s 8b Time-Interleaved Time-Domain ADC with Input-Independent Background Timing Skew Calibration

作者:Minglei Zhang, Yan Zhu, Chi-Hang Chan, Rui P. Martins

机构:State-Key Laboratory of Analog and Mixed-Signal VLSI, IME, University of Macau, Macao, China

期刊:Symposium on VLSI Circuits

时间:2021

摘要

本文介绍了一种基于直接时间估计的时间交织(TI)ADC背景定时偏差校准方法,以实现与输入无关的快速收敛特性。无论24个校准周期的校准输入条件如何,它在奈奎斯特输入时抑制20GS/s 8×TI-ADC低于‒50dB的定时杂散。8b时域TI-ADC实现91.3fJ/迭代步长的 F o M W a l d e n FoM_{Walden} FoMWalden和>16GHz带宽。

关键词

背景,时间偏斜校准,时域ADC,时间交错ADC,输入无关

文章目录

一. 介绍

对于10GS/s以上的中分辨率ADC,时间交织(TI)架构是不可避免的。与偏移和增益失配相比,定时偏差校准具有相当大的挑战性,因为其误差随输入频率和振幅的增加而增加。使用PVT跟踪能力,背景定时倾斜校准更可靠,同时不会中断转换,但通常会限制输入条件。现有技术[1]要求宽范围的固定输入,而[2]和[3]使输入条件变得足够繁忙。但是,额外的专用通道[2]会导致时变ADC输入阻抗,闪存ADC[3]会限制整体转换速度。嵌入式DAC[4]通过在内部生成校准信号来避免外部输入,但更换校准通道会定期干扰TI-ADC输入条件的一致性。本工作通过时间比较直接提取子ADC采样时钟的定时漂移,开发了一种与输入无关的背景定时偏差校准,使得校准与ADC输入路径及其量化信息完全解耦。在具有奈奎斯特输入的20GS/s TI-ADC中,所提出的技术在24k样本中抑制了低于‒50dB的定时杂散。

二. 校准细节和ADC架构

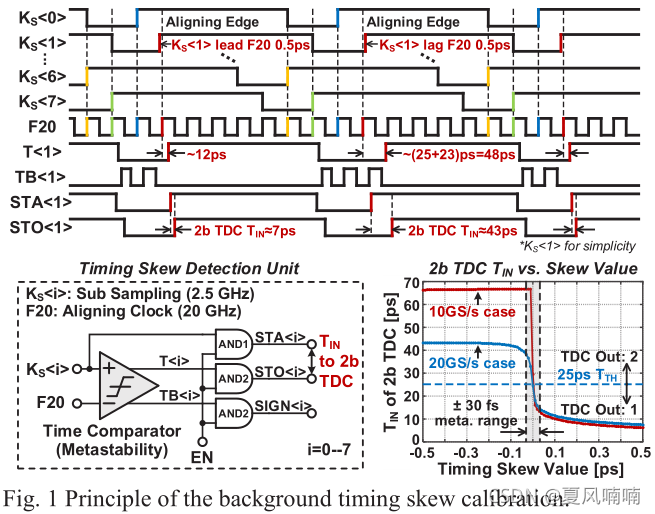

图1示出了直接基于时间的时钟偏移估计的原理,其目的是通过定时比较将子ADC的所有采样时钟(

K

S

<

i

>

K_S<i>

KS<i>,i=0-7,2.5GHz)对准全局时钟(

F

20

F20

F20,20GHz)。当

K

S

<

i

>

K_S<i>

KS<i>=0时,其对应的时间比较器的输出为

T

<

i

>

T<i>

T<i>=0。在

K

S

<

i

>

K_S<i>

KS<i>的上升沿,如果它领先于F20的上升沿,则时间比较器延迟(~ 12fs@0.5ps领先时间)后,

T

<

i

>

T<i>

T<i>立即变高。相反,

T

<

i

>

T<i>

T<i>在

F

20

F20

F20的下一个下降沿处,另一个时间比较器延迟(~ 23fs@0.5ps滞后时间)后给出高值。这两种情况下的比较器延迟因初始条件不同而不同。根据图1,

K

S

<

i

>

K_S<i>

KS<i>(≈

F

20

F20

F20)上升沿和

T

<

i

>

T<i>

T<i>之间的时间间隔(≈上述两种情况中的T分别为~ 12ps和~ 48ps)。然后,比较器输出端的与门分别将它们更新为~ 7ps和~ 43ps,从而呈现之后2b TDC的输入(

S

T

A

<

i

>

STA <i>

STA<i>与

S

T

O

<

i

>

STO <i>

STO<i>)时差

T

I

N

T_{IN}

TIN。2b TDC量化与定时歪斜信息相关联的

T

I

N

T_{IN}

TIN以启用自适应歪斜控制。模拟结果(图1)表明,当定时偏差远离时间比较器的±30fs亚稳范围时,2b TDC可以很好地识别具有25ps阈值的偏差极性。此外,为了屏蔽比较器噪声(RMS=7.5fs)以及

K

S

<

i

>

K_S<i>

KS<i>和F20的时钟抖动的影响,2b TDC输出的1000次迭代统计用于单个校准决策。

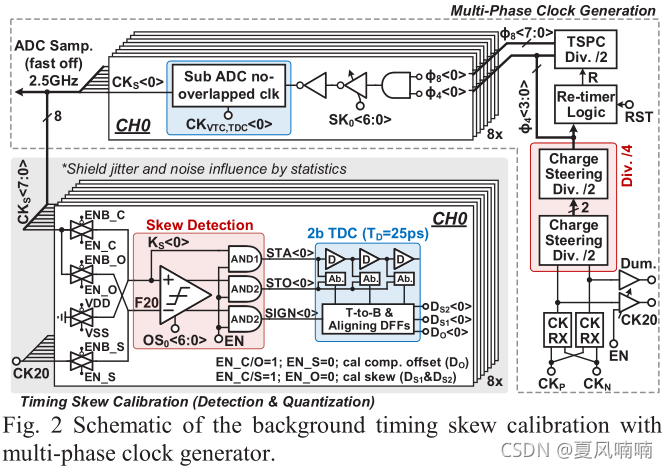

除了噪声之外,时间比较器offset还降低了时钟偏移校准精度,如图2所示,在背景中移除了时钟偏移校准精度。在offset校准期间(

E

N

_

C

/

O

=

1

EN\_C/O=1

EN_C/O=1),ADC采样时钟

C

K

S

<

i

>

CK_S<i>

CKS<i>应用于两个输入比较器,同时还使用

D

O

<

i

>

D_O<i>

DO<i>(=

S

I

G

N

<

i

>

SIGN<i>

SIGN<i>)上的1000个统计信息,以~5fs的步长进行

O

S

i

<

6

:

0

>

OS_i<6:0>

OSi<6:0>的offset反馈校准。在偏斜校准期间(

E

N

_

C

/

S

=

1

EN\_C/S=1

EN_C/S=1),

C

K

S

<

i

>

CK_S<i>

CKS<i>通过2b TDC输出

D

S

2

<

i

>

D_{S2}<i>

DS2<i>和

D

S

1

<

i

>

D_{S1}<i>

DS1<i>上的1000个统计数据与CK20对齐,并以~ 45fs的步长控制偏斜控制代码

S

K

i

<

6

:

0

>

SK_i<6:0>

SKi<6:0>。剩余的误差源,包括添加的开关、布局布线和采样开关,进一步降低了校准精度,使用1.2V电源,厚金属布线和快速断开路径将其最小化。Monte Carlo仿真表明,上述总误差源贡献了~ 100fs 3σ 歪斜值。

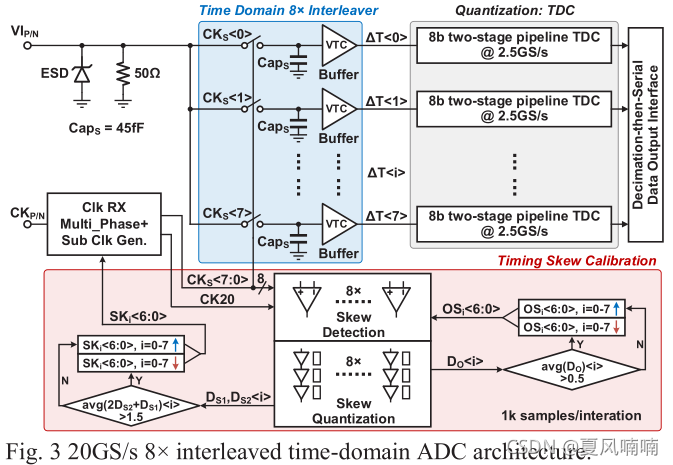

图3显示了20GS/s 8×交错ADC的体系结构,该ADC具有用于高输入带宽的嵌入式VTC缓冲器,与分层电压缓冲器相比,在能效和线性方面具有显著优势。子ADC将450mV输入信号转换为~ ±180ps

Δ

T

<

i

>

ΔT<i>

ΔT<i>,并由8b 2.5GS/s流水线TDC[5]量化。时序偏差检测和量化都是带调谐单元的片上逻辑,而

D

S

2

/

S

1

D_{S2/S1}

DS2/S1和

D

O

D_O

DO的统计逻辑是片外实现。自适应编码控制在前7个周期中采用二进制搜索,然后采用5个单调搜索周期,以加快收敛速度。

三. 测量结果

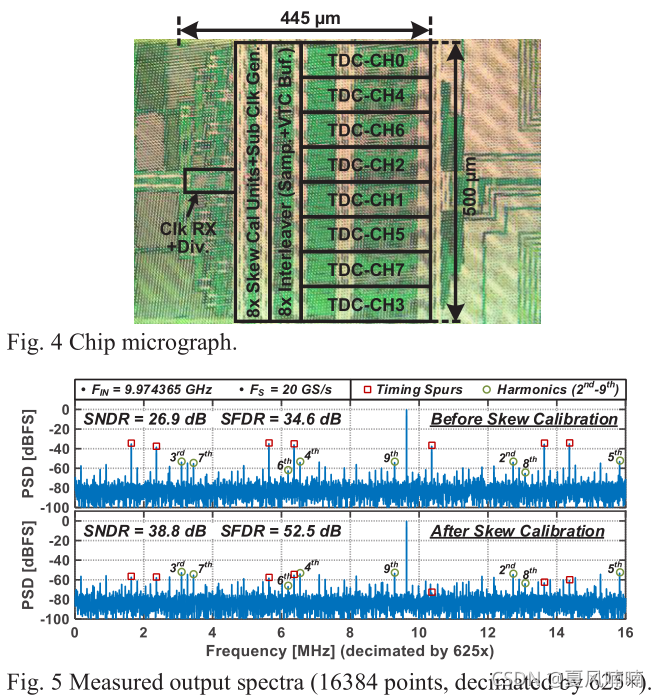

TI-ADC采用65nm CMOS工艺(图4,0.22

m

m

2

mm^2

mm2)。在数字域消除了通道间的offset和增益误差。20GS/s TI-ADC在奈奎斯特输入下实现38.8dB SNDR和52.5dB SFDR,其中时序倾斜校准将最大时序杂散从-34.6dB降低到-55.2dB,如图5所示。

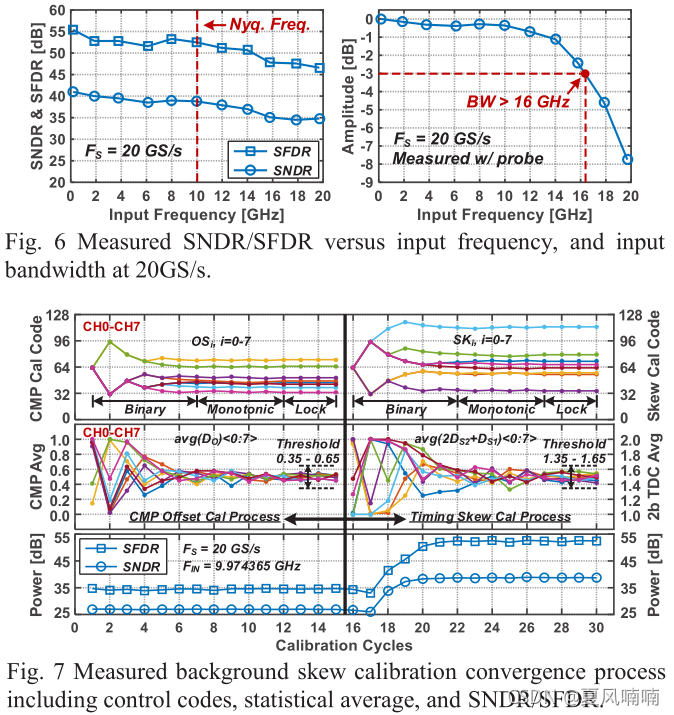

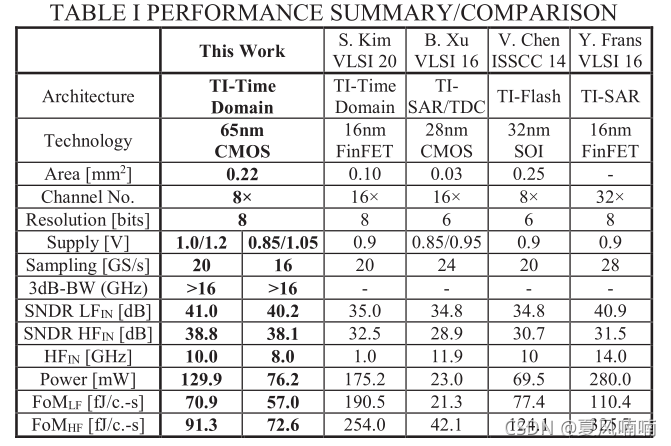

在图6中,使用输入差分探头测量的输入带宽为>16GHz。图7给出了测量到的校正收敛过程,包括时间比较器offset和时序倾斜,倾斜控制码锁定后,2b TDC的平均输出很好地在边界内(进入±30fs亚稳态范围)。所有5个被测芯片在校准后的Nyquist输入都有< -50dB的最大时序杂散。TI-ADC核心从1V电源消耗125.1mW,此外,时序倾斜校准单元从1.2V电源消耗4.8mW,激活率为10%(图2中的EN),这得益于其输入无关和快速收敛的特性。

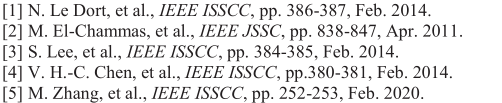

表Ⅰ总结和比较了性能,时域ADC的动态特性也允许在16GS/s下的0.85V转换,同时保持类似的量化精度,但具有更好的FoMs。该工作实现了一个快速和无输入信号的背景时序倾斜校准,精度~ 100fs。

四. 参考文献

866

866

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?