一、系统架构

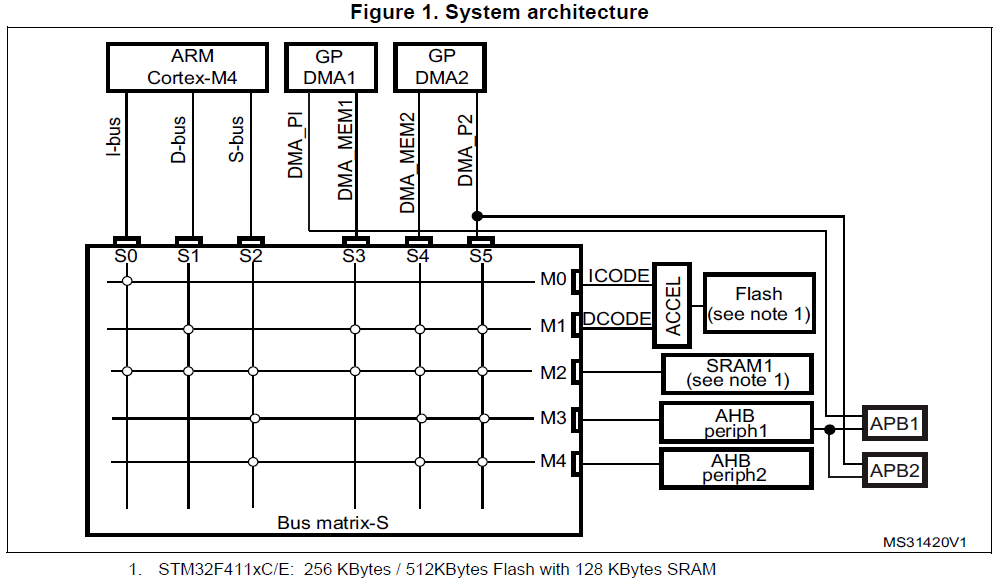

主系统由 32 位多层 AHB 总线矩阵构成,可实现以下部分的互连:

有关AHB总线和APB总线的更多信息请参考博文:

浅析AMBA规范以及AMBA 5 AHB接口和AMBA 3 APB接口

1、六条主控总线:

● Cortex™-M4F 内核 I 总线、D 总线和 S 总线;

● DMA1 存储器总线;

● DMA2 存储器总线;

● DMA2 外设总线。

2、五条被控总线:

● 内部 Flash ICode 总线;

● 内部 Flash DCode 总线;

● 主要内部 SRAM;

● AHB1 外设(包括 AHB-APB 总线桥和 APB 外设);

● AHB2 外设。

借助总线矩阵,可以实现主控总线到被控总线的访问,这样即使在多个高速外设同时运行期间,系统也可以实现并发访问和高效运行。此架构如 Figure 1 所示。

S0:I 总线

此总线用于将 Cortex™-M4F 内核的指令总线连接到总线矩阵。内核通过此总线获取指令。此总线访问的对象是包含代码的存储器(内部 Flash/SRAM)。

S1:D 总线

此总线用于将 Cortex™-M4F 数据总线连接到总线矩阵。内核通过此总线进行立即数加载和调试访问。此总线访问的对象是包含代码或数据的存储器(内部 Flash/SRAM)。

S2:S 总线

此总线用于将 Cortex™-M4F 内核的系统总线连接到总线矩阵。此总线用于访问位于外设 或 SRAM 中的数据。也可通过此总线获取指令(效率低于 I 总线)。此总线访问的对象是内部 SRAM、包括 APB 外设在内的 AHB1 外设、AHB2 外设。

S3、S4:DMA 存储器总线

此总线用于将 DMA 存储器总线主接口连接到总线矩阵。DMA 通过此总线来执行存储器数据的传入和传出。此总线访问的对象是数据存储器:内部 Flash、内部 SRAM 以及 S4 可以额外访问包括 APB 外设在内的 AHB1/AHB2 外设。

S5:DMA 外设总线

此总线用于将 DMA 外设主总线接口连接到总线矩阵。DMA 通过此总线访问 AHB 外设或执 行存储器间的数据传输。此总线访问的对象是 AHB 和 APB 外设以及数据存储器:Flash 储存器和内部 SRAM。

总线矩阵

总线矩阵用于主控总线之间的访问仲裁管理。仲裁采用循环调度算法。

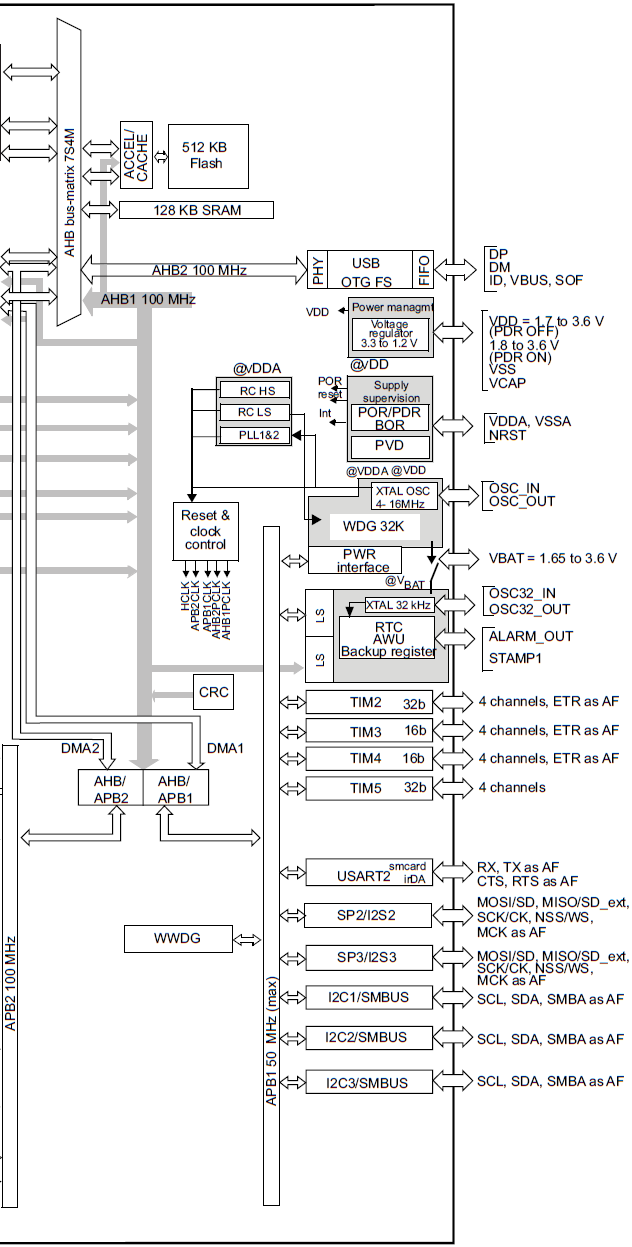

AHB/APB 总线桥 (APB)

借助两个 AHB/APB 总线桥 APB1 和 APB2,可在 AHB 总线与两个 APB 总线之间实现完全 同步的连接,从而灵活选择外设频率。

有关 APB1 和 APB2 最大频率的详细信息,请参见器件数据手册;有关 AHB 和 APB 外设地 址映射的信息,请参见STM32F411参考手册中的 Table 1。

每次芯片复位后,所有外设时钟都被关闭(SRAM 和 Flash 接口除外)。使用外设前,必须在 RCC_AHBxENR 或 RCC_APBxENR 寄存器中使能其时钟。其中RCC寄存器不属于外设,复位后RCC寄存器直接由HSI提供时钟信号。但其RCC寄存器仍然挂接在AHB1总线上,具体请看下文中 STM32F411xC/xE 方框图中的“Reset & clock control”。

注意:对 APB 寄存器执行 16 位或 8 位访问时,该访问将转换为 32 位访问:总线桥将 16 位或 8 位数据复制后提供给 32 位向量。

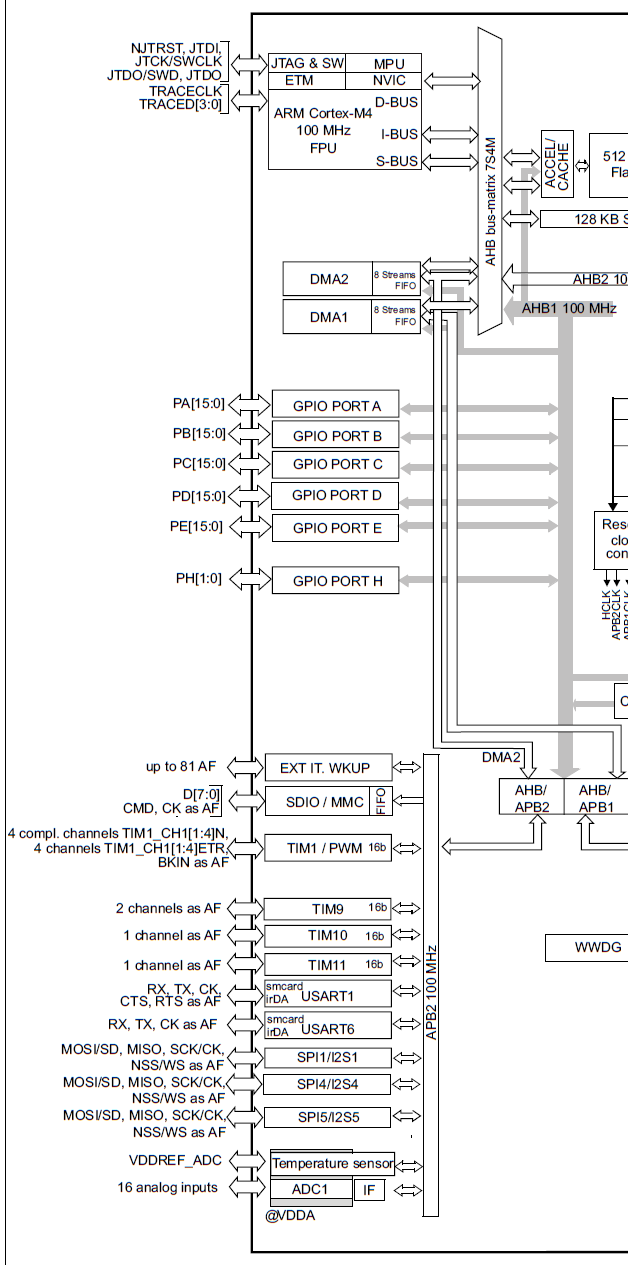

STM32F411xC/xE 方框图

左边部分:

右边部分:

挂接在 AHB1 总线上的外设有:GPIOA、GPIOB、GPIOC、GPIOD、GPIOE、GPIOH、CRC、RCC、Flash 接口寄存器、DMA1、DMA2;

挂接在 AHB1 总线上的外设有:USB OTG FS;

挂接在 APB1 总线上的外设有:TIM2、TIM3、TIM4、TIM5、RTC 和 BKP 寄存器、WWDG、IWDG、I2S2ext、SPI2 / I2S2、SPI3 / I2S3、I2S3ext、USART2、I2C1、I2C2、I2C3、PWR;

挂接在 APB2 总线上的外设有:USART1、USART6、ADC1、SDIO、SPI1/I2S1、SPI4/I2S4、SYSCFG、EXTI、TIM9、TIM10、TIM11、SPI5/I2S5。

有关 STM32F411xC/E 器件中可用外设的边界地址请参考STM32F411数据手册中的“Table 1. STM32F411xC/E register boundary addresses”。

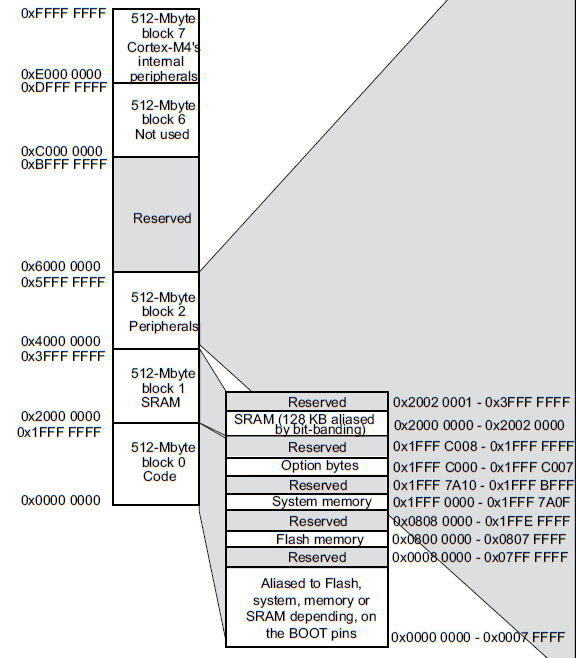

二、存储器组织结构

综合存储器映射图:

程序存储器、数据存储器、寄存器和 I/O 端口排列在同一个顺序的 4 GB 地址空间内。

各字节按小端格式在存储器中编码。字中编号最低的字节被视为该字的最低有效字节,而编号最高的字节被视为最高有效字节。

有关外设寄存器映射的详细信息,请参见STM32F411参考手册中的相关章节。

可寻址的存储空间分为 8 个主要块,每个块为 512 MB。

未分配给片上存储器和外设的所有存储区域均视为“保留区”。请参见STM32F411数据手册中的存储器映射图。

从0x0000 0000到0x03FF FFFF这段地址空间称为自举存储空间,Cortex™-M4F CPU 通过 ICode 总线从地址 0x0000 0000 获取栈顶值,然后从始于0x0000 0004 的存储器开始执行代码。自举存储空间使用别名,也就是说在单片机上电之前是没有存储器映射到这段自举存储空间内的。单片机上电之后通过硬件检测相应的 BOOT 引脚来确定将自举存储空间映射到主 Flash、系统存储器还是嵌入式 SRAM。

1791

1791

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?