AXI协议关于Data read and write structure的部分指出,在数据传输过程中,主要涉及三个问题:

- 窄位宽数据传输(Narrow transfers)

- 地址非对齐传输(Unaligned Transfer)

- 混合大小端传输(Byte invariance)

Narrow transfers

当master产生的一笔数据(transfer)位宽小于总线数据位宽时,该次传输成为窄(位宽)数据传输。

协议中规定:

- 在 INCR 和 WRAP 模式中每次使用的 byte line 必须不同,即数据位置与地址对应。

- 在 FIXED 模式中,整个传输过程使用相同的 byte line(地址反正 FIXED 不会变)

在这种传输过程中,Master需要告知slave数据通道中哪些字节是有效的,这就需要使用到W通道中的WSTRB信号。

WSTRB[n] 对应 WDATA[8n+7:8n],也就是:当 WSTRB[n] 为 1 时,WDATA[8n+7:8n]有效。

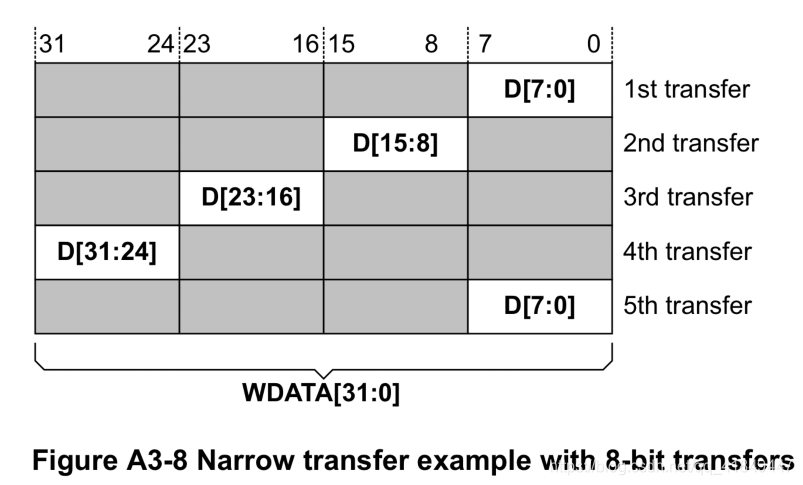

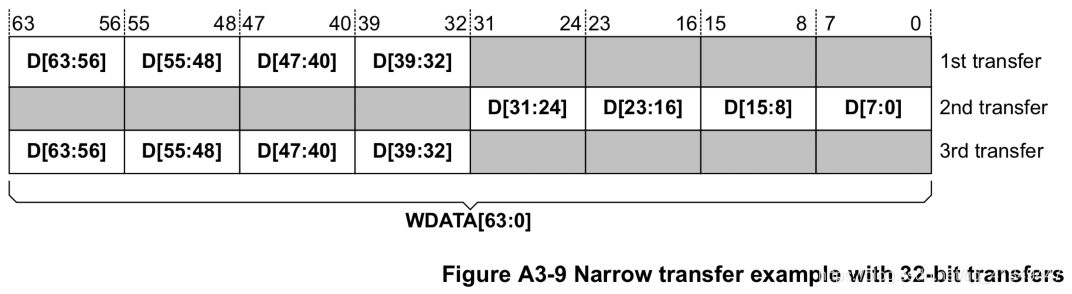

以下图为例,5笔transfer的WSTRB分别为0001/0010/0100/1000/0001

从上图我们发现,在每次数据传输中使用的数据总线字节位置(byte line)不同,尽管数据以字节为单位,分为多个周期传输,但是数据的位置仍与其地址对应。D[7:0]将写入起始地址 0x0,故位于最低字节。D[15:8] 将写入地址 0x1,故位于次低字节。

总之,这种窄位宽传输的设计可能的好处在于,当Master是因为Slave或者其他客观条件限制,需要进行窄传输时,可以一次性将数据放置于数据总线上,只需在每次传输期间由Master改变WSTRB信号即可。窄传输中通过Master来调整有效数据的字节位置,以及给出字节有效信号 WSTRB,能够使Slave无需进行数据重组等工作。

Unaligned transfers

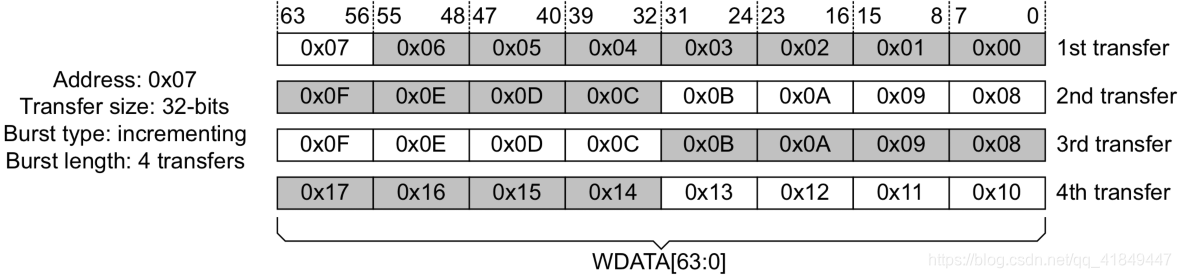

AXI 协议支持地址非对齐的传输,允许突发传输的首字节地址,即起始地址与突发传输位宽不对齐。举个例子,数据总线位宽为 64bit 时,如果起始地址为 0x1002 ,则产生了非对齐现象。与 64bit 位宽总线对齐的地址需要能被 8(byte) 整除,即 ADDR[2:0] = 3’b0。

此处对齐与否应该取决于突发传输的宽度,而不是数据总线位宽!这两个是不一样的!数据总线是64bit不代表WDATA有效的数据是64bit

对于非对齐传输,Master会进行两项操作:

- 即使起始地址非对齐,也保证所有传输是对齐的

- 在首个transfer中增加填充数据,将首次传输填充至对齐,填充数据使用 WSTRB 信号标记为无效

这是一个窄传输+非对齐传输的例子,以1st transfer为例:

- 首先将transfer填充至突发传输位宽32bit(和数据总线位宽区分开),还需要补充0x07 mod 4(byte) = 3byte。解决了非对齐的问题。

- 接下来就是窄位宽传输的问题了,遵从上文的分析。

- Master通过添加7byte数据将的实际地址调整为对齐,并用WSTRB为1000标识出无效字节

Mixed-Endian data structure

首先我们要搞清楚内存中数据存放的大小端模式。可以参考内存中的数据存放模式(大端/小端)

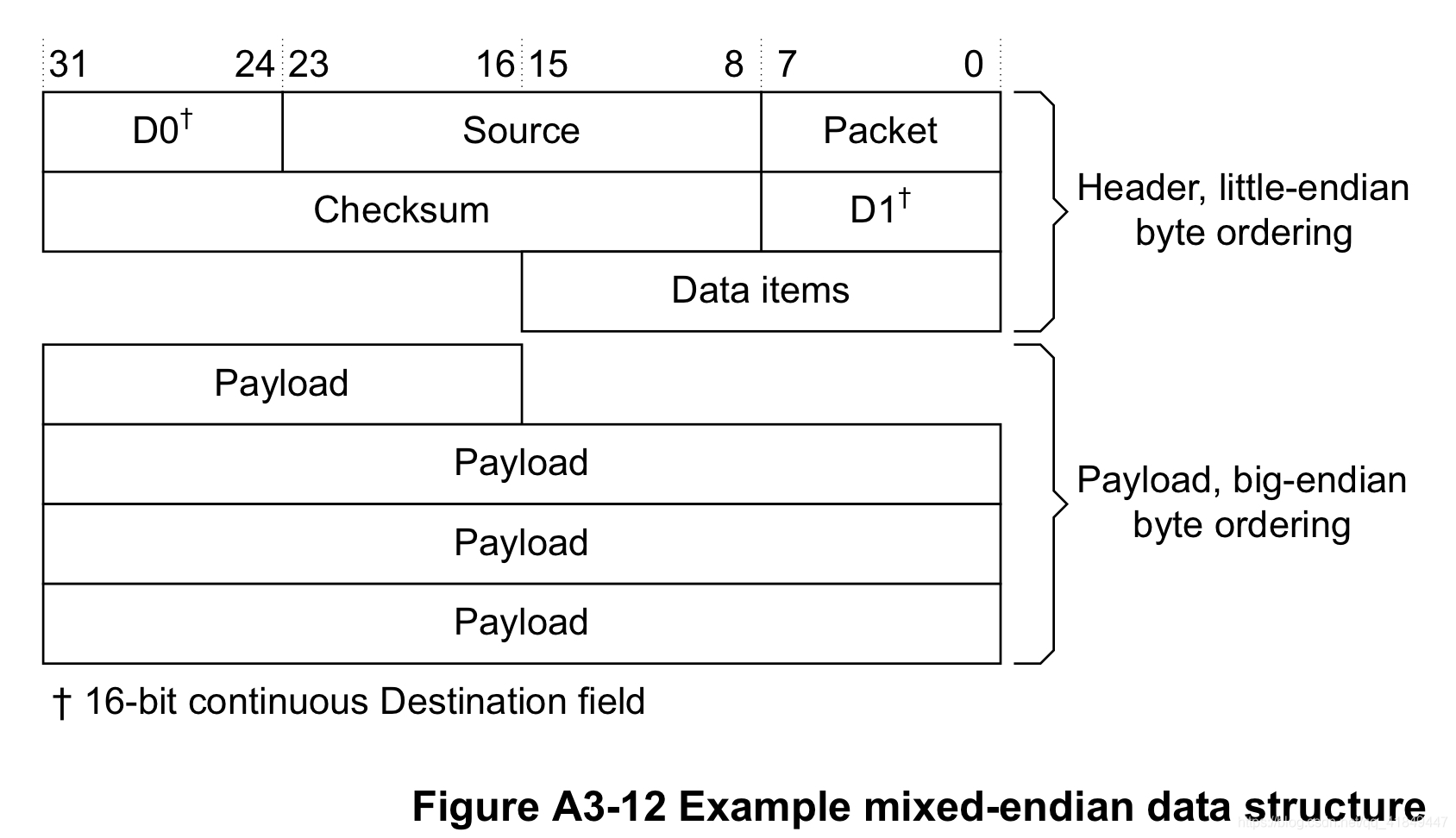

为了能够使大小端模式在存储中共存,AXI 协议设计了一种字节定序(Byte-invariant)的大小端传输方案。对于存储中包括多个字节的数据结构(单字节自然不存在大小端问题)协议做了如下规定:

- 无论数据按什么顺序存放,每个数据结构存储空间的分配方式是相同的

- 该数据结构按照其大小端模式决定字节存储的地址顺序

- 在传输过程中不考虑数据结构的大小端,按照字节原先存储的顺序,原样传输并存放至对端

这种模式的意义在传输双方均不对数据结构的大小端进行解析转换,而严格按照字节的存储顺序进行传输并转存,防止大小端共存产生数据覆盖。

参考文献:

amba3_axi_protocol_spec.A3.4.3

https://zhuanlan.zhihu.com/p/46538028

本文深入探讨AXI协议中关于窄位宽数据传输、地址非对齐传输及混合大小端传输等核心概念。针对不同场景下数据传输的具体实现进行了详细解释,并提供了具体的案例分析。

本文深入探讨AXI协议中关于窄位宽数据传输、地址非对齐传输及混合大小端传输等核心概念。针对不同场景下数据传输的具体实现进行了详细解释,并提供了具体的案例分析。

3565

3565

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?