AMBA总线无论是soc还是FPGA,应该都是比较常用的一组总线协议,对于其中的协议,有一种传输形式叫Narrow Transfers。

>>Axsize

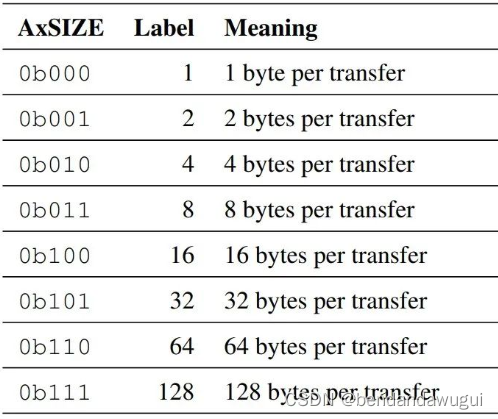

在AXI4协议中,aw通道以及ar通道均存在一个size字段:

这里面就有点儿意思了,比如说在FPGA中常用的512bit总线位宽场景下,FPGA设计里一般也会直接固定死arsize,awsize为0x6,即每拍传输64bytes,然而协议里面的设置野允许了axsize可以设置为0x0~0x6中任一值,即每一拍可以传输1,2,4,8,16,32,64中的任一情况,而这种不满位宽输出的场景,即为“Narrow Transfers”

>>传输规则

在AXI4总线中,协议中规定了其传输规则:

示例参数

- 总线宽度:64位(8字节)

- 突发类型(Burst Type):INCR(递增模式)

- 突发大小(Burst Size, AxSIZE):4字节(对应32位数据传输,

AxSIZE=0b010) - 突发长度(Burst Length, AxLEN):4(共传输5次,因AXI突发长度定义从0开始计数)

- 起始地址(AxADDR):0x1000(对齐到4字节边界)

地址计算规则

- 地址对齐:起始地址必须对齐到突发大小(

AxSIZE)的整数倍。本例中起始地址0x1000满足4字节对齐。 - 地址步长:每次传输后,地址递增步长等于突发大小(4字节)。

- 数据位置:数据在总线中的位置由起始地址的低位决定。

- 64位总线中,每个地址对应1字节。

- 起始地址0x1000对应的总线数据段为:

- 低32位:地址0x1000~0x1003

- 高32位:地址0x1004~0x1007

- 若起始地址为0x1004,则数据占据高32位(地址0x1004~0x1007)。

传输过程与地址变化

| 传输序号 | 地址(Hex) | 数据在总线中的位置 | 地址计算逻辑 |

|---|---|---|---|

| 0 | 0x1000 | 总线[31:0](地址0x1000~0x1003) | 起始地址 |

| 1 | 0x1004 | 总线[63:32](地址0x1004~0x1007) | 0x1000 + 4字节 = 0x1004 |

| 2 | 0x1008 | 总线[31:0](地址0x1008~0x100B) | 0x1004 + 4字节 = 0x1008 |

| 3 | 0x100C | 总线[63:32](地址0x100C~0x100F) | 0x1008 + 4字节 = 0x100C |

| 4 | 0x1010 | 总线[31:0](地址0x1010~0x1013) | 0x100C + 4字节 = 0x1010 |

关键点解析

-

数据位宽与总线对齐:

- 总线宽度为64位,但每次仅传输32位数据(Narrow传输),因此每个地址步长仅增加4字节(而非8字节)。

- 数据在总线中的位置由地址的低3位(

AxADDR[2:0])隐式决定:- 若起始地址低3位为

0b000(如0x1000),数据占据总线低32位; - 若起始地址低3位为

0b100(如0x1004),数据占据总线高32位。

- 若起始地址低3位为

-

突发类型影响:

- INCR模式:地址线性递增(如上述示例)。

- WRAP模式:地址在达到边界后回环,例如:

- 若突发长度为4(5次传输),边界为

4 * 4字节 = 16字节。 - 起始地址0x1000,传输地址依次为:0x1000 → 0x1004 → 0x1008 → 0x100C → 0x1000(回环)。

- 若突发长度为4(5次传输),边界为

-

未对齐【地址】处理:

- 若起始地址未对齐(如0x1001),AXI协议要求从机返回错误响应(

SLVERR)。

- 若起始地址未对齐(如0x1001),AXI协议要求从机返回错误响应(

4. len=0 的narrow 传输即为 narrow single,len>0 的传输即为 narrow burst。

设计注意事项

- 性能优化:Narrow传输会降低总线利用率(如64位总线仅传输32位数据),需权衡带宽与设计复杂度。

- 地址生成逻辑:主设备需根据

AxSIZE和AxLEN自动计算地址步长,避免手动干预。 - 跨时钟域:若总线时钟与本地时钟不同步,需插入FIFO或异步桥处理地址与数据同步。

2860

2860

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?