做过USB的人都或许有一个纠结,那就是D+和D-上到底要串多大的电阻,串在源端还是终端。

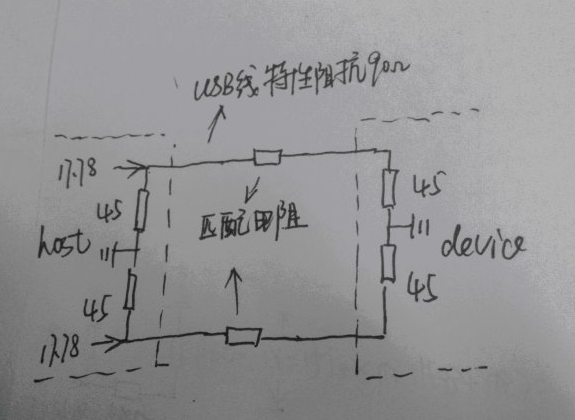

我想说:网络上的说法都不完全正确,首先USB有低速、全速和高速之分,在低速和全速模式下是电压驱动的,驱动电压为3.3V,但在高速模式下是电流驱动的,驱动电流为17.78mA,host-device模型如下:

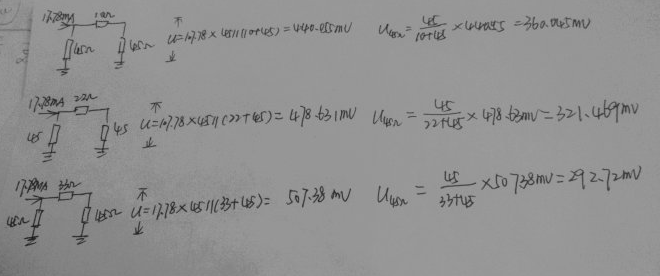

Host和device的D+和D-都有45ohm的电阻端接到地,所以每根线的并联电阻为22.5ohm,17.78x22.5=400mV,所以高速模式下的差分幅度为800mV (这时匹配电阻为0),但是匹配电阻选择10ohm,22ohm和33ohm时我们可以计算出单端信号的幅度如下图:

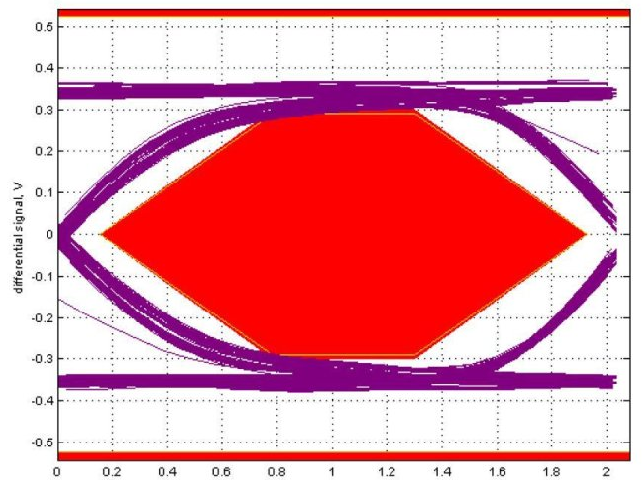

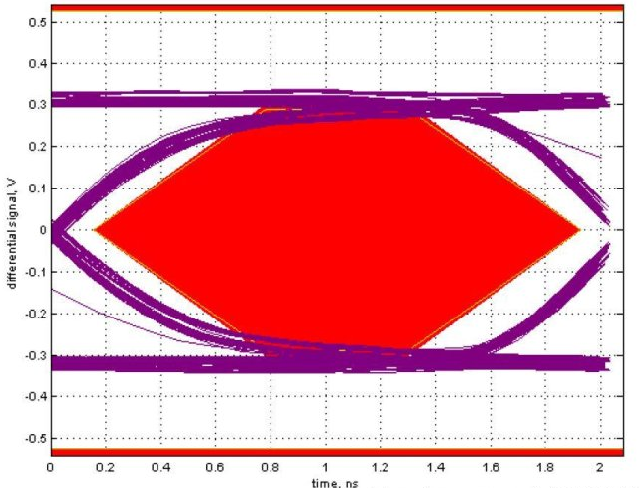

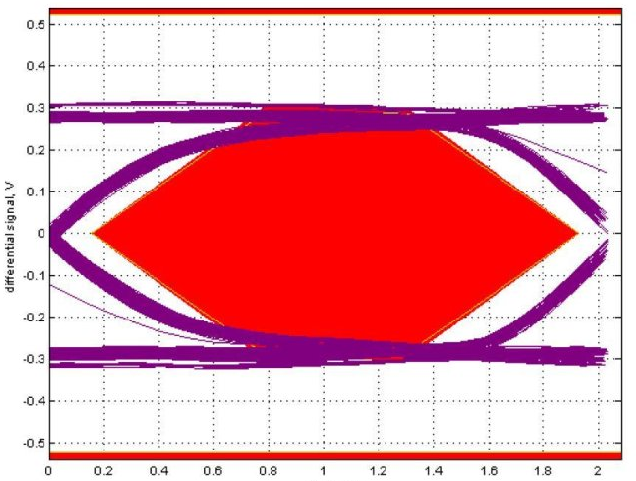

由此可得高速模式下加入匹配电阻会使信号幅度下降,使信号质量变差,加入匹配电阻后的眼图分别如下:

10ohm

22ohm

33ohm

总结:一般高速模式下是通过电流源驱动的,以上任何匹配电阻的存在都将降低信号质量,所以高速模式不用接匹配电阻。

那么网上所说的匹配电阻都是错的么?也不是啦!网上所说的匹配电阻都是在全速和低速模式下的,全速模式下为电压驱动的,驱动器具有一定输出阻抗(一般较小),USB线的特性阻抗为90ohm,所以要想源端与USB线匹配就需要串电阻,具体阻值是要根据驱动器的输出阻抗来决定的,如果驱动器输出阻抗小于USB线特性阻抗,则串联一个电阻Rs,使驱动器阻抗+Rs=USB线特性阻抗。如果驱动器输出阻抗大于USb线特性阻抗,则要并联一个电阻。

转自:http://blog.sina.com.cn/s/blog_7bfaf44b010147u9.html

转自:http://blog.sina.com.cn/s/blog_7bfaf44b01014gjp.html

1126

1126

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?