文章目录

- 前言

- 一、简答题

-

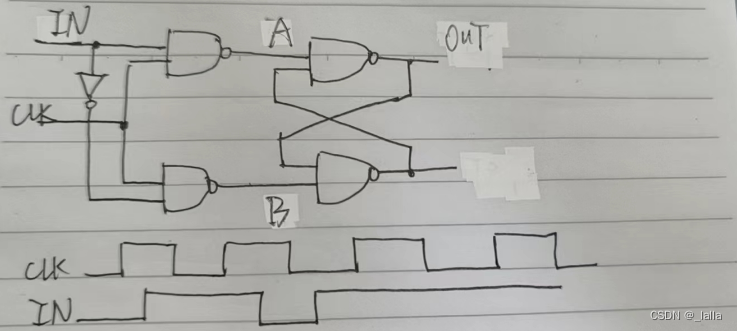

- 1、如下图所示的组合电路以及给出的CLK和IN的输入波形,画出A,B,OUT三个点的波形图

- 2、请用verilog语言设计实现如图所示流水线电路。

- 3、(1)你所了解的算法、接口协议有哪些?尽可能多列出接触过的算法或者协议。(2)挑选其中一个算法或者接口协议,详细阐述。可以使用公式、伪代码、图表、波形等方式。

- 4、一个五级的mux,若是第二级数据信号为关键信号(即其延迟最大),如何改善timing

- 5、盐重量问题:有7克、2克砝码各一个,天平一只,如何只用这些物品三次内将140克的盐分成50、90g各一份?

- 6、一个delay element基本单元有如下结构,假设其中所有门电路延迟为0.1ns,将8个delay element串联为如下结构,并配置sel[7:0]为8’ b00001000,请计算start到end的延时为多少,并简述计算过程

- 二、复合题

前言

笔试题型:简答题(6个) + 复合题(3个)

笔试平台:猿圈(电脑监控)

笔试时间:1h30min

做题感受:9个大题,相当于10分钟一个题目,体量大且题目难度大,写不出来,且题目中图片都是乱码

一、简答题

1、如下图所示的组合电路以及给出的CLK和IN的输入波形,画出A,B,OUT三个点的波形图

2、请用verilog语言设计实现如图所示流水线电路。

该流水线电路需要实现将上游模块发送的8bit数据din传送给下游模块中,当上游模块数据准备好后,din_vld信号有效(即为高电平),经过3级流水后(即三个时钟周期),将数据通过dout端发送给下游模块,此时dout_vld信号有效(即为高电平),表明dout数据有效。

- 如果下游模块没有准备好,那它随时可以通过dout_rdy信号告知前级模块,暂停数据传输。dout_rdy信号为低电平时表示没有准备好。

- 如果上游模块数据无效,它也可以随时拉低din_vld信号,来暂停数据传输。

- 模块输入:输入数据din,8bit位宽,输入数据有效指示位din_vld

- 输出数据准备信号dout_rdy,

订阅专栏 解锁全文

订阅专栏 解锁全文

2602

2602

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?