在第一次VHDL实验中,要求实现下图所示的非常简单的逻辑功能:

由于VHDL中实现逻辑功能的语言与C语言类似,稍微学习一下VHDL的语法,很容易就写出了实现该逻辑功能的语句:

IF S="00" THEN

A<=C;

ELSIF S="01" THEN

C<=A;

ELSE

C<=B;

END IF;但是这样的仿真结果会出现右图所示的“不确定”信号:![]()

从网上找到的代码与笔者想的代码稍有不同:

IF S="00" THEN

C<="ZZZZZZZZ";A<=C;

ELSIF S="01" THEN

A<="ZZZZZZZZ";C<=A;

ELSE

C<=B;

END IF;其多了一个给C、A赋值为“ZZZZZZZZ”的代码。这样的话仿真结果是正确的,当在仿真S="00",C=“01010101”时,得到的A的结果也为“01010101”。

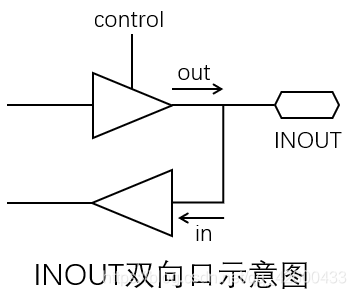

(注:由于A、B、C为8位数据总线,赋值“01010101”代表第0位到第8位分别为'0','1','0','1','0','1','0','1',赋值“ZZZZZZZZ”代表第0到第8位全为“Z”,其中每一位都是一个“INOUT”双向口。请不要因为VHDL语言的简化而认为这8位是同一个INOUT口,事实上它们8个是相互独立的8个INOUT口。)

这让我百思不得其解:在代码中明明给C赋值为“ZZZZZZZZ”,然后在将C的值赋给A,那A的值不应该也是“ZZZZZZZZ”?这样的话,在仿真中C的信号为“01010101”又有什么意义?

出现这样矛盾的思维是因为笔者当时还是用看C语言的视角来看VHDL语言,要注意的是,VHDL是一门硬件编程语言,其与C语言等计算机编程语言是不同的。

什么是“ZZZZZZZZ”?为什么要赋“ZZZZZZZZ”?

在参考文档中,作者只简单的说明了赋值“ZZZZZZZZ”的目的是“为输出端置为高阻态,因为双向口在同一时刻只可执行输入功能”,这让我还是有点不明白,但是至少有了“高阻态”这一突破口。通过查找资料,我渐渐了解了其中的缘由。

双向端口的设计也需要考虑三态的使用。因为双向端口在完成输入功能时必须使原来呈输出模式的端口呈高阻状态。否则,待输入的外部数据会与端口处原来的电平发生线与,导致无法将外部数据正确的写入。

要注意的是,Z在综合中是一个不确定的值,不同的综合器会给出不同的结果。对于关键词VHDL不区分大小写,但是高阻‘Z’需要大写。

------摘自新浪博客《三态门电路及其VHDL实现双向端口》

什么是“线与”?

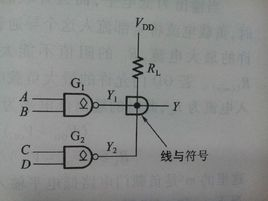

两个输出端(包括两个以上)直接互连就可以实现“AND”(线与)的逻辑功能。

------百度百科《线与逻辑》

当用TTL作为输出端时,若多个TTL以右图所示的“线与结构连接时”,当两个输出端一个输出高电平一个输出低电平时,由于它们的输出端连接的是同一条线(或理解位两个输出端之间连接),这是会出现问题的。在仿真时,线上将会出现“不确定”状态(上面的“XXX”仿真结果);在实际电路中,由于导线的电阻很小,这样会形成很大的电流,击穿TTL。这样的电路是不可取的。

这时就出现了一个叫做“三态门”的东西。用“三态门”作为输出端时可以解决上面的问题。

什么是“三态门”?

一般的输出口只有“高电平”和“低电平”两种输出状态,这两种状态下输出口和外部导线是相连的。也就是说,无论该输出口处于“高电平”还是“低电平”,只要外部导线(或“线与”的其他输出口)给出了不同的输出状态,都会产生大电流烧毁电路。“三态门”就引入了“高电平”和“低电平”以外的第三种状态——“高阻态”。当输出口处于“高阻态”时,从外部导线看入的电阻非常大,相当于断路。当有两个输出口需要以线与结构连接时,当输出口1输出时,将输出口2置为高阻态,这时外部导线相当于只连接了输出口1,获得的是输出口1的数据;当输出口2输出时则置输出口1为高阻态。

(注:为什么两个输出口要接同一个外部导线?(待补充。。。))

INOUT双向口的“高阻态”:

上面笔者说的是多个输出口线与的时候需要用到三态门的高阻态,那么为什么VHDL中的INOUT双向口也需要用到三态门的高阻态呢?

如上图INOUT双向口的示意图,其结构为IN口和OUT口接同一个外部导线(使用同一个引脚),这时也会出现与上面多输出口线与遇到的问题相同的问题:当第0s输出口有输出时,其会一直保持输出。若第1s在仿真波形中对该INOUT口给了一个信号值,让输入口读入时,当第0s保持到第1s输出口一直在输出的值与仿真波形给的输入值不同时,就会出现上面线与时遇到的问题。在仿真中将出现不确定状态,在实际电路中则会烧毁。

这个时候就需要用到三态门的高阻态了。双向INOUT口的输出口是带有控制端的,当为双向口赋值为“Z”时,输出口将处于高阻态,此时相当于输出口与外部导线断路,只有输入口连接,这时输出口的值与导线给入的值不同不会引发错误。

总之,当INOUT口需要输入值时,需要将其设为高阻态,以防止之前的输出值影响输入。

本文介绍了VHDL中INOUT双向口的使用,探讨了为何需要赋值“ZZZZZZZZ”以实现高阻态,以及三态门在解决线与问题中的作用。通过实例解释了高阻态如何防止输出值影响输入,并防止电路损坏。

本文介绍了VHDL中INOUT双向口的使用,探讨了为何需要赋值“ZZZZZZZZ”以实现高阻态,以及三态门在解决线与问题中的作用。通过实例解释了高阻态如何防止输出值影响输入,并防止电路损坏。

1010

1010

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?