reg d;

reg [1:0] out;

always@(posedge clk) begin

if(!rst_n)

d <= 'd0;

out <= 'd0;

else begin

d <= a + b;

out <= d + c;

end

end

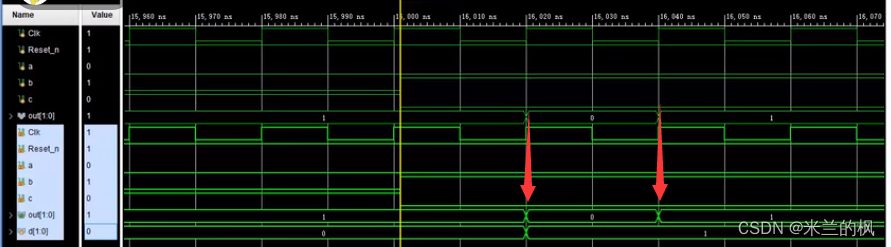

1.时序电路使用非阻塞赋值,always块中的语句顺序无影响;

2.非阻塞赋值中d和out的新值在本次上升沿计算之后,下一次上升沿才会生效;

阻塞赋值会使信号变化立即生效

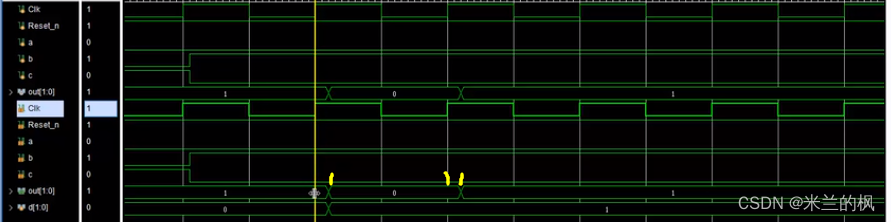

3.实际电路中,下一次上升沿值生效时会有一定触发器延时(上一拍采数时,往左边偏一点采值)。

reg d;

reg [1:0] out;

always@(posedge clk) begin

if(!rst_n)

d <= 'd0;

out <= 'd0;

else begin

d <= #2 a + b;

out <= #2 d + c;

end

end

512

512

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?