ModelSim HDL 设计与模拟基础练习二

FPGA中的整数及运算

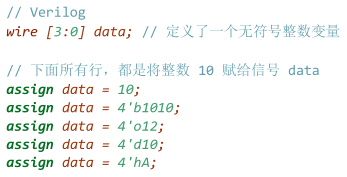

HDL中的整数类型

HDL 语言(Verilog, VHDL)原生支持两种整数类型: 无符号整数 和 有符号整数

- 无符号整数

- 有符号整数(硬件中,有符号整数采用的编码是: 补码)

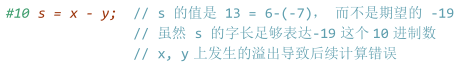

溢出

Overflow

-

无符号整数的溢出

-

有符号整数的溢出

-

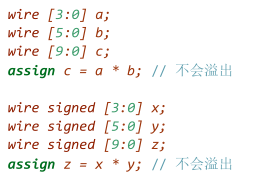

避免溢出的充分条件

a.避免加法运算结果溢出

两个 n bit 整数相加,最多产生一个进位 bit, 所以用 n+1 bit 保存加法之和,就一定不会产生溢出。这个结论可以推广到 2 m 个 n bit 整数相加,用 n+m bit 保存加法结果,就不会产生溢出。b.避免乘法运算结果溢出 一个 m bit 整数与一个 n bit 整数相乘,其结果最多产生m+n bit -

溢出检测

a. 饱和

饱和是溢出发生时,对结果的一种修正(或者说保护)处理。

– n bit 有符号数的饱和

• 发生最大正值界限上的溢出时,将结果限定在能表达的最大正值 ——

(2 n-1 -1)

• 发生最小负值界限上的溢出时,将结果限定在能表达的最小负值 ——

(-2 n-1 )

– n bit 无符号数的饱和

• 发生最大正值界限上的溢出时,将结果限定在能表达的最大正值 ——

(2 n -1)b.饱和的实现

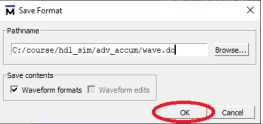

ModelSim技巧:保存波形的设置

• 新技巧:Modelsim 中保存波形的设置

在 Modelsim 中,定义好 Wave 窗口中的信号和显示格式后,可以将设置保存下来。

今后再次做模拟时,直接调出,无需重新将信号拖入 Wave 窗口,重复格式设置等

操作。

– 保存设置

保持 Wave 窗口为当前活动窗口,选择菜单 File > Save Format…

– 调出上一次的 Wave 窗口设置

a. 选择菜单 File > Load > Macro File…

b. 选中 wave.do 文件,点击 Open

1488

1488

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?