本文仅用于记录与学习。参考

1 功能验证

1.1 验证平台:

指用Verilog或VHDL语言实现的一个单元模块。在这个单元模块中,通过实例化将待验证设计(DUV)作为一个子模块,通过验证平台的内部信号给待验证设计(DUV)的输入提供激励信号(包括控制和数据),并接收从待验证设计(DUV)输出的信号(包括控制和数据),通过检查输出是否符合预期值,从而判断待验证设计(DUV)是否能正常工作。验证平台的基本结构如下图:

如上图所示,testbench 最基本的结构包括接收(信号声明)、发送(激励)和待验证设计(模块例化)

1.2 验证平台构造依据:

验证平台主要是用来判断设计是否符合要求和规格(预期),对此,我们要做功能分析。对这些细化、具体化的分解的功能,我们需要定义测试用例,覆盖所有这些具体的功能要求。对于modelsim仿真出来的波形,我们通过检查波形中的数据、或者通过输出数据和预期正确数据的对比检查来判断设计是否正常工作。由于验证没有完成点,可以一直做下去,所以验证只有“收敛”,功能覆盖率和代码覆盖率是判断验证是否“收敛”的依据

1.2.1功能覆盖率:

分为覆盖点(coverage points)和断言(assertion)

1.2.2代码覆盖率:

分为行覆盖(line coverage),翻转覆盖(toggle coverage),分支覆盖(branch coverage),条件覆盖(condition coverage),状态机覆盖(FSM coverage)等

行覆盖: DUV的每行代码都要被执行过

翻转覆盖: DUV的每个模块的信号(包括端口信号和内部信号)都有被翻转过(即每一个信号都从0>1,1>0变化过)

分支覆盖: DUV的所有模块的每个条件分支否有被执行过(包括if,else和case等)

条件覆盖: 可能进入某个分支的所有条件的组合都应该被遍历到

状态机覆盖: 状态机里所有可能发生的状态跳转都要被遍历到

1.3 UART(发送模块)功能的特征分析与分解

1.3.1 UART(发送模块)接口及接口信号分析:

- 时钟和复位:时钟(sys_clk)频率50Mhz,复位(sys_rst_n)信号下降沿触发

- 控制输入:发送使能(uart_tx_en),当其为高电平的时候,代表此时需要发送数据

- 数据输入:一组八位并行数据(uart_tx_data[7:0])

- 数据输出:八组一位串行数据(uart_txd)

1.3.2 UART(发送模块)功能分析

- 复位信号为低电平,无论是否有数据输入,都无数据输出

- 复位信号为高电平,使能信号为低电平,无论是否有数据输入,都无数据输出

- 复位信号为高电平,使能信号为高电平,输入一组8位并行数据,输出对应八组一位串行数据

下图为UART发送模块结构框图:

1.4 UART(发送模块)testbench

`timescale 1ns/1ns //定义时间刻度

module tb_uart_tx();

reg sys_clk ;

reg sys_rst_n ;

reg [7:0] uart_tx_data ;

reg uart_tx_en ;

wire uart_txd ;

parameter integer BPS = 'd230400 ; //波特率

parameter integer CLK_FRE = 'd50_000_000 ; //系统频率50M

localparam integer BIT_TIME = 'd1000_000_000 / BPS ; //计算出传输每个bit所需要的时间

initial begin

sys_clk <=1'b0;

sys_rst_n <=1'b0;

uart_tx_en <=1'b0;

uart_tx_data <=8'd0;

#80 //复位信号拉高,系统开始工作

sys_rst_n <=1'b1;

#200

@(posedge sys_clk);

uart_tx_en <=1'b1; //发送使能

uart_tx_data <= ({$random} % 256); //发送8位随机数据

#20

uart_tx_en <=1'b0;

#(BIT_TIME * 10) //发送1个BYTE需要10个bit

#200 $finish; //结束仿真

end

always #10 sys_clk=~sys_clk; //定义主时钟,周期20ns,频率50M

//例化发送驱动模块

uart_tx #(

.BPS (BPS ),

.CLK_FRE (CLK_FRE )

)

uart_tx_inst(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.uart_tx_done (uart_tx_done ),

.uart_tx_data (uart_tx_data ),

.uart_tx_en (uart_tx_en ),

.uart_txd (uart_txd )

);

endmodule

波形仿真如下

通过随机函数生成一组八位数据8’d36从uart_tx_data[7:0]端口送入UART_TX模块,从uart_txd端口输出八组一位信号00100100(低位在前,高位在后),符合功能描述

2 逻辑综合

2.1 概念

利用工具将RTL代码转换为门级网表,形成以FPGA存在的硬件单元(LUT)构成的电路过程叫做逻辑综合。综合一个设计的过程从读取RTL代码开始,通过施加时序约束关系,映射产生一个门级网表文件。在Quartus II中双击“Analysis&Synthesis”,完成分析与综合,该步骤在Quartus II中完成了编译、映射两步

编译是将原理图、HDL代码、IP软核生成了门级网表。门级网表中,描述的电路元件是基本的门、加法器、除法器等与此同级别的元件。这里生成的门级网表与所用的器件无关

实际上FPGA中并没有与门、或门、非门等门电路,这些逻辑关系,都是由查找表LUT所实现的。所以编译过后,下一步的内容,就是把编译得到的网表,转换为LUT、触发器等FPGA内部存在的基本逻辑单元,而这正是映射的目的,映射之后,得到了具体的综合网表

2.2 使用Quartus II综合

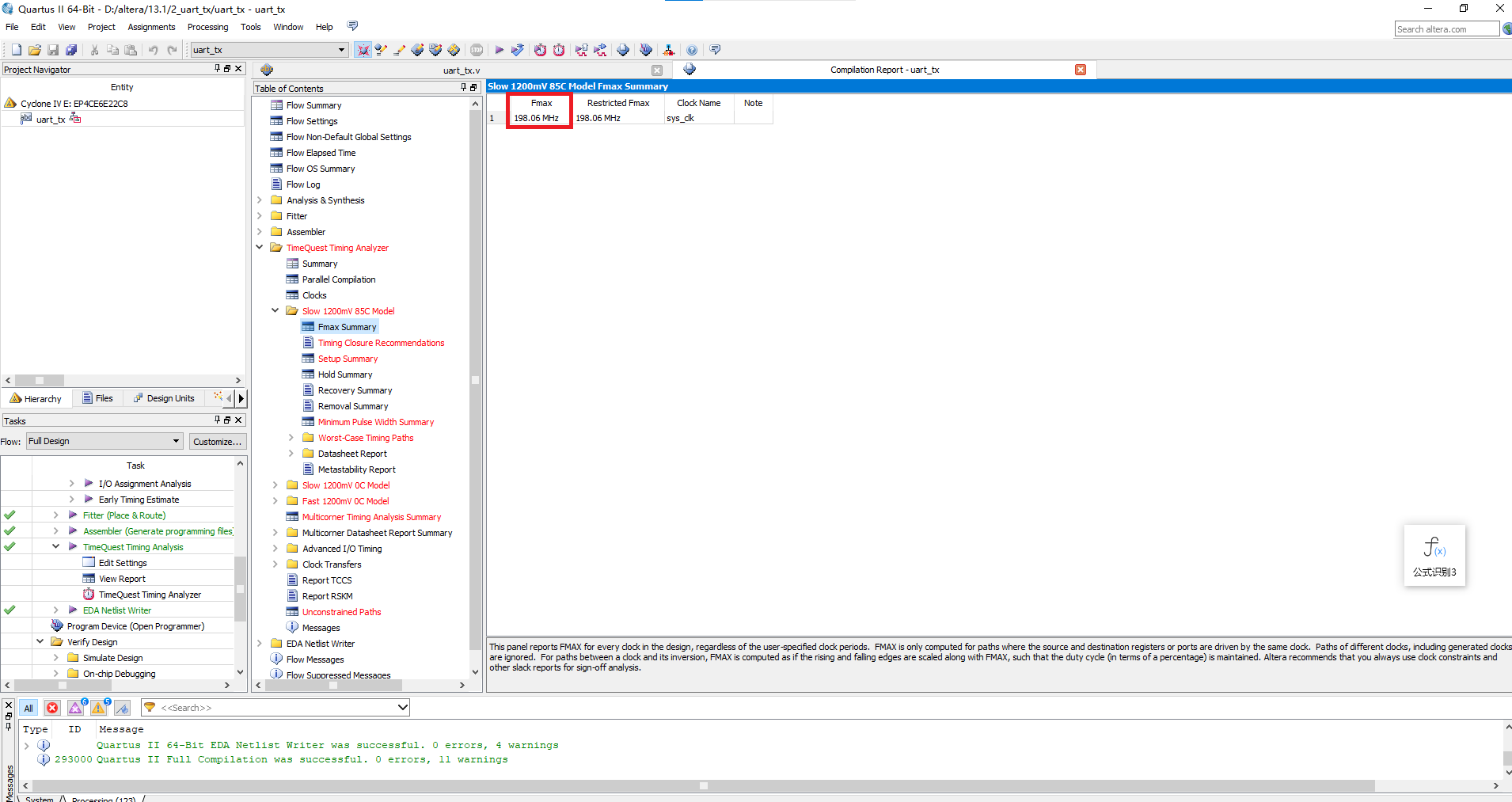

1.首先对工程进行全编译,编译报告中TimeQuest Timing Analyzer部分被标红,系统时钟也不是工程中所定义的50MHz,而是1GHz。这是由于我们没有手动加入时序约束,系统默认给CLK添加的时钟约束是1GHZ

2.可以看到在1200mv,85℃慢速模型下,系统能达到的最大工作频率只有198.06MHz。实际上,这个频率已经比我们想要系统工作的频率高了,但为了规范设计,防止不必要的错误,我们还是需要手动添加时钟约束

12.导出综合后网表文件,点击processing>start>start vqm writter,生成vqm文件(verilog quartus II mapping)

13.点击project>export design partition生成布局布线后的网表文件(qxp文件)

2.3 综合结果

1.门级电路图(未截全)

2.综合后电路图,与门级电路图的区别是,综合后的电路将门级电路映射成了FPGA内部存在的单元,如本工程中的LUT,D触发器,输入缓冲器

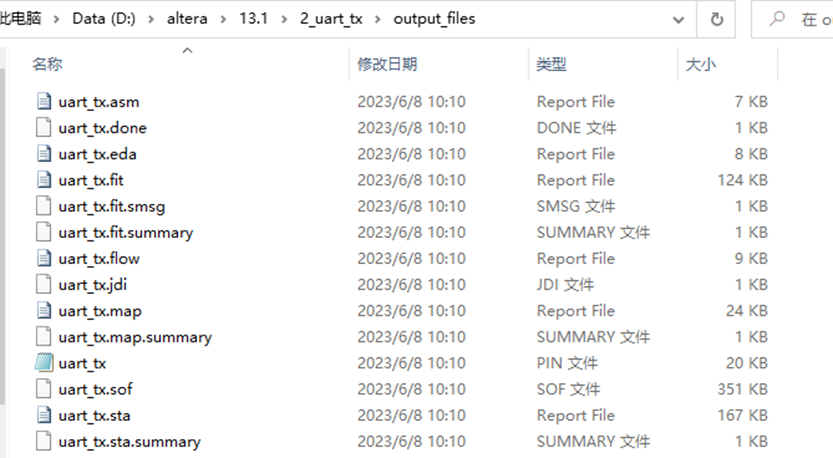

3.工程文件夹下有以下文件,sdc文件为我们添加的时钟约束,qpf为工程文件,qxp为布局布线后的网表,由于建立工程是选择的器件不支持导出综合后的网标文件vqm,所以文件夹里没有该文件

4.如图,simulation>modelsim文件夹下的sdo为器件延时文件,用于时序仿真,vo为门级网表文件

5.output_files文件夹下主要是各种报告文件

3 时钟约束

3.1 时钟约束目的

3.1.1 理想时钟信号

理想时钟信号是完美的方波,但是实际的方波是存在一些时钟抖动的,时钟抖动(Clock jitter)是相对于理想时钟沿,实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动

3.1. 2时钟延时

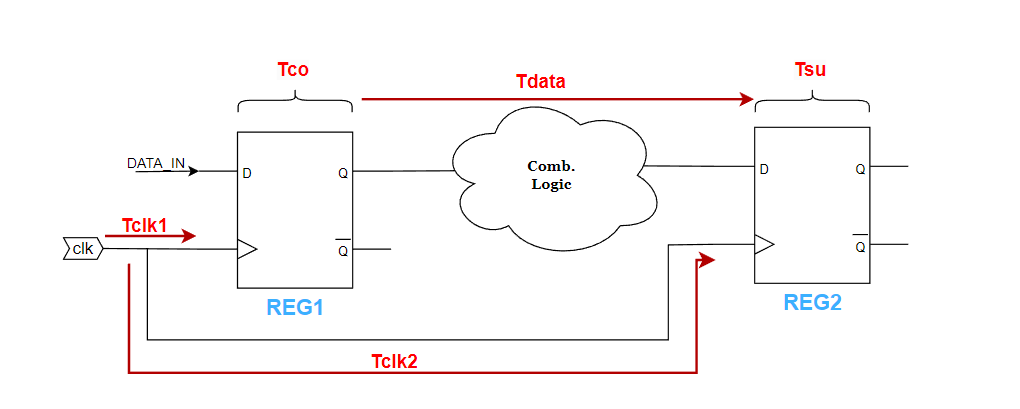

时钟信号也会走线,那么和其它信号的传输一样,就会有延时。下图中,时钟信号从时钟源传输到源寄存器的延时我们定义为 Tclk1,传输到目标寄存器的延时我们定义为 Tclk2。时钟偏差(Clock skew)就是就是Tclk2和Tclk1的差值

3.1.3 时钟不确定性

时钟的不确定性主要是由 Clock Skew 和 Clock Jitter 构成。 因此 Clock Uncertainty = Clock Skew + Clock Jitter。 一般标准的时序约束文件中,都需要加 Clock Uncertainty 的约束,这个约束是为了让时序分析更贴近真实的电路设计

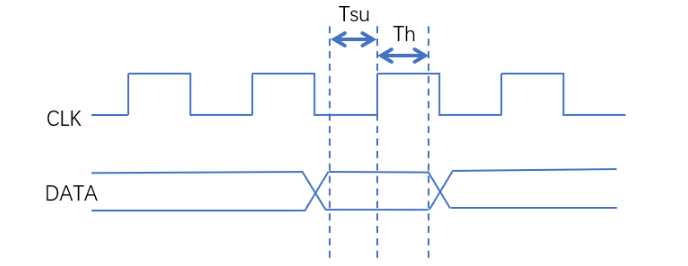

3.1.4建立时间和保持时间

建立时间和保持时间就是在寄存器采样窗口中输入数据必须保持不变,以免寄存器无法稳定采样。

也就是说,在寄存器的采样窗口之前输入数据就必须要保持稳定,即输入数据不能来的太晚(建立时间);同样的,寄存器的输入数据也必须在寄存器的采样窗口结束后才变化,在此之前必须保持问题,即输入数据不能走的太早(保持时间)

3.1.5时序分析

时序分析主要有两种办法:

静态时序分析:(static timing analysis, STA),是遍历电路存在的所有时序路径,根据给定工作条件(PVT)下的时序库.lib 文件计算信号在这些路径上的传播延时,检查信号的建立和保持时间是否满足约束要求, 根据最大路径延时和最小路径延时找出违背时序约束的错误。

动态时序分析:(dynamic timing analysis, DTA),通常是所有的输入信号都会给一个不同时刻的激励,在 testbech(.sp 或者.v)中设置一段仿真时间,最后对仿真结果进行时序和功能分析。 这里的仿真可以是门级或者晶体管级,包括 spice 格式和 RTL 格式的网表

3.1.6时序约束

时序约束就是要告诉综合工具我们的的标准是什么。综合工具应该如何根据我们的标准来布线,以满足所有寄存器的时序要求。

在FPGA设计中,一旦时钟频率上升,那么时钟周期就会减少。频率越高,时钟周期越小,而建立时间和保持时间的要求不变,那么对应的,满足建立时间和保持时间也会变难,因为留给信号到达的窗口变小了

3.2 添加时钟约束

1.打开TimeQuest Timing Analyzer以图形化方式添加约束(也可自己编写sdc文件),界面如下

2.双击Create Timing Netlist 创建约束对象(网表),然后双击Read SDC File读取系统默认为我们建立的约束

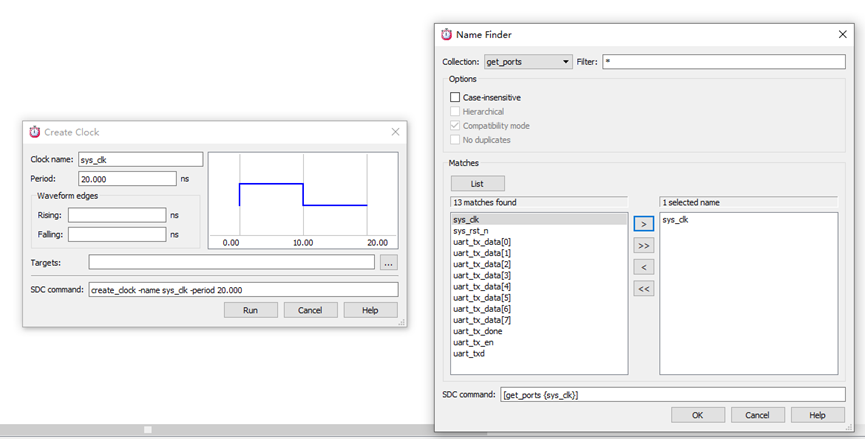

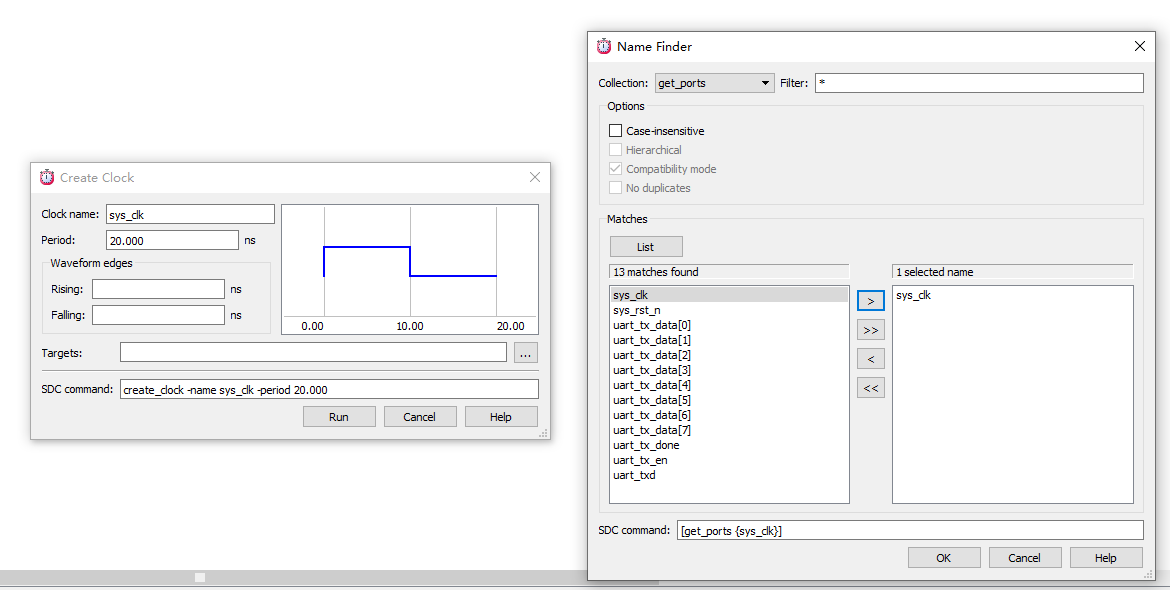

3.点击constaints项的create clock,设置时钟约束

4.在弹出的时钟约束图形界面中,输入该时钟的各项属性。Clock name是用户为约束的该时钟信号取一个方便识别的别名,而非被约束的时钟的原本名称,可任取代号。频率50MHz,则周期设置为20ns,占空比默认50%,Targets为我们要约束的时钟信号。

上面输入的各种参数只是为了方便用户更加方便的添加约束,这些参数输入之后,软件就会根据这些参数生成最终起作用的脚本命令。

5.双击write SDC file,在工程文件夹下会生成sdc文件。点击Diagnotistic栏下的Report Clocks查看时钟约束是否添加成功

6.若添加失败,右键后edit clock constaints重新设置时钟约束

7.点击assignment>settings,将工程文件夹下生成的sdc文件添加进来

8.添加成功后全编译无报错,查看此时软件给出的分析报告,点击report clock查看约束是否生效,report fmax summary查看系统最高能工作的频率

9.在Quartus II界面查看worst-case timing paths,标红的数据表明建立时间余量不够,会引起时序违规。或者在TimeQuest Timing Analyzer手动添加寄存器路径,查看寄存器间时序是否违规

10.在Quartus II界面右击要查看的某两个寄存器之间的时序信息

3.3 简略报告分析

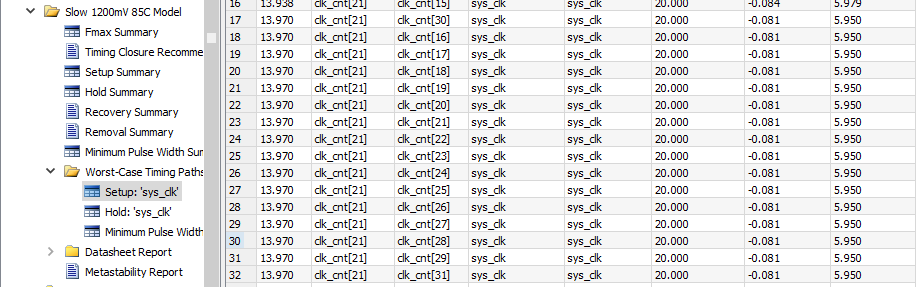

1.在TimeQuest Timing Analyzer软件中,查看工程中时序情况最糟糕的一条路径(相对而言)

红框所示分别为,建立时间余量(slack)为13.938ns;源寄存器clk_cnt[21],目标寄存器clk_cnt[13];发射沿(sys_clk),锁存沿(sys_clk);发射沿与锁存沿时间差(relationship)为20ns,即一个周期;寄存器内部延迟tco和数据路径延迟tdata合为data delay,5.979ns

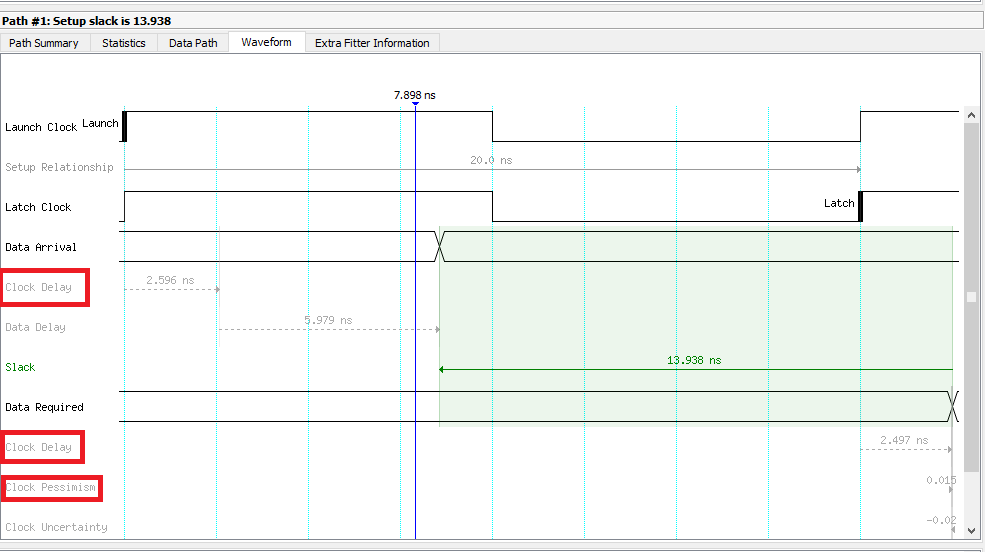

2.建立余量波形示意图

上下两个clock delay分别为Tclk1(最小值),Tclk2(最大值);clock pessimism(时钟悲观)是Tskew=Tclk2-Tclk1的一个修正量,计算Tsew时要加上这个值;

4 布局布线

4.1 FPGA后端流程(主要是布局布线)

布局将逻辑网表中的硬件原语和底层单元合理的配置到芯片内部的固有硬件结构上,需要在速度最优与面积最优之间做出选择;布线根据布局的拓扑结构,利用芯片内部的各种连线资源,合理正确的连接各个元件

FPGA的结构非常复杂,特别是在有时序约束条件时,需要利用时序驱动的引擎进行布局布线。布线结束后,软件工具会自动生成报告,提供有关设计中各部分的资源使用情况。由于只有FPGA生产商对芯片结构最为了解,所以布局布线必须选择芯片开发商提供的工具

4.2 SOC后端流程

4.2.1 Data prepare:

综合/DFT后的网表(netlist)、时序约束sdc、timing&physical等库文件、signoff的条件和设置以及各种EDA工具所需要的工艺文件

4.2.2 Floorplan:

对整个设计进行一个宏观的规划,包括像模块大小的规划,Macro的摆放,power走线的规划,pin的规划,decap的摆放,endcap 的摆放,welltap 的摆放等等

4.2.3 Placement:

对整个设计进行一个宏观的规划,包括像模块大小的规划,Macro 的摆放,电地 power 走线的规划,pin 的规划,decap 的摆放,endcap 的摆放,welltap 的摆放等等

4.2.4 CTS:

芯片中的时钟网络要驱动电路中所有的时序单元,所以时钟源端门单元带负载很多,其负载延时很大并且不平衡,需要插入缓冲器减小负载和平衡延时。时钟网络及其上的缓冲器构成了时钟树。

4.2.5 Route:

包括布线及之后的优化,主要是调用PR工具的算法对设计中的net进行自动布线,并在布线后继续优化时序, 面积和功耗等

4.2.6 ECO:

对于工具无法完全修掉的问题进行手动修复,包括局部的改动逻辑功能,例如将cell的连接关系改掉,或者增加删除inverter等和时序优化脚本

4.2.7 Pysical Verification:

DRC(检查连线间距,连线宽度等是否满足工艺要求)

LVS(版图与逻辑综合后的网表进行对比验证)

ERC(检查短路和开路等电器违规违例)、ANT、DFM

4.2.8 Signoff:

设计数据交给芯片制造厂商生产之前,对设计数据进行复检,确认设计数据达到交付标准,这些检查和确认统称为signoff

4.3 Quartus II布局布线

1.下图为布局布线后的连接情况

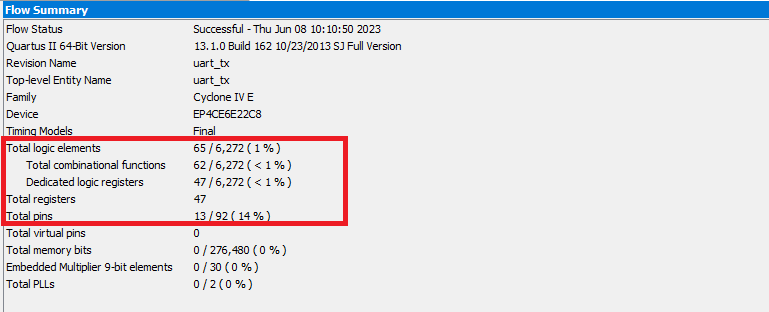

2.在全编译无误后查看flow summary,显示设计总共用到了65个逻辑单元,47个专用逻辑寄存器,13个引脚

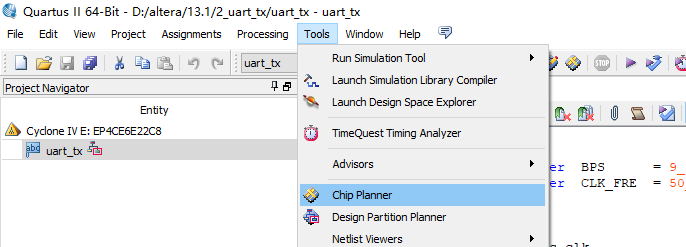

3.点击tools>chip planner,查看FPGA资源使用情况

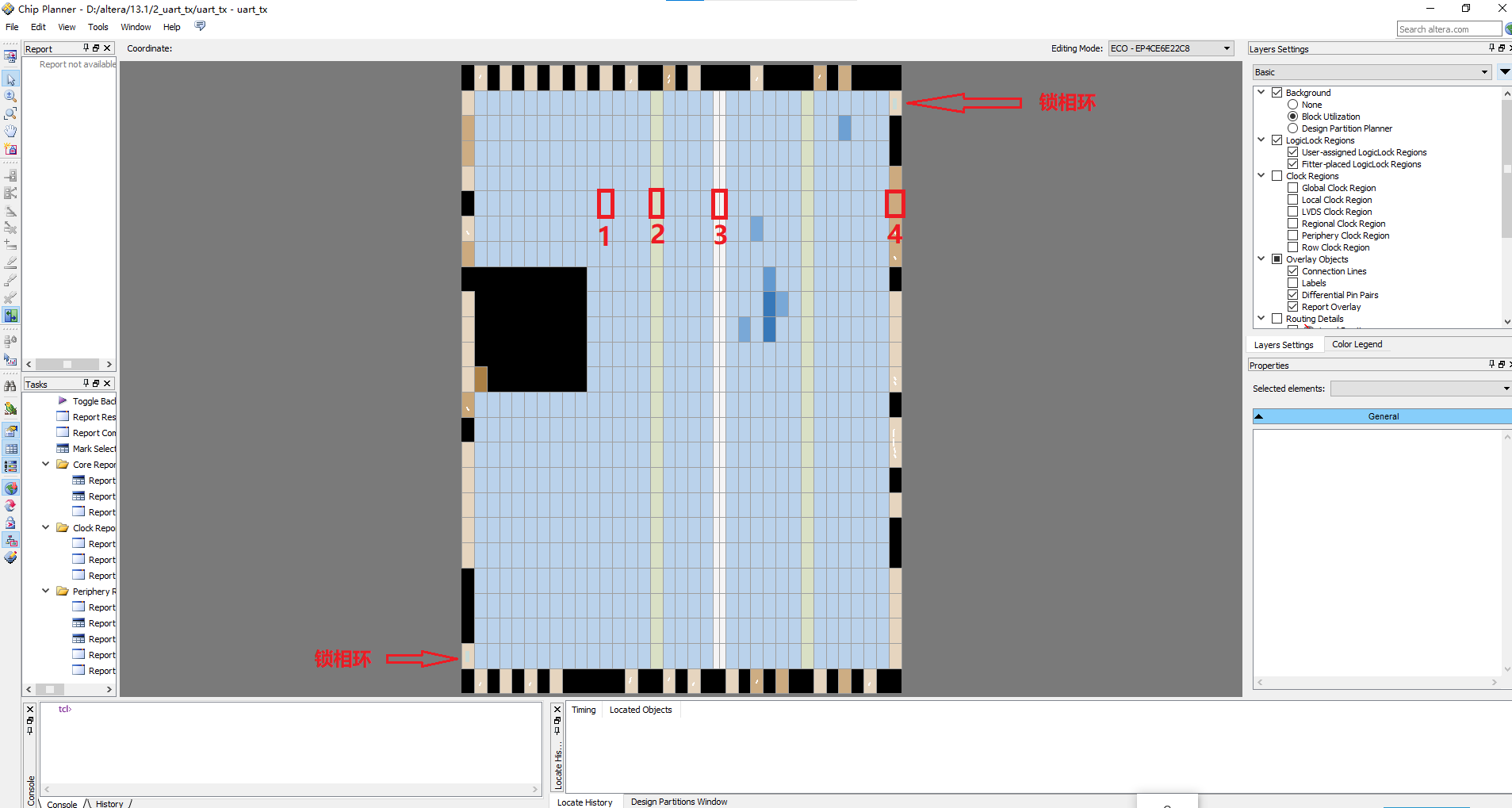

4.可以看到EP4C6E22C8这款FPGA右上和左下各有一个锁相环单元,1标记的单元块为逻辑阵列块(LAB),2标记的单元块为嵌入式存储单元,3标记的单元块为嵌入式乘法单元,4标记的单元块为用户可编程IO

深色表示该资源已经被使用,而颜色越深的地方表示资源利用率越高。黑色区域为一些固定功能的资源或没有资源,用户不可对其进行任意配置

5.放大图像,可以看到每个逻辑阵列块(LAB)由16个逻辑单元(LE)组成,每个LE由一个LUT(蓝色)和寄存器(红色)组成。还可以看到使用的资源少,颜色就浅;使用的资源多,颜色就深

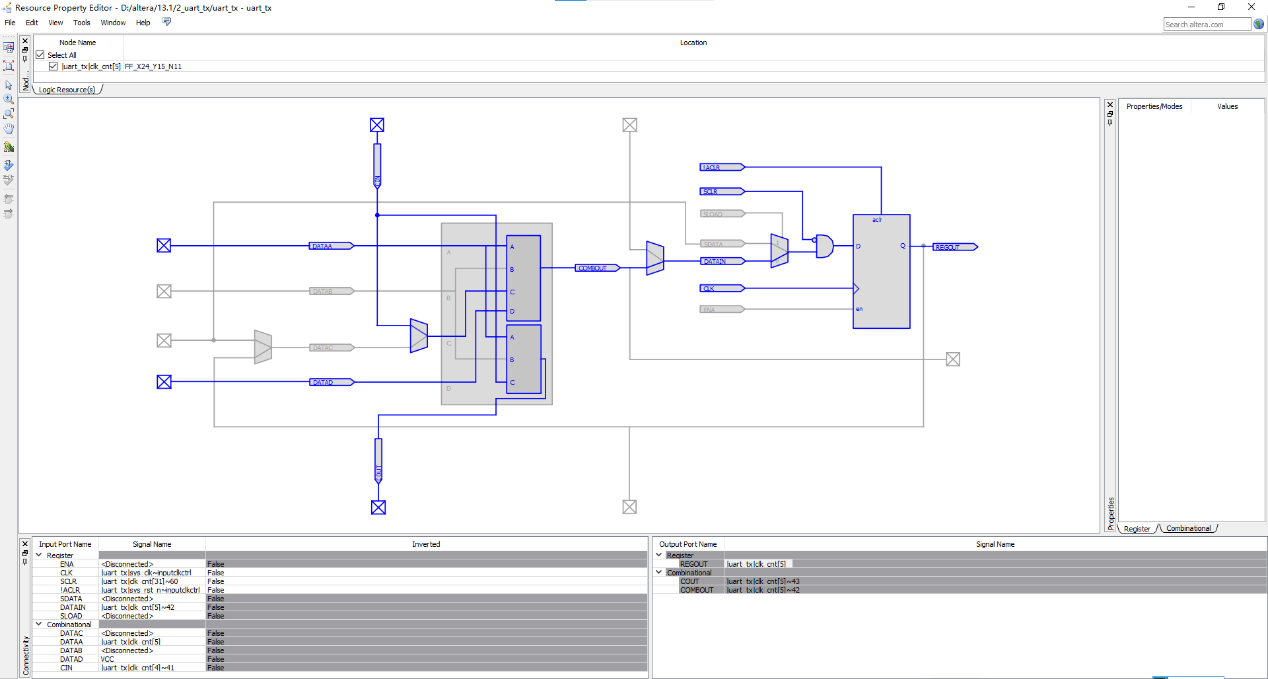

6.双击任意被调用了的LE可以观察到其内部的大致结构,主要由两部分,一是左边的4输入LUT,另一个是可编程寄存器,还一些选择器和与门等辅助逻辑电路

7.双击用户可编程IO单元块,由双向I/O缓冲器、OE寄存器、对齐寄存器、同步寄存器、DDR输出寄存器、三态门、延时模块等组成

8.由于没使用到嵌入式存储单元、嵌入式乘法器单元、锁相环单元,故无法查看内部连接情况

1392

1392

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?