1. 综合基础概念

- 综合:将Verilog、VHDL等语言描述的RTL代码转为使用台积电等代工厂提供的工艺器件描述的网表,在这个过程中综合工具会进行一定逻辑优化。

- 工艺库:包括逻辑门电路、MUX、buffer、触发器、latch等等,他们具有不同的驱动强度、面积、功耗等物理特性,具体选用哪一种,需要不仅需要RTL,还需要我们进行一定的综合约束,然后DC工具进行逻辑映射,生成网表。

- 约束:更多是宏观约束,比如时钟频率、器件最大驱动数量,禁用器件等等

- 输入件:RTL+工艺库+物理库+约束文件

- 输出件:网表(netlist)与相关rpt(面积、时序等)

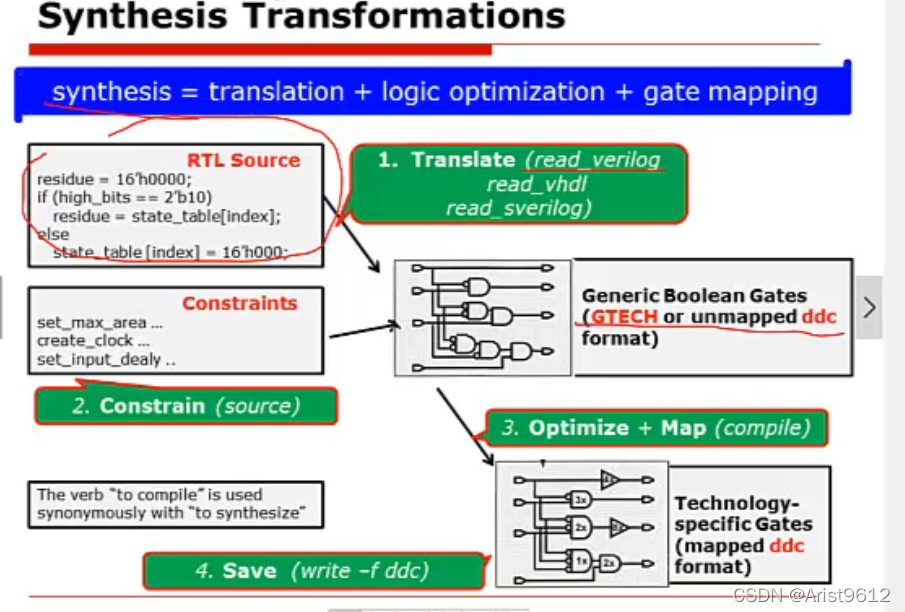

2. 综合流程

- 输入RTL

- DC将各种类型代码编写的RTL转为一般化的逻辑电路,单纯翻译RTL为GTECH电路(此时没有映射到工艺库,即工艺无关)

- 读取约束信息

- 优化,逻辑优化、面积、时序优化、冗余器件删除

- 映射,使用工艺库中器件完成RTL到网表的映射

- 生成ddc,包括ddc网表、延迟信息、约束信息等;sdf文件包括延迟信息,用于后仿真

3. 两种综合模型

- 实际电路的延迟=器件延迟+线延迟

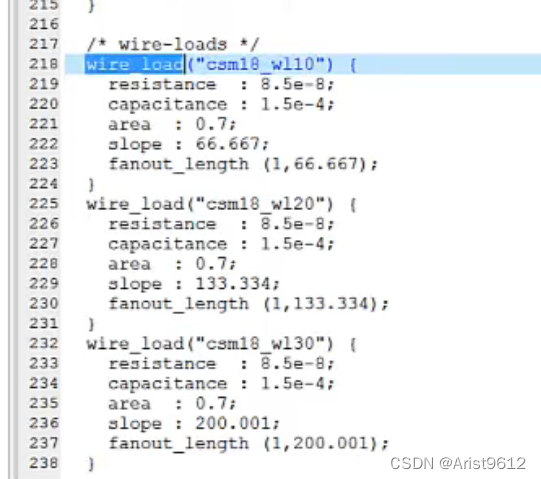

3.1 线负载模型

- 根据连线所接入的负载来计算线延迟,但是没有考虑连线长度

- 工艺厂会提供不同规模的线负载模型,百万门级、千万门及等等,实际延迟信息通过已经生产出的电路统计获得。具体选什么需要和厂商沟通确认

3.2 拓扑结构模型

- 使用脚本提供物理信息,包括电路基本布局等,如IP位置、RAM位置,指导DC进行综合

- 实际可以使用线负载模型先综合一版本,得到初步的模块布局后,以该布局信息作为第二次拓扑综合的输入进行第二次综合,这样所得的时序、面积信息更为准确。

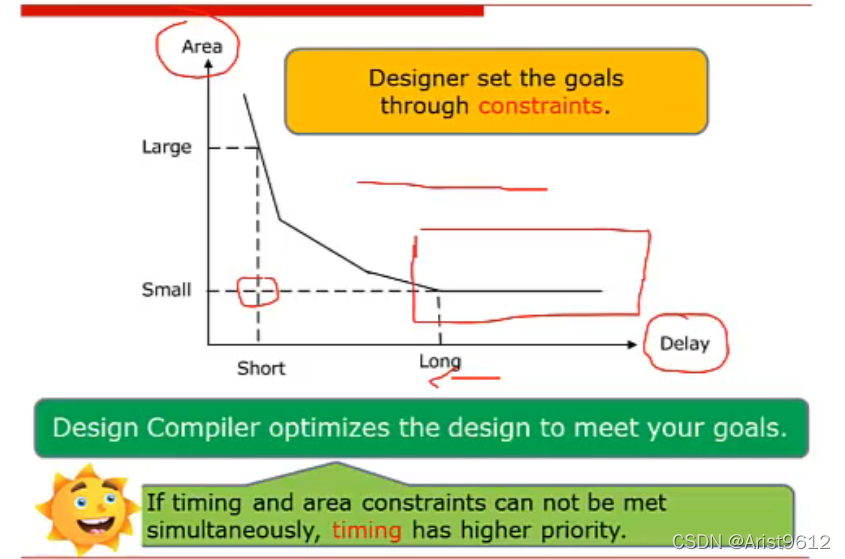

4. 面积、延迟的矛盾

- 我们期望,面积小、延迟低。但是这两个是相互制约的因素。综合优先保证时序。

- 面积越小、流片成本越低

- 面积大小取决于RTL质量,约束,工艺库等。相同功能需求不同人实现,面积不同,是因为RTL质量不同;约束越紧,需要用到的强驱动器件越多,面积越大;28nm工艺库器件面积>7nm工艺库器件。

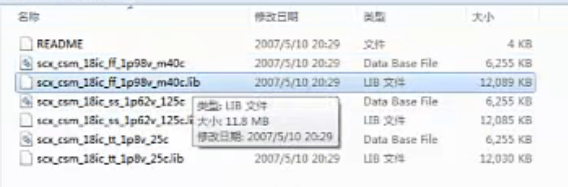

5. 工艺库文件

- 一般以lib后缀的文件是给人看的,同名没有lib的文件是给DC读取的

- 上图线负载模型的信息,有很多种,每种里面都包括电阻、电容、面积、斜率、fanout信息

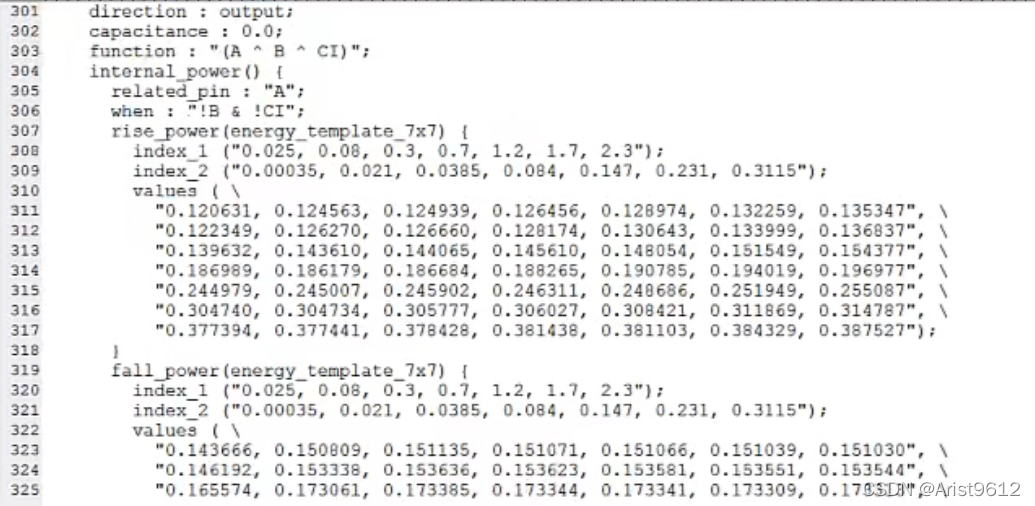

- 上图是一个加法器器件的工艺信息,包括引脚信息,器件功能信息

- 上图是加法器续表,实际上是多个查找表,根据idx_1/2对values进行索引,idx1/2分别是输入转换时间和扇出负载电容,根据这两个得到延迟信息。

6. synopsys_dc.setup

- DC设置文件,名称是固定的,DC只认识这个

- 一般设定路径信息、工艺库等信息

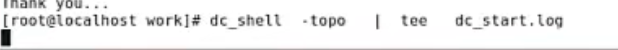

- -topo运行在拓扑模式

- | 管道符号,表示将上一步命令的结果交给后面的命令执行

- tee dc_start.log 将启动时候的打印信息输出到log

6万+

6万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?