前言

上一篇文件介绍了vivado的Dynamic Phase Shift功能,但是该功能无法在Bitfile运行期间动态改变输出时钟的相位,经过搜索发现MMCM的Dynamic Reconfig选项可以在Bitfile运行期间动态改变输出时钟的相位,本文主要介绍如何使用MMCM的DRP接口。

基础介绍

参考文档:

(1)MMCM and PLL Dynamic Reconfiguration

链接:https://pan.baidu.com/s/1OYklF0EszYlHMRf6CD6apw?pwd=atmp 提取码: atmp

(2)ug476-7-series-user-guide

链接: https://pan.baidu.com/s/1wmqCm6NbfcYpe_8k2yNR-w?pwd=76u2 提取码: 76u2

MMCM有五个用户可访问的配置位组,允许重新配置单个时钟输出。五个配置位组分别是分频组、移相组、锁定组、过滤器组和电源组。其中锁定组、过滤器组和电源组是固定的,一般不需要我们去进行设置,需要操作的主要是分频组和移相组。

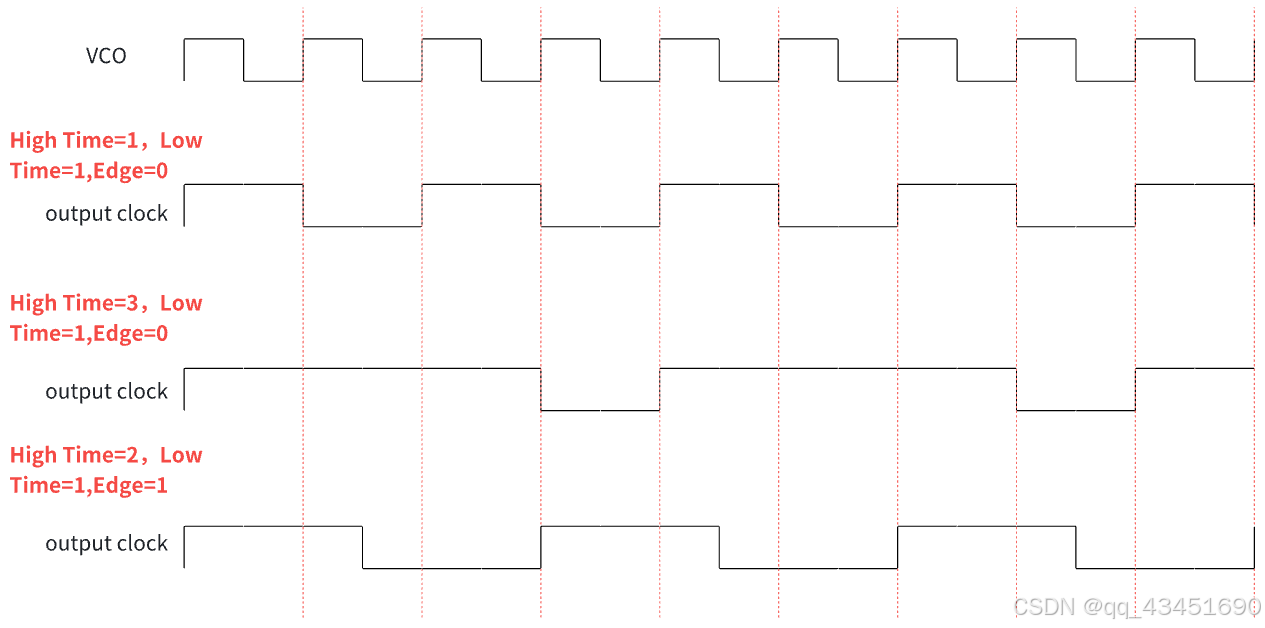

1、Divider Group

具体的参数有下面四个:

High Time:

高电平计数器,设置输出分频时钟的高电平时间为多少个VCO时钟周期

Low Time:

低电平计数器,设置输出分频时钟的低电平时间为多少个VCO时钟周期

No Count:

调用该参数之后将会禁用高电平和低电平计数器。分频器只生成一分频的时钟。

Edge:

该参数控制由高电平到低电平的转换。迫使高电平时间计数器在计数结束时在下降沿上转换。常用于奇数分频,使边沿移动半个VCO周期,从而使占空比达到50%。

例如:如果有一个占空比50%的时钟,分频值设置为3,Edge参数被设置为1。此时,在一个时钟周期内高电平时间被设置为2,低电平时间将被设置为1。设置了Edge参数后,High Time时间和Low Time是将分别为1.5个时钟周期。

4分频设置:High Time:2,Low Time:2,No Count:0,Edge:0。

1分频设置:High Time:0,Low Time:0,No Count:1,Edge:0。

2、Phase Group

除了DIVCLK之外,每个输出时钟都有一个相移组与之相关联,具体参数如下:

Phase Mux:

相位选择,为输出时钟选择一个粗略的相位,数值为1~8,1表示其相移度数相对于VCO时钟为45°(360°/8),8表示其相移度数相对于VCO时钟为360°。

Delay Time:

延迟时间是一个计数器,用于计算VCO时钟周期数来延迟输出。这意味着时钟输出的可能相移与特定输出的分频值之间存在直接相关性。随着分频值的增加,可以使用更精细的移相器移位策略。延迟时间计数器允许最多64个VCO clcok周期的相位偏移。说明每计数一次,输出时钟就相对VCO时钟偏移1/64个VCO时钟周期。

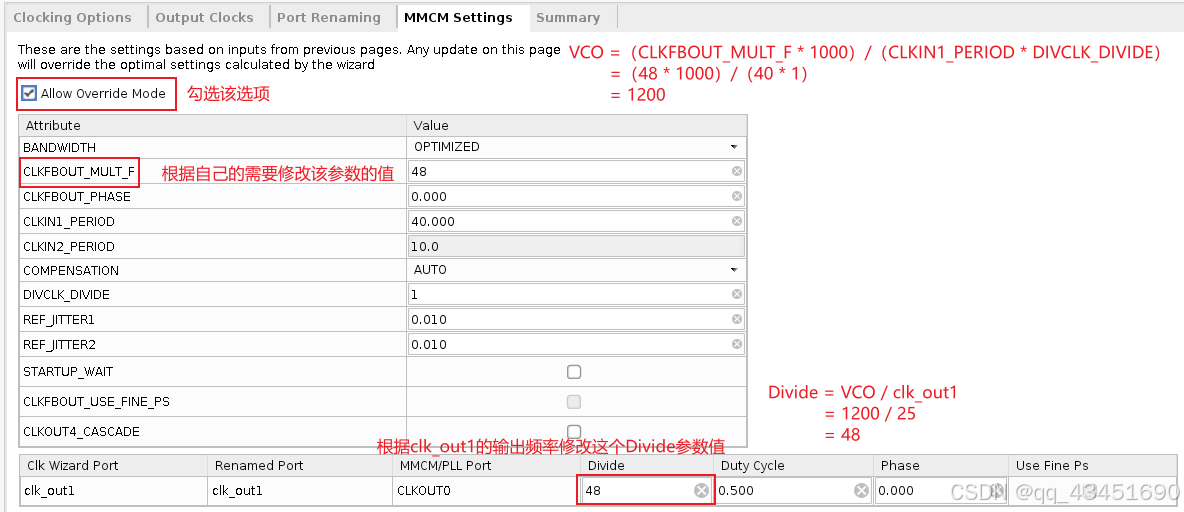

假设输出时钟为25M,设置VCO Frequency=1200M,那么输出时钟就是VCO的48分频(1200M/25M=48),就相当于使用VCO将输出时钟切分为48份,而一个时钟周期是360°,360°/48=7.5°,说明Delay Time每设置一次,输出时钟的相位就移动7.5°。

MX:

在重新配置期间(重新配置输出相移度数),这个参数必须被设置为2'b00,不管之前的值是多少。这个参数确保了可以按照预期输出想要的相位。

3、DRP Registers

Table 1: ClkReg1 Bitmap for CLKOUT[6:0] and CLKFBOUT

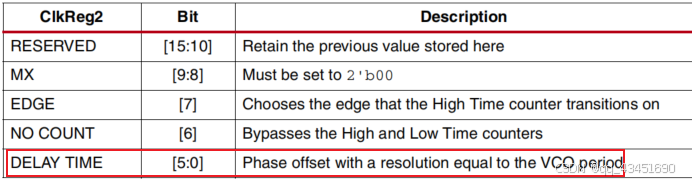

Table 2: ClkReg2 Bitmap for CLKOUT[6:0] and CLKFBOUT

从上面的介绍可以得知,如果想要修改输出时钟的相位,就需要设置DELAY TIME参数,因此需要操作ClkReg2寄存器。

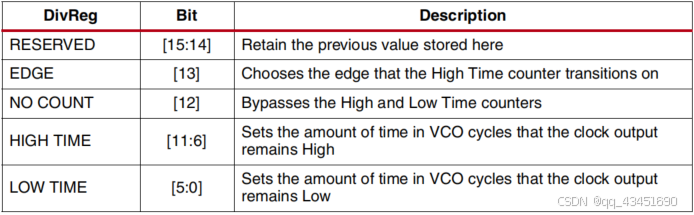

The register bitmap associated with the input divider D is shown in Table 3. Only a single register is needed because there is no phase adjustment on the input divider.

Table 3: DivReg Bitmap

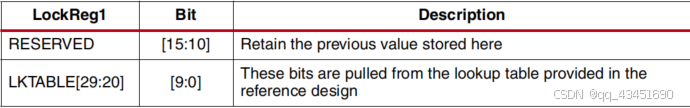

Three additional LOCK configuration registers must also be updated based on how the MMCM is programmed. These values are automatically setup by the reference design.

Table 4:** LockReg1 Bitmap**

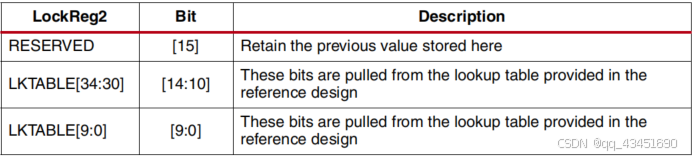

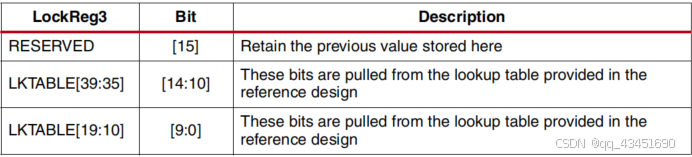

Table 5: LockReg2 Bitmap

Table 6: LockReg3 Bitmap

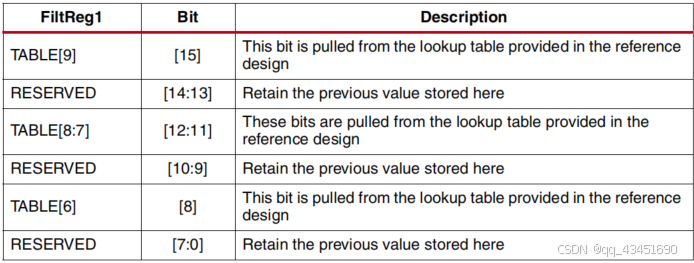

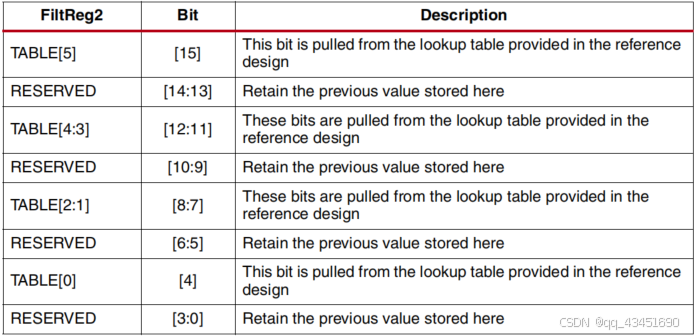

The filter group is composed of 10 bits that are stored on two registers. The register layouts are shown in Table 7 and Table 8.

Table 7:FiltReg1 Bitmap

Table 8: FiltReg2 Bitmap

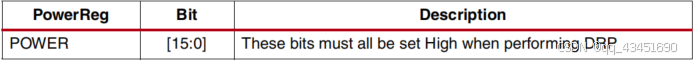

The power bits are stored in one register whose layout is shown in Table 9.

Table 9: PowerReg Bitmap

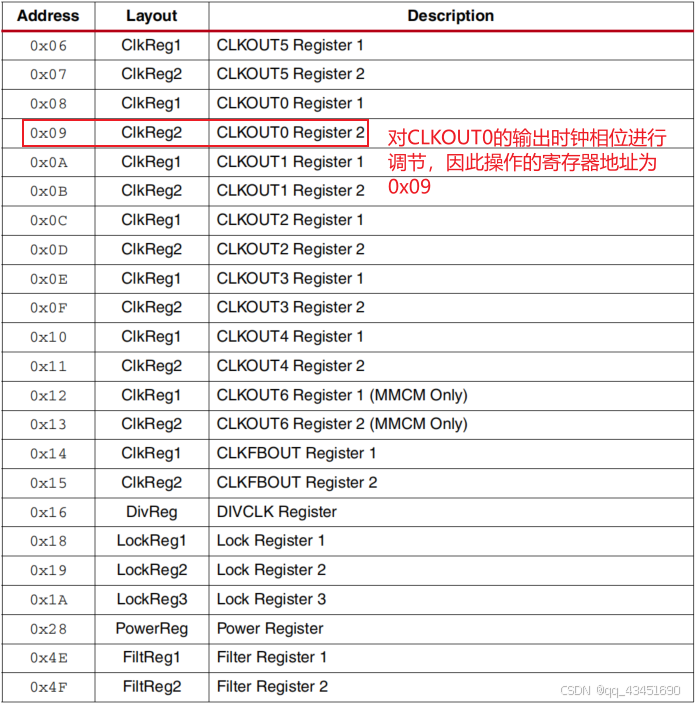

4、DRP Address Map

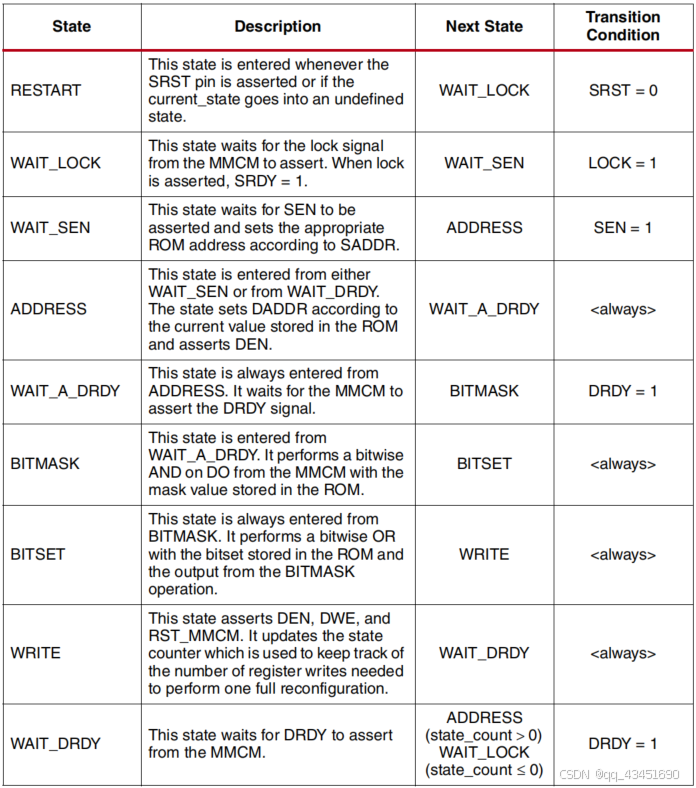

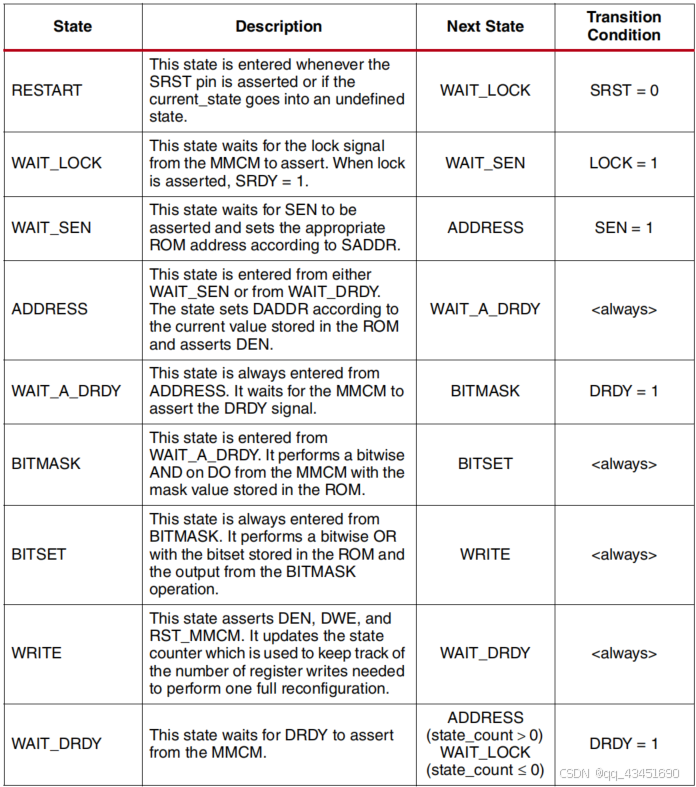

5、DRP State Machine

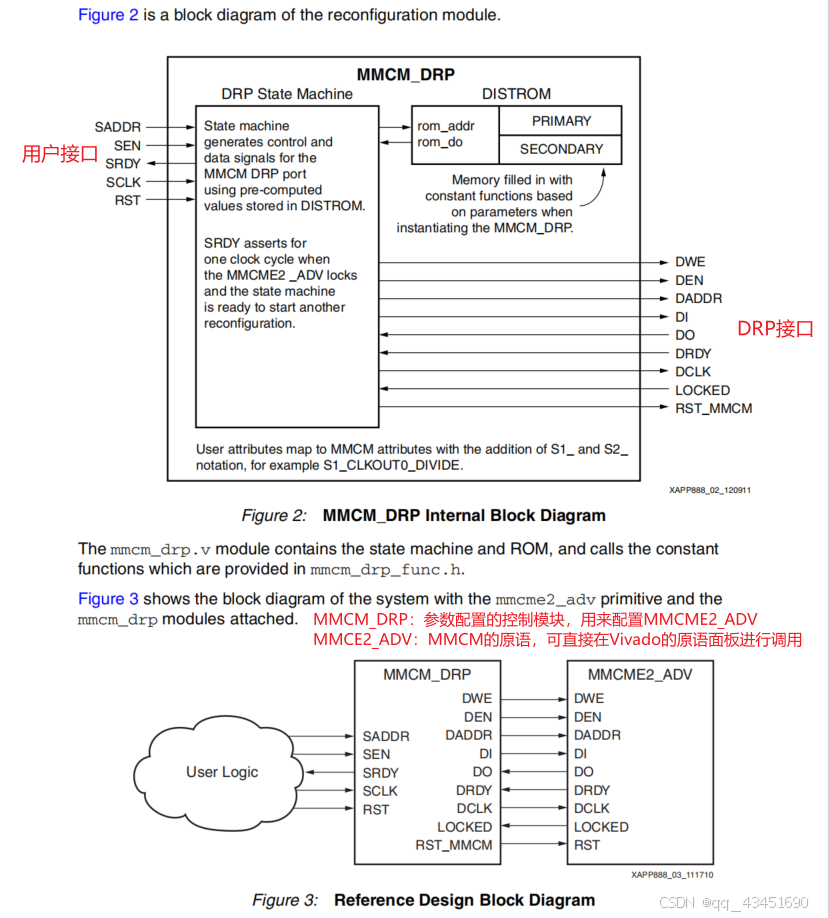

6、DRP Reference Design

参考设计使用处理MMCM地址的状态机驱动DRP端口,读取前面的值,屏蔽需要更改的位,设置新值,最后将该值写入MMCM DRP端口。

6.1 DRP State Machine

The operations that must be implemented to reconfigure one value in the MMCM are:

• Assert RST to the MMCM (do not deassert)

• Set DADDR on the MMCM and assert DEN for one clock cycle

• Wait for the DRDY signal to assert from the MMCM

• Perform a bitwise AND between the DO port and the MASK (DI = DO and MASK)

• Perform a bitwise OR between the DI signal and the BITSET (DI = DI | BITSET)

• Assert DEN and DWE on the MMCM for one clock cycle

• Wait for the DRDY signal to assert from the MMCM

• Deassert RST to the MMCM

• Wait for MMCM to lock

(1)复位MMCM

(2)设置要操作的MMCM寄存器地址,并将DEN信号拉起一个时钟周期

(3)等待MMCM的DRDY信号被拉起

(4)在DO端口和MASK(DI = DO & MASK)之间执行位和,将寄存器对应Bit置0

(5)在DI端口和BITSET(DI = DI | BITSET)之间执行位或,将寄存器对应Bit置1

(6)将MMCM上的DEN和DWE信号拉高一个时钟周期

(7)等待MMCM的DRDY信号被拉起,循环上述操作,写入所有寄存器;

(8)若所有的寄存器全部修改完成,释放MMCM的复位信号,等待MMCM的输出时钟锁存

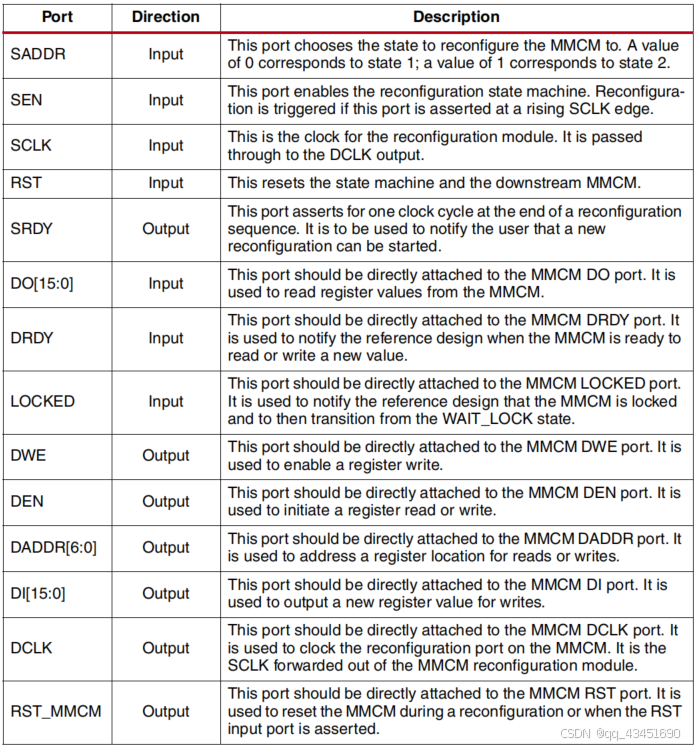

6.2 Reconfiguration Module Ports

用户操作接口信号介绍:

SADDR:该端口选择重新配置MMCM的状态。值0对应状态1;值1对应状态2

SEN:该端口启动重新配置状态机。如果该端口处于上升的SCLK边缘,则触发重新配置

SCLK:重新配置模块时钟,被传递到DCLK输出

RST:重置状态机和下游MMCM

SDRY:该端口在重新配置序列结束时上拉一个时钟周期,将用于通知用户可以重新开始新的重新配置。

DO:用于从MMCM读取寄存器的值

DRDY:用于在MMCM准备好读取或写入新值的时候通知参考设计。

LOCKED:用于通知参考设计MMCM被锁定,然后从WAIT_LOCK状态转换。

DWE:启用寄存器写入(写使能)

DEN:读写使能信号

DADDR:地址控制,用于寻址用来读或写的寄存器位置。

DIN:写配置,输出一个新的寄存器值用于写操作。

DCLK:配置时钟,用于MMCM的重新配置端口的时钟,它是从MMCM重构模块转发出去的SCLK。

RST_MMCM:用于在重新配置期间复位MMCM,或者RST端口被复位的时候。

7、DRP设计介绍

本文是对一个输出频率为25M的时钟进行动态调相。开发平台基于Vivado2022.1,器件使用的是Ulstrascale+。

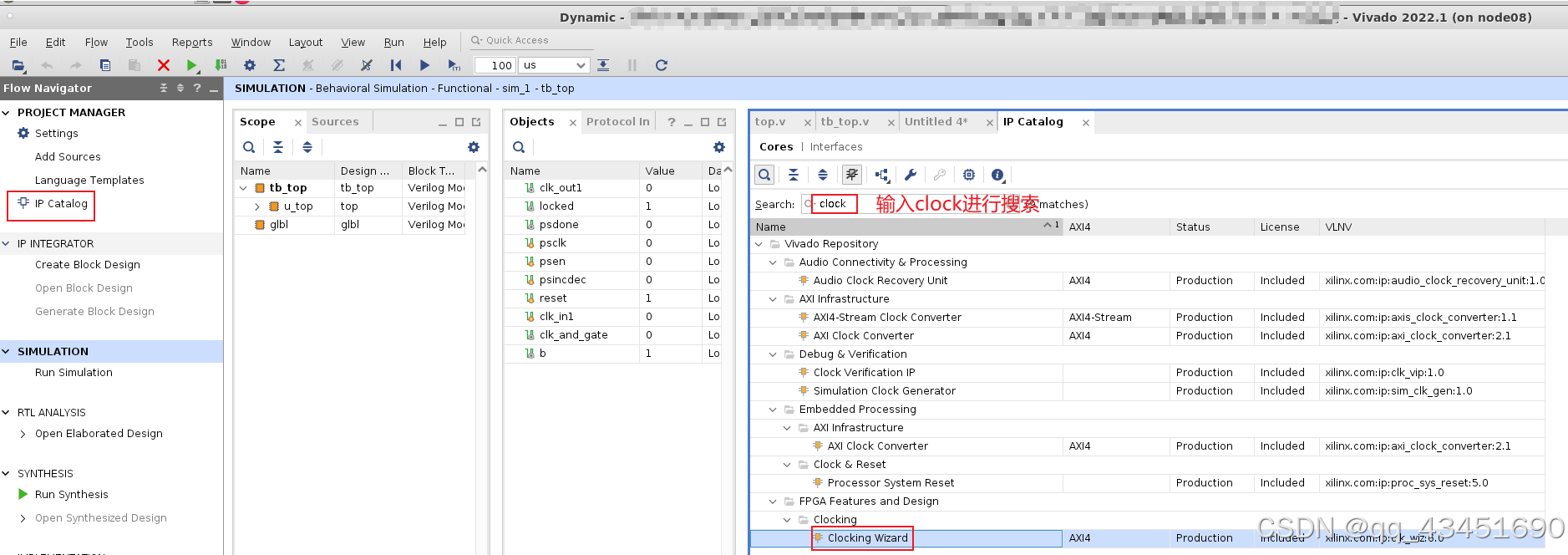

7.1 IP配置说明

(1)打开vivado,创建好工程后,点击IP Catalog,在出现界面的搜索框中输入clock进行查找,双击Clocking Wizard进入IP配置界面;

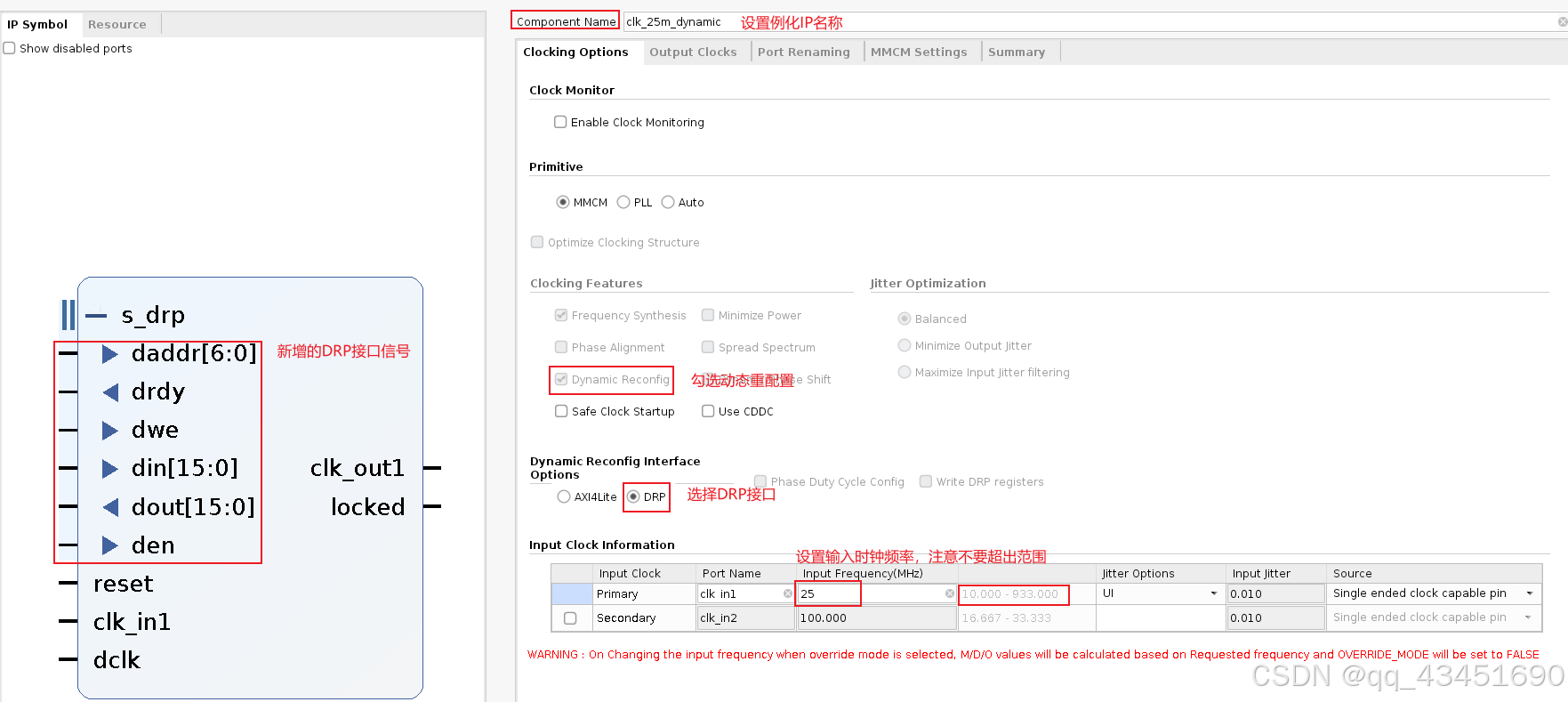

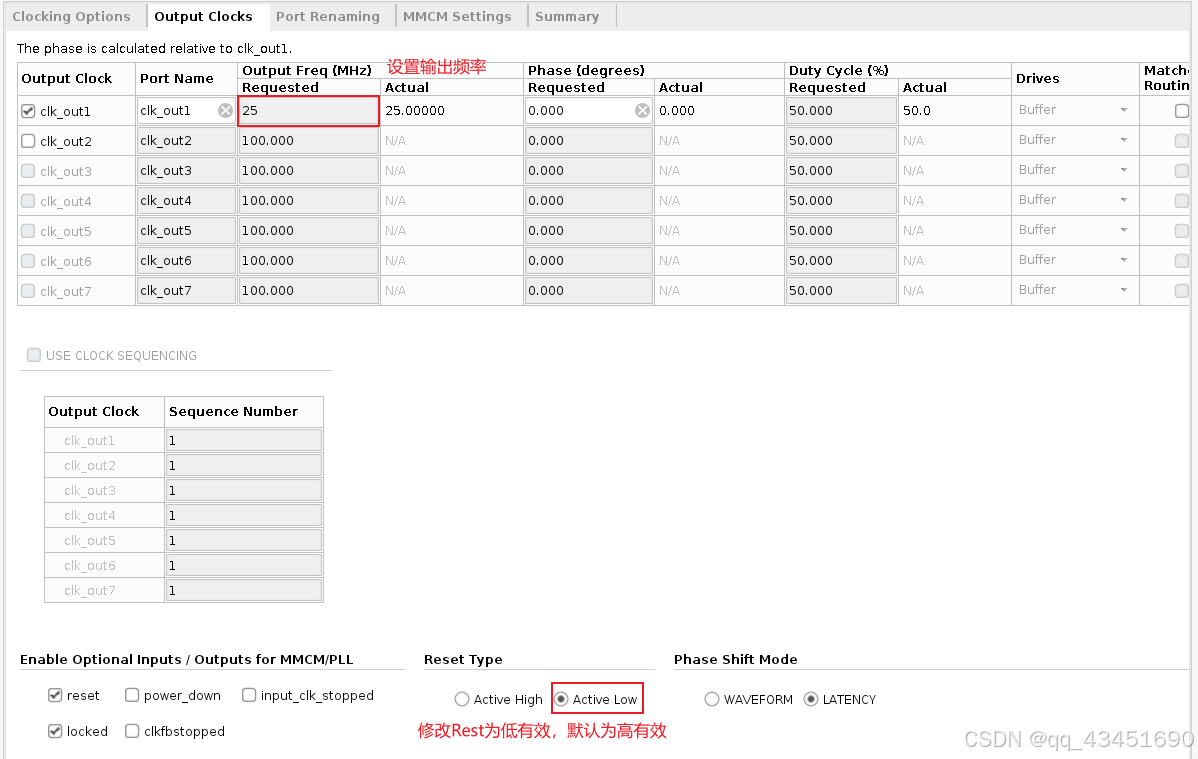

(2)配置MMCM

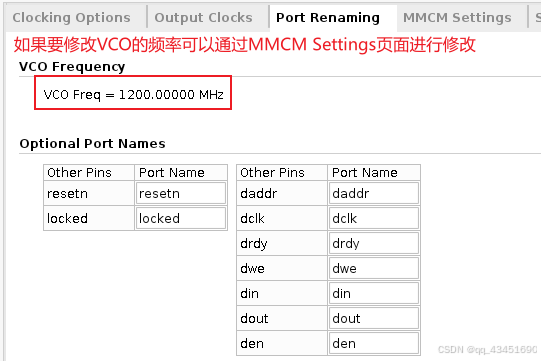

(3)根据需求修改VCO频率

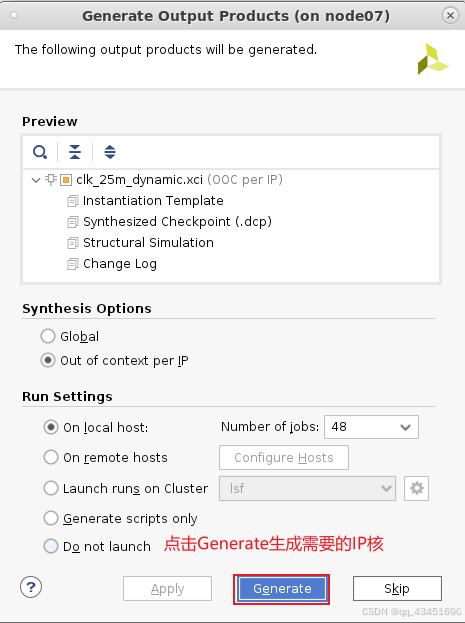

(4)生成IP核

7.2 相移代码介绍

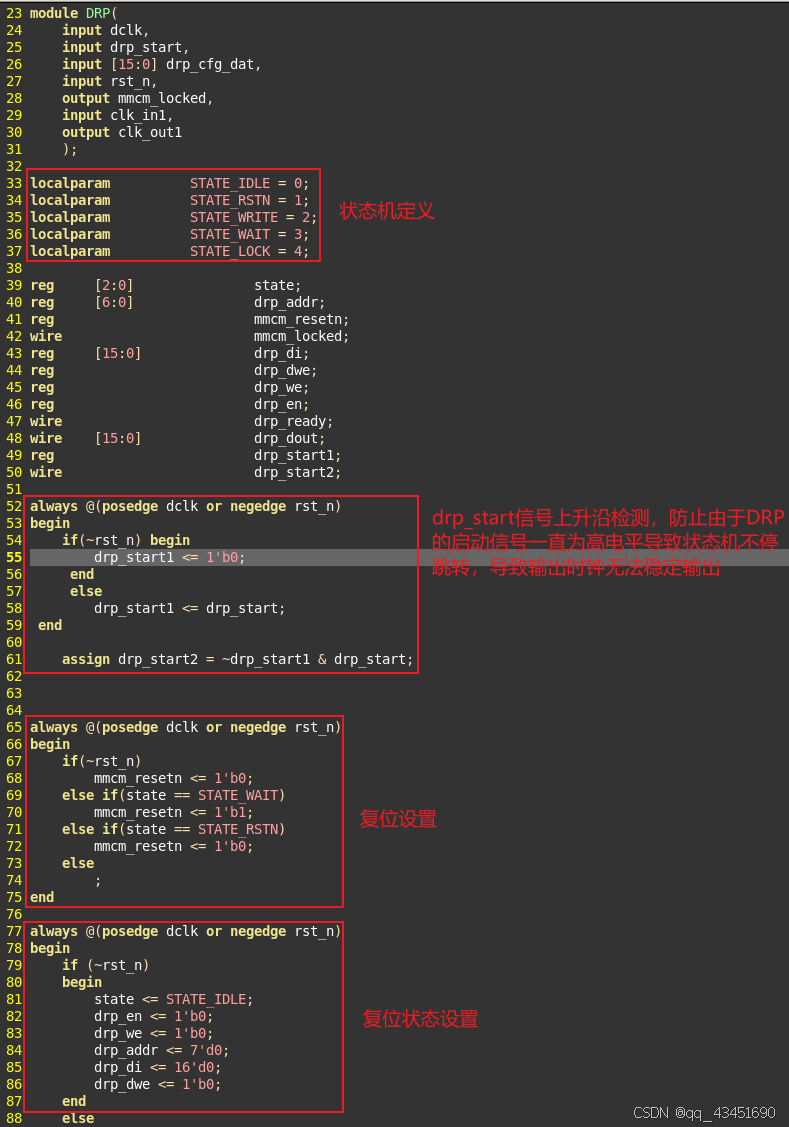

通过文档可以看到,实现动态重配置需要通过状态机跳转来实现,根据需求可知状态机的跳转流程如下所示:

(1)复位MMCM

(2)复位完成之后,设置需要操作的地址和相位设置参数

(3)当DRDY信号被拉起之后,启用寄存器写使能,将操作地址写入寄存器

(4)等待MMCM输出锁定,输出对应相移的时钟

(5)完成之后进入等待状态,等待下一次的相移操作

由于output clock=25M,VCO Fre=1200M,Delay Time=1200/25=48,因此该输出时钟最多调相48次。

因为是对CLKOUT1的输出时钟进行调相,因此操作寄存器地址Address=0x09。

7.3 仿真代码

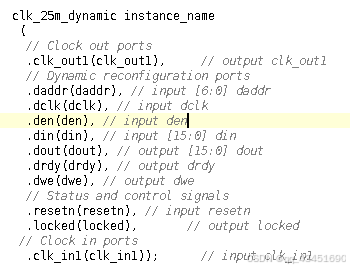

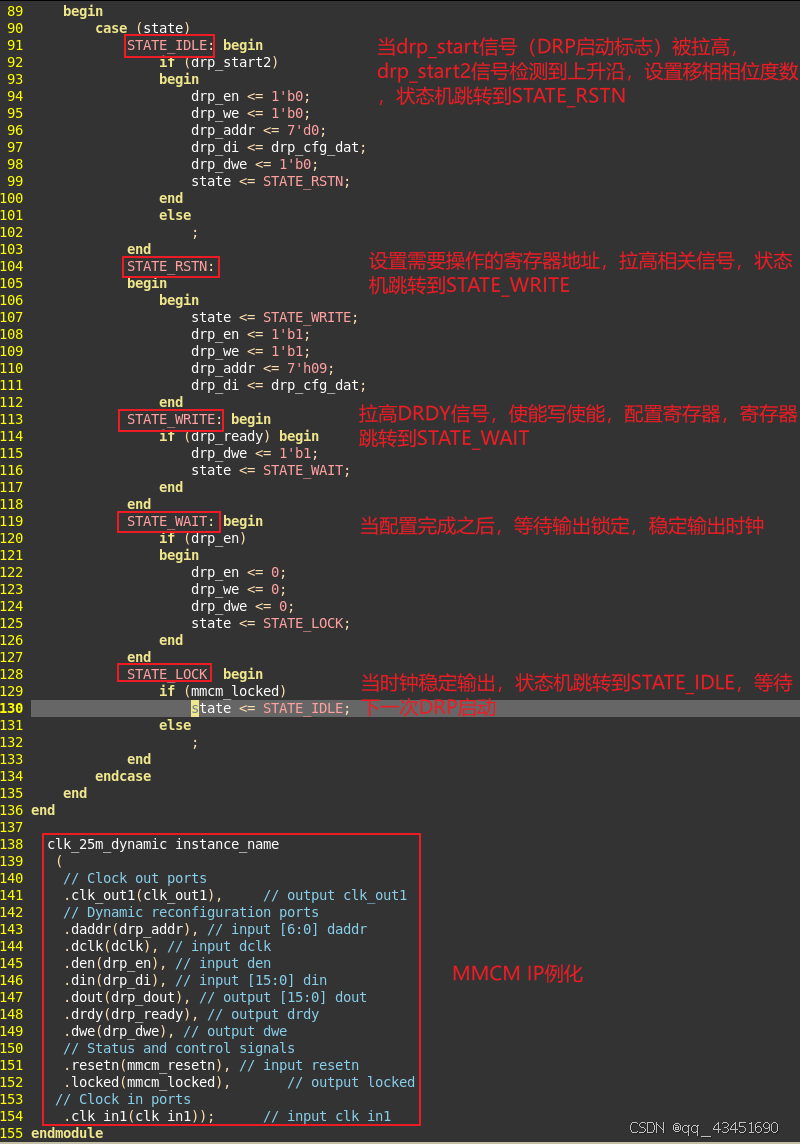

(1)IP核例化代码

(2)顶层文件代码

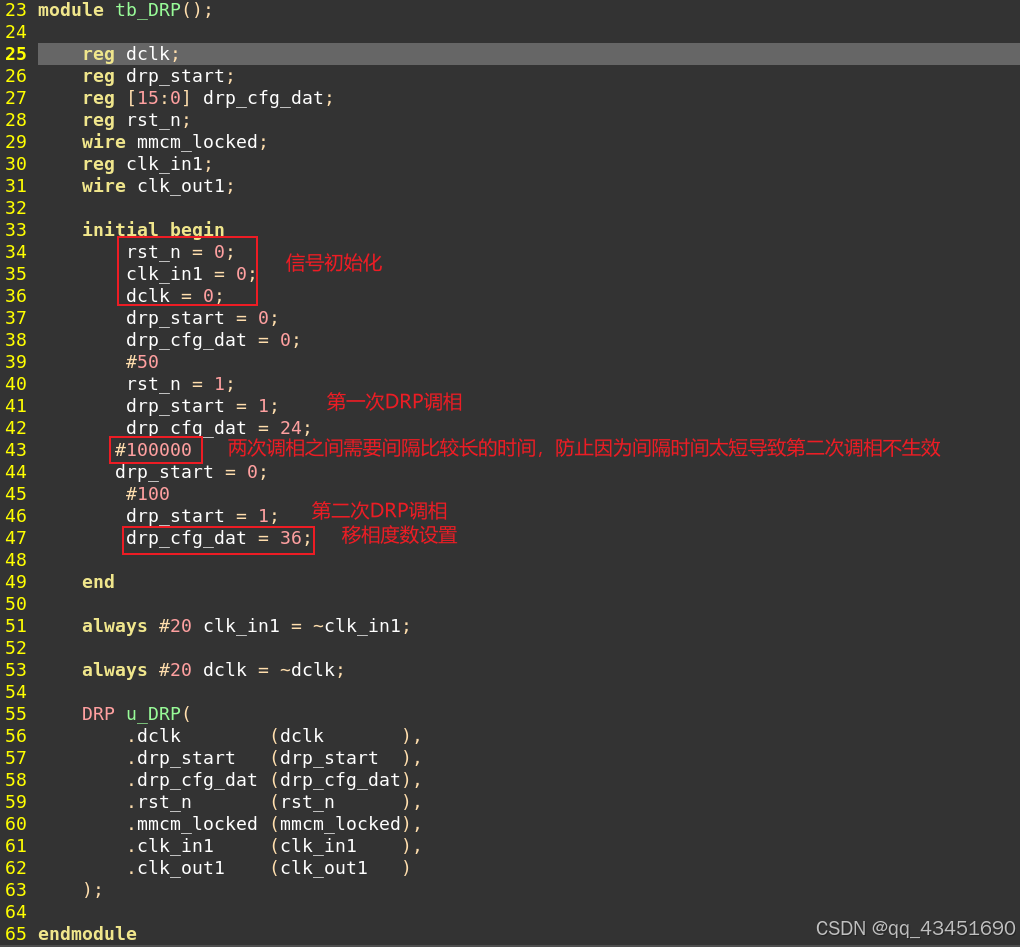

(3)测试代码

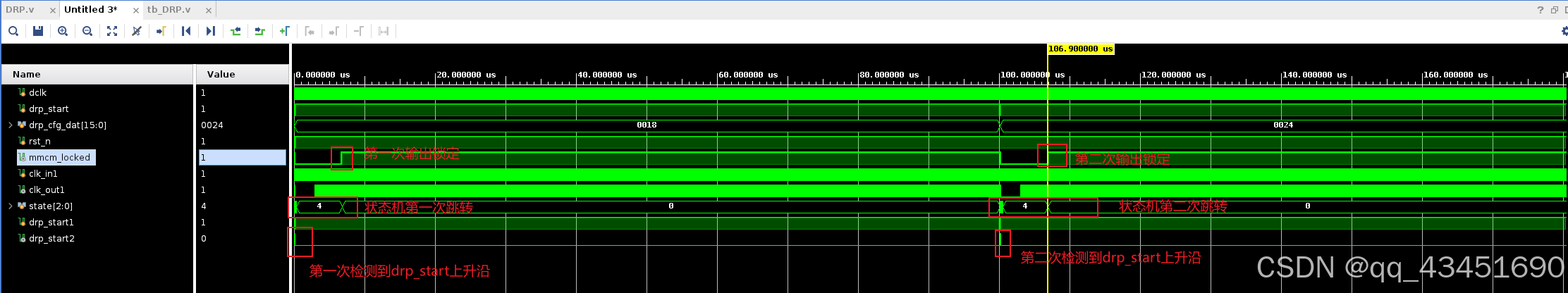

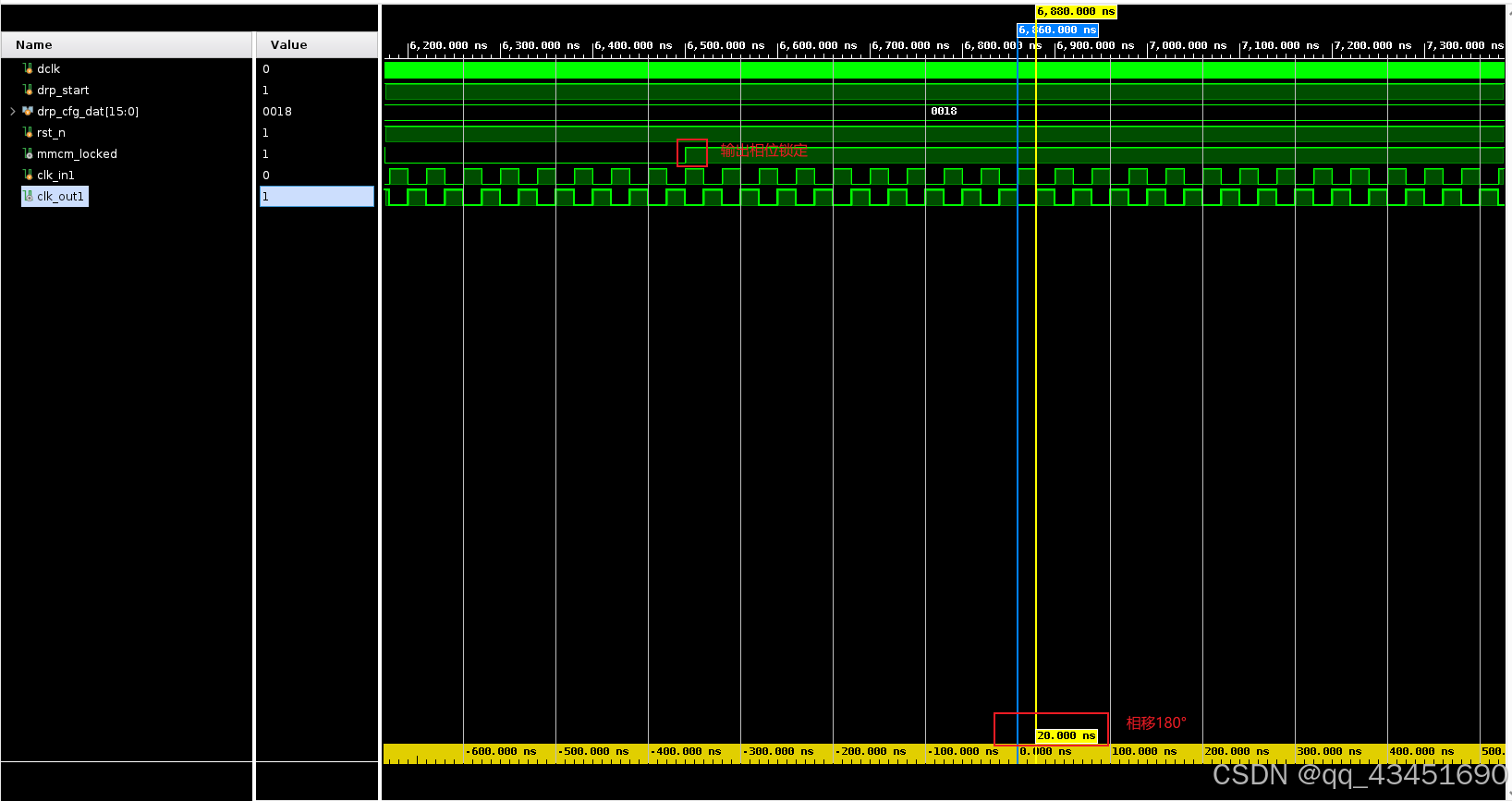

8、波形图

(1)两次动态调相

(2)相移180°

6526

6526

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?