一些基本概念

- MLU Core:是寒武纪硬件的基本组成单元。每个MLU Core是具备完整计算、IO和控制功能的处理器核心,可独立完成一个计算任务,也可与其他MLU Core协作完成一个计算任务

- Cluster:每4个MLU Core构成一个Cluster,每个Cluster内还会包含一个额外的Memory Core和一块被Memory Core和4个MLU Core共享的SRAM(Shared RAM,共享存储单元)

- Memory Core:不能执行向量和张量计算指令,只能用于SRAM和DDR(Double Data Rate Synchronous Dynamic Random Access Memory,双倍速率同步动态随机存储器,DDR SDRAM简称为DDR)和MLU Core之间的数据传输

- DDR RAM=DDR SDRAM:DDR原理就是它可以在一个时钟读写两次数据,从而使得数据传输速度加倍;S(Synchronous)指数据的读写需要时钟来同步

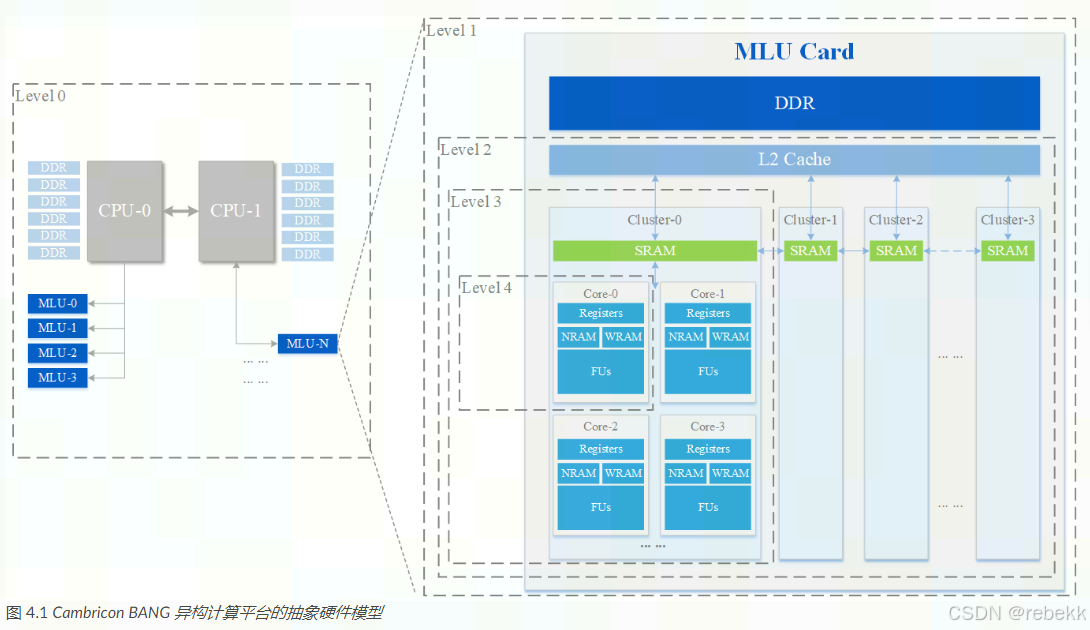

Cambricon BANG异构并行计算平台的整个抽象硬件模型概览

- 概述:由通用处理器和多个MLU领域专用处理器组成

- MLU负责核心的大规模并行计算

- 通用处理器作为控制单元,负责复杂控制和任务调度等工作

- 整个抽象硬件模型分为5个层级,每个层级都包括抽象的控制单元、计算单元、存储单元。整个抽象硬件模型可通过增加服务器数量、板卡数量、芯片数量、Cluster数量或MLU Core数量的方式自由扩展计算能力,也可通过在各层增加存储容量的方式自由扩展存储容量。此外,还可以减少层次来适应具体需求,如在边缘侧场景中可省去板卡级,直接由主机侧的CPU与MLU芯片互联;在一些计算需求不高的终端侧场景中,还可直接省去板卡、芯片级和Cluster级,将MLU Core作为主机侧CPU的协处理器

- 【0】服务器级:由多个CPU构成的控制单元、本地DDR存储单元和多个MLU板卡构成的计算单元组成

- 【1】板卡级:每个MLU板卡由本地控制单元、DDR存储单元和多个MLU芯片构成的计算单元组成

- 【2】芯片级:每个芯片由本地控制单元、本地存储单元(如L2 Cache)以及一个或多个Cluster构成的计算单元组成

- 【3】处理器簇(Cluster)级:每个Cluster由本地控制单元、共享存储(SRAM)、以及多个MLU Core构成的计算单元组成

- 【4】MLU Core级:每个MLU Core由本地控制单元、私有存储单元和计算单元。在MLU Core内部支持指令级并行和数据级并行

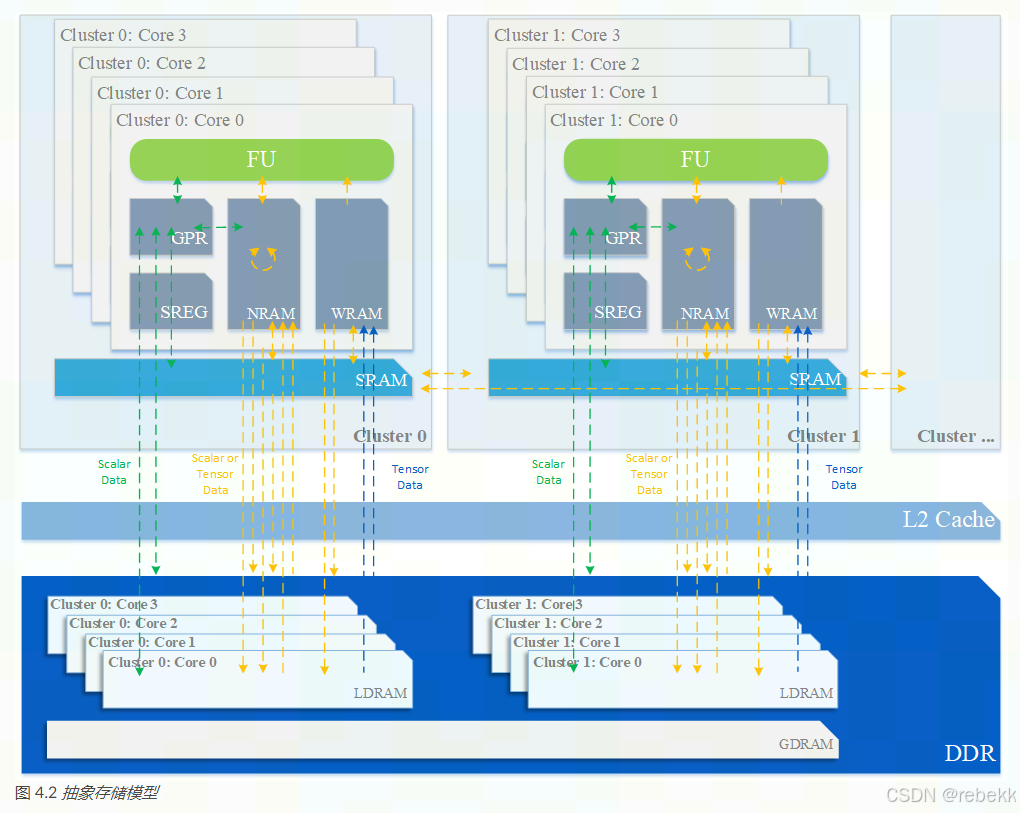

存储模型

- 存储层次

- GPR:每个MLU Core和Memory Core私有的存储资源。所有标量数据在参与运算前都要先加载到GPR

- NRAM:每个MLU Core私有的片上存储空间。所有向量、张量数据在参与运算前都要先加载到NRAM上,也可用于存储一些运算过程中的临时标量数据。

- WRAM:每个MLU Core私有的片上存储空间。主要用于存放卷积运算的卷积核数据(其上特殊的数据布局使得能高效实现卷积运算)

- SRAM:一个Cluster内所有MLU Core和Memory Core都可以访问的共享存储空间。SRAM可用于缓存MLU Core的中间计算结果,实现Cluster内不同MLU Core或Memory Core之间的数据共享及不同Cluster之间的数据交互。

- 因为同一个Cluster内所有MLU Core和Memory Core都可自由读写SRAM,硬件不保证所有读写操作之间的顺序,所以软件需要插入同步原语来保证数据依赖

- L2 Cache:是位于片上的全局存储空间,主要用于缓存指令、Kernel参数和只读数据,用户不能访问

- LDRAM:每个MLU Core和Memory Core私有的存储空间,可用于存储无法在片上存放的私有数据。LDRAM属于片外存储,不同MLU Core和Memory Core之间的LDRAM相互隔离,软件可以配置其容量。与GDRAM相比,LDRAM的访存性能更好,因为LDRAM的访存冲突比较少

- GDRAM:与LDRAM类似,GDRAM也是片外存储。位于GDRAM中的数据被所有的MLU Core和Memory Core共享。GDRAM空间的作用之一是用来在主机侧与设备侧传递数据,如Kernel的输入、输出数据等。目前GDRAM空间只能由主机侧分配和释放,设备侧只支持GDRAM的读写操作

- 数据迁移

- 显式数据迁移:由用户调用对应的数据移动接口来完成

- 隐式数据迁移:由编译器自动完成,无需用户参与。MLU要求所有标量计算在GPR中进行,当定义在LDRAM/GDRAM/SRAM/NRAM上的标量参与运算时,编译器会自动插入load指令将数据搬移到GPR中,在计算完成后再通过编译器插入的store指令将GPR上的结果写回LDRAM/GDRAM/SRAM/NRAM

- 访存一致性

计算模型(具体性能调优实践待续)

- 核内并行和同步:MLU硬件同时支持数据级并行和指令级并行

- 数据级并行:一条指令中同时处理多个数据。向量指令就是典型的数据级并行

- 指令级并行:MLU硬件同时提供了多条可以并行执行的流水线,分别对应不同功能。位于同一条流水线中的指令串行执行,位于不同流水线中的指令并行执行,从而实现不同流水线之间的指令级并行。

- MLU Core有4条指令流水线:IO流、Move流、Compute流、Scalar流

- Memory Core有3条指令流水线:IO流、Move流、Scalar流

- 核间并行和同步

抽象硬件模型支持多个MLU Core协同完成同一个计算任务。对于只需要一个Cluster的任务,硬件会启动4个MLU Core和1个Memory Core分多轮迭代处理所有Task。同一轮迭代的Task之间可以通过共享SRAM通信,也可通过核间同步原语实现同步- 局部同步:同一个Cluster内不同MLU Core和Memory Core之间的同步

- 全局同步:多个Cluster之间的同步

1954

1954

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?