Linux下基于cadence的verilog仿真(接上篇)

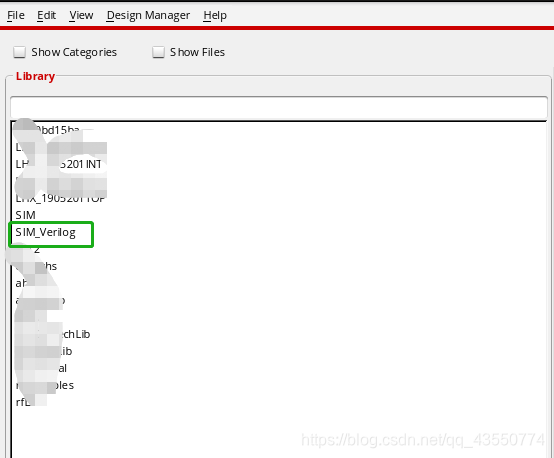

首先,为了方便我们以后可以很好地区分,我们可以新建一个库,这里我起名为SIM_Verilog。

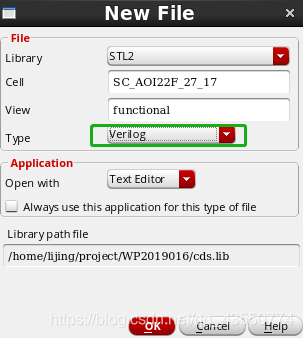

接下来在要仿真的电路图的库中添加functional单元库。

这里新建单元,Type选择Verliog,选择OK即可。

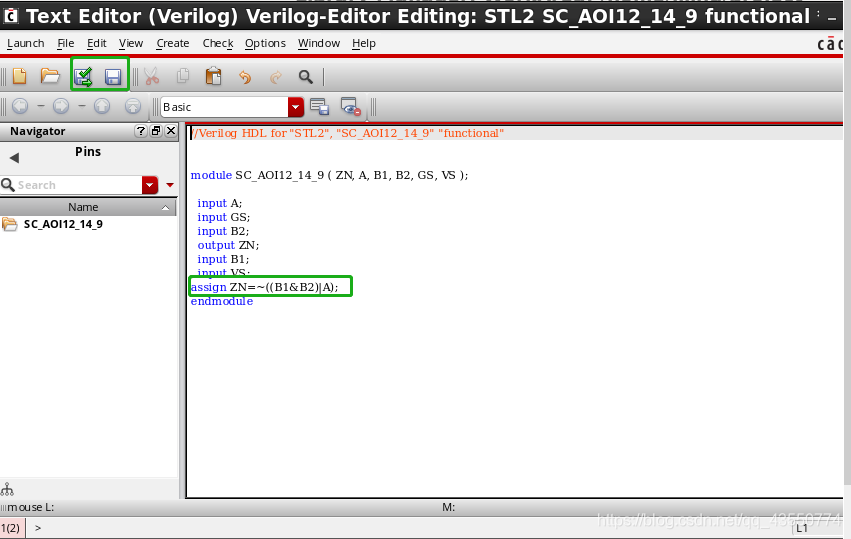

在跳转弹出的窗口用Verilog语言添加功能,选择保存检查即可。(没有学过Verilog语言的童鞋们可以自己在网上搜帖子,很好学的)。

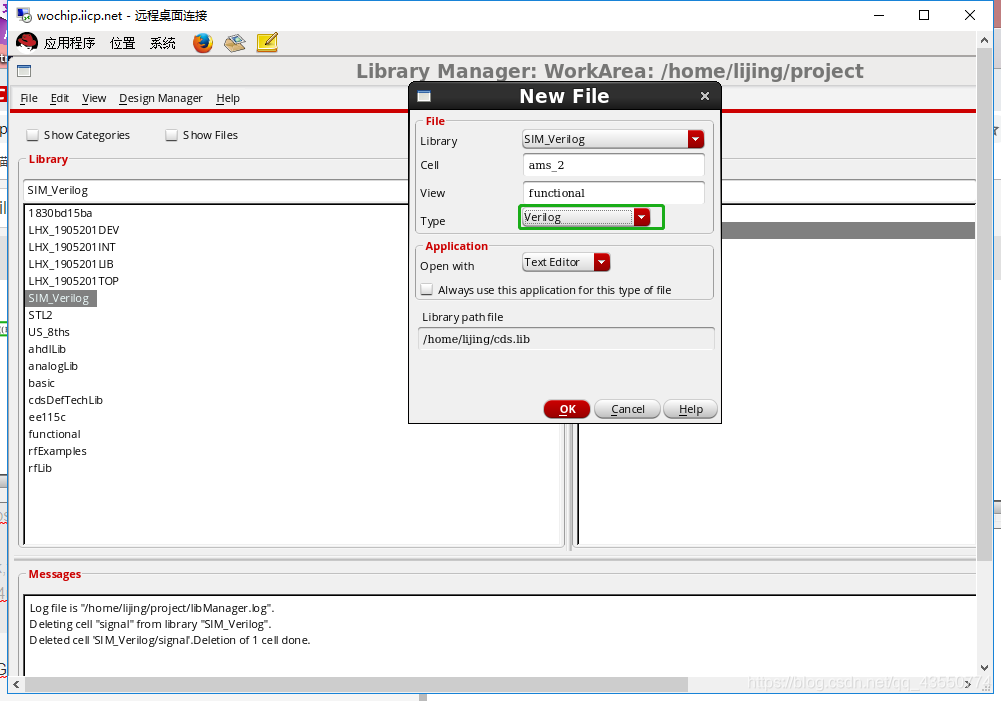

接下来我们需要写一个sigGen,作为电路激励。

具体步骤为:新建一个单元,Type选择Verilog。

这里在弹出的窗口写出sigGen的代码,时间可以自己给定,sigGen的端口可以尽量给多一些,方便以后使用,建立好SigG

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

793

793

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?