FPGA开发流程

开发流程

1、设计定义

项目需要做什么,了解系统的功能,如果是大型的项目还会划分模块

2、设计输入

通过使用verilog、VHDL、成熟的IP核或者通过画原理图的方式进行逻辑输入设计

3、分析和综合

当逻辑输入设计完成后需要对其进行验证,该部分由软件部分进行验证,如果逻辑输入有问题需要检查语法错误或则重新设计设计输入

4、功能仿真

当分析和综合通过后应该进行功能性验证,针对项目设计定义的功能使用设计的逻辑输入验证其功能能否实现,一般的做法都是通过功能仿真的方式进行验证,比如软件逻辑分析仪,modelsim、vivado等软件自带的仿真工具进行仿真验证

功能仿真也称为行为仿真,主旨在于验证电路的功能是否符合设计要求,其特点是不考虑电路门延迟与线延迟,主要是验证电路与理想情况是否一致。也可以叫做RTL仿真(test bench)

5、布局布线

当我们的IO可以开始分配了我们首先需要分配IO,如果当前还没到IO分配的时候我们可以将IO分配放在最后,当IO分配完成后我们就可以通过软件进行布局布线,在芯片内部生成芯片电路

6、时序仿真

时序仿真也称为布局布线后仿真,是指电路已经映射到特定的工艺环境以后,综合考虑电路的路径延迟与门延迟的影响,验证电路能否在一定时序条件下满足设计构想的过程,能较好地反映芯片的实际工作情况,当时序仿真不通过的时候可能还会设计到时序约束的一个过程(在比较复杂的设计中也需要用到);

7、IO分配以及配置文件(bit流文件)的生成

如果在布局布线时未进行IO分配在该步骤进行IO分配并生成BIT流文件

8、配置(烧录)FPGA

时序通过了后需要通过硬件进行验证也就是最后一步的实物验证

9、在线调试

当系统出现问题运行不正常我们可以通过外部硬件示波器或者逻辑分析仪进行实际引脚信号抓取分析

例子

1、设计定义

1.1 需求

二选一多路器,两个输入IO(a,b)可以是高电平可以是低电平,一个sel选择信号

当sel为0时候输出按键1的状态

当sel为1时候输出按键2的状态

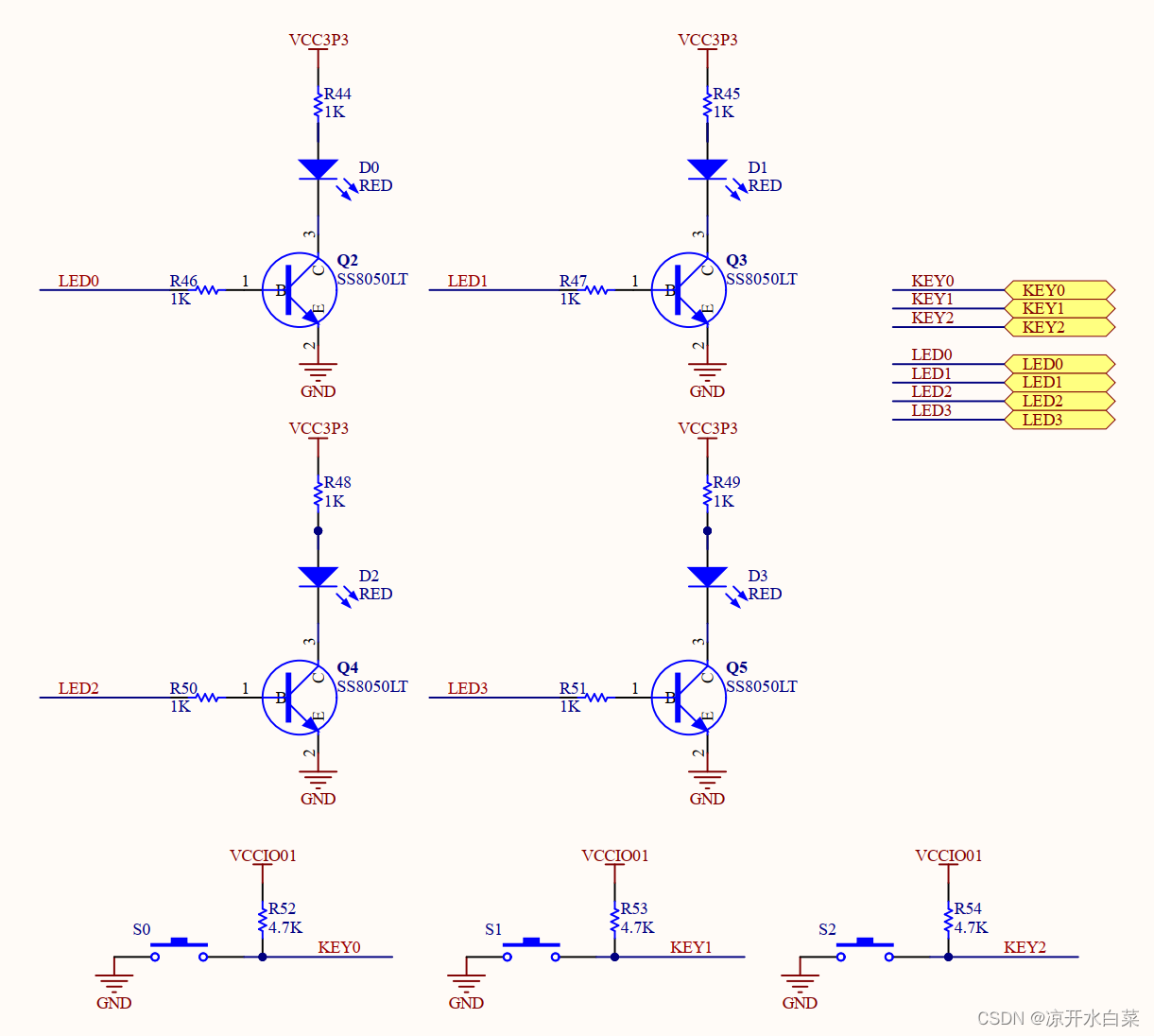

1.2 原理图

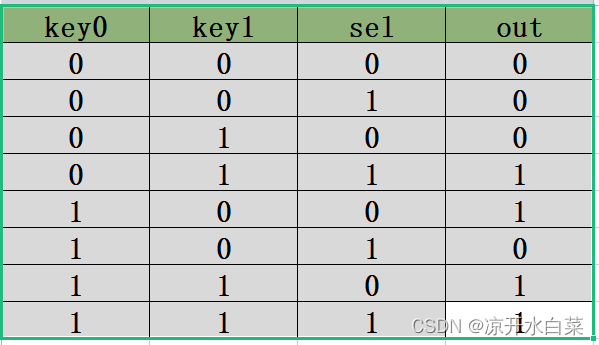

1.3 真值表

2、设计输入

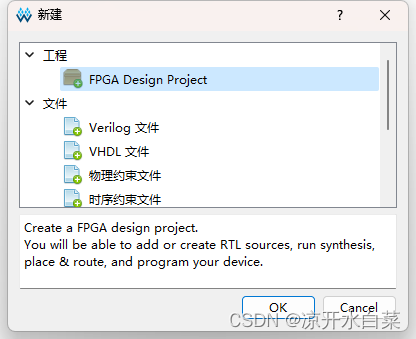

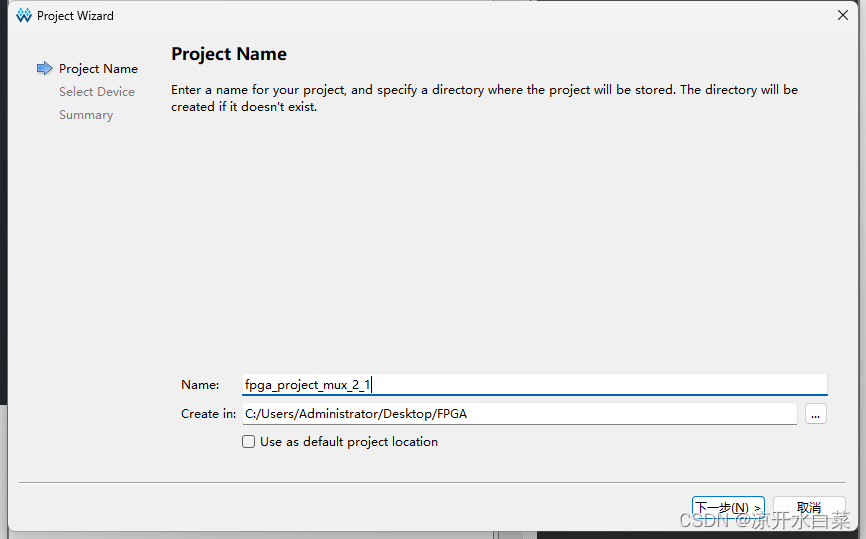

2.1 新建工程

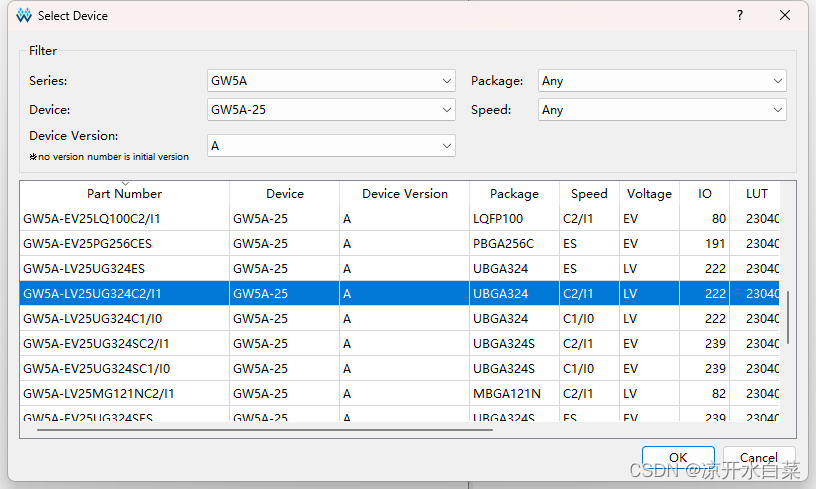

选择自己使用的芯片(我这里采用的是小梅哥的高云FPGA开发板)

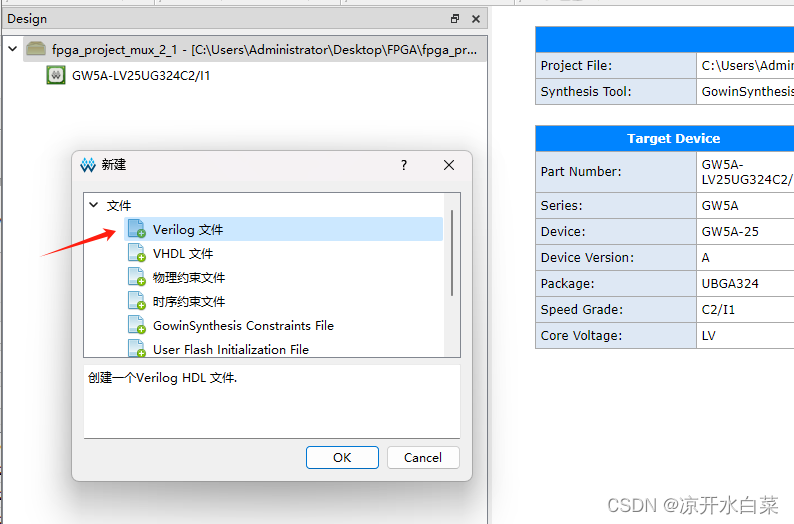

新建一个verilog文件

2.2 添加代码

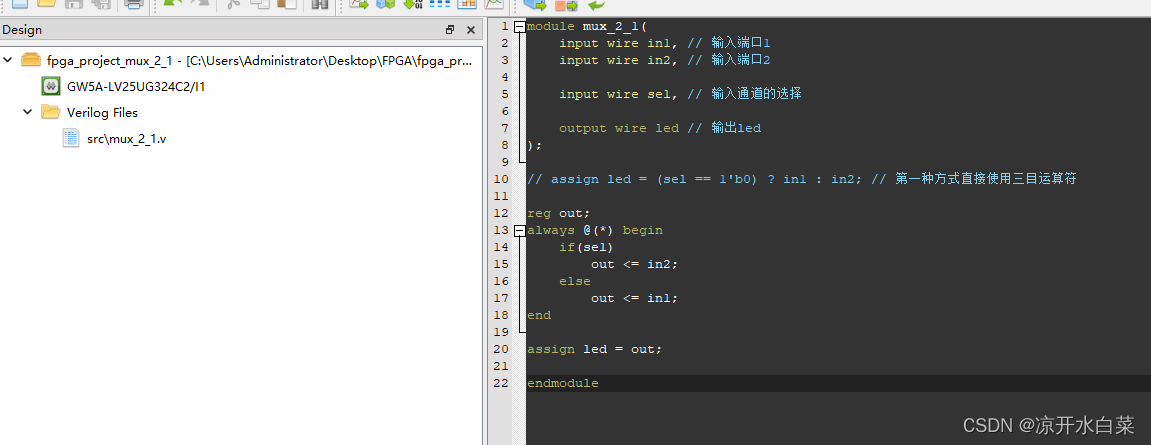

module mux_2_1(

input wire in1, // 输入端口1

input wire in2, // 输入端口2

input wire sel, // 输入通道的选择

output wire led // 输出led

);

// assign led = (sel == 1'b0) ? in1 : in2; // 第一种方式直接使用三目运算符

// 第二种方式是使用always的*触发方法ifelse判断

reg out;

always @(*) begin

if(sel

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5095

5095

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?