芯片介绍

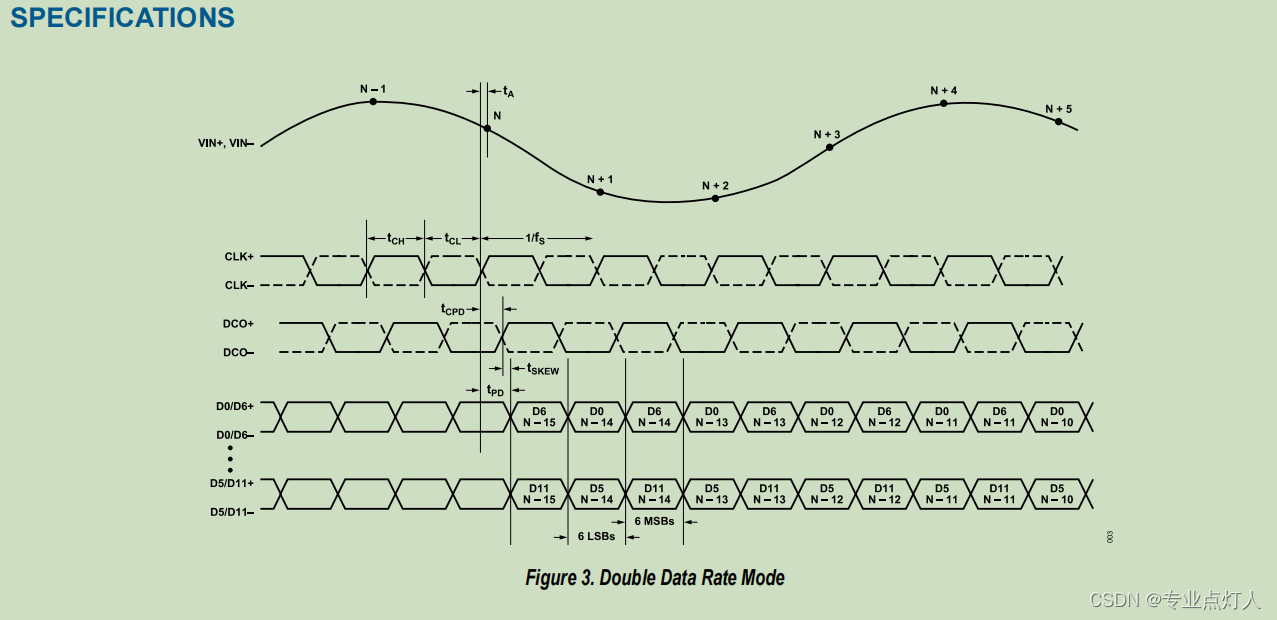

本次开发使用的国产adc CBM94AD34 该adc用来替代ad9434(封装管脚开发模式完全一样,由于 CBM94AD34数据手册过于简单,所以全部参照AD9434)ad9434是一款单通道12bit,采样率高达500Mhz的模数转换芯片,该芯片有sdr和ddr两种工作模式,本次开发采用的7系列fpga,adc采用的是ddr模式。

具体详情查看数据手册。

开发过程及思路

1.信号和时钟均为差分输入,使用IBUFDS原语使差分信号转为单端信号

IBUFDS_inst : IBUFDS

generic map (

DIFF_TERM => FALSE, -- Differential Termination

IBUF_LOW_PWR => TRUE, -- Low power (TRUE) vs. performance (FALSE) setting for referenced I/O standards

IOSTANDARD => "DEFAULT")

port map (

O => O, -- Buffer output

I => I, -- Diff_p buffer input (connect directly to top-level port)

IB => IB -- Diff_n buffer input (connect directly to top-level port)

);2.使用IDDR原语对双边缘数据进行分离和读取

```c

DR_inst : IDDR

generic map (

DDR_CLK_EDGE => "OPPOSITE_EDGE", -- "OPPOSITE_EDGE", "SAME_EDGE"

-- or "SAME_EDGE_PIPELINED"

INIT_Q1 => '0', -- Initial value of Q1: '0' or '1'

INIT_Q2 => '0', -- Initial value of Q2: '0' or '1'

SRTYPE => "SYNC") -- Set/Reset type: "SYNC" or "ASYNC"

port map (

Q1 => Q1, -- 1-bit output for positive edge of clock

Q2 => Q2, -- 1-bit output for negative edge of clock

C => C, -- 1-bit clock input

CE => CE, -- 1-bit clock enable input

D => D, -- 1-bit DDR data input

R => R, -- 1-bit reset

S => S -- 1-bit set

);

问题产生原因

FPGA的差分输入输出管脚硬件工程师设计板子时供电电压为1.8v,但配置为

LVDS后,软件提示报错说HRbank做差分输入输出时只能配置为LVDS_25,这就矛盾了,后来通过查阅资料,https://www.elecfans.com/d/1883119.html

https://xilinx.eetrend.com/blog/2022/100561754.html

这两篇写的比较详细

在第二篇文章中说到,HP BANk时当作为输入时vcco电压可以不为1.8v,此时内部端接电阻不可用,只能使用外部端接

虽未对HR BANk做同样文字描述但,表述为“对于图二检查表(HR BANK)上述类似”,可以理解为跟 HP BANk要求一样

所以在配置IBUFDS参数时DIFF_TERM我选择的是FLASE

FPGA输出给时钟驱动芯片的差分时钟就只能改为单端输出。差分输入就配置为LVDS_25.编译完成之后经过调试一直采不到正常的正弦信号(输入正弦信号作为测试信号)。

原因分析:

起初是怀疑输出时钟由差分改为单端后驱动能力有限。(500mHz的时钟手头的示波器也无法用示波器准确的测出来)

外接一个500Mhz的差分时钟,但还是采集不到正常的信号

后来公司前辈让我把DIFF_TERM 改为true试试,结果就好了。不合理但有效。

解决方案:

第二版硬件就将adc信号输入改到HR BANK了

1726

1726

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?