提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

前言

对DDR3的重新学习和知识梳理

借鉴:野火凌云系列书籍,B站小白FPGA

一、DDR3基础知识

1.基本概念

DDR3(Double-Date-Rate Three Synchronous Dynamic Random Access Memory )是第三代双倍速率同步动态随机存取内存。

1.双倍速率: DDR3 SDRAM 和SDRAM 最大的不同是DDR3是双边沿输入输出数据,上升沿和下降沿都输出数据。

2.同步: 与通常的异步DRAM不同,DDR3 SDRAM存在一个同步接口,其工作时钟的时钟频率与对应控制器(CPU/FPGA)的时钟频率相同,并且 SDRAM 内部的命。

令发送与数据传输均以此时钟为基准,实现指令或数据的同步操作。

3.动态:掉电无法保存,需要不断刷新。

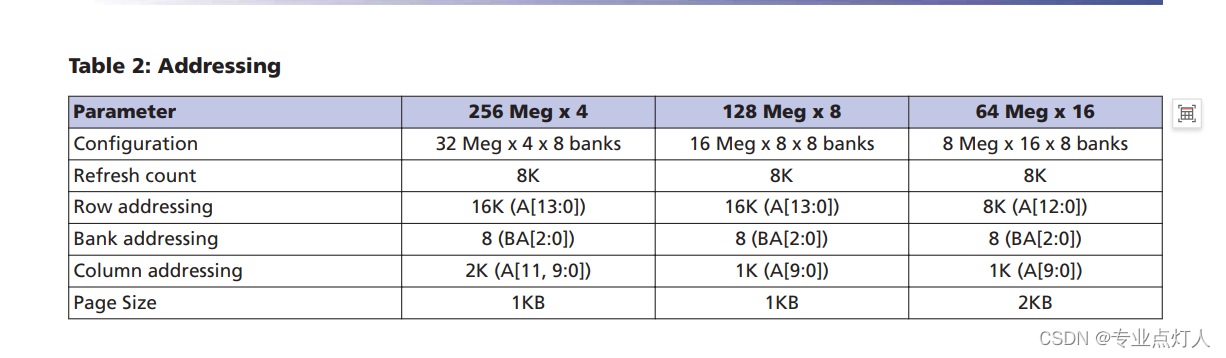

2.DDR3容量计算

bank数量* 行数量* 列数量*存储单元容量

例如 bank address位宽为3,Row address 位宽为14,Column adress 位宽为10,存储容量为16bit

则容量为2^3 * 2^14 * 2^10 * 16bit

第四列64Meg *16

Row addressing 8k=2^13/1024 同理

64Meg为8k * 8 * 1k

16为ddr3数据线位宽

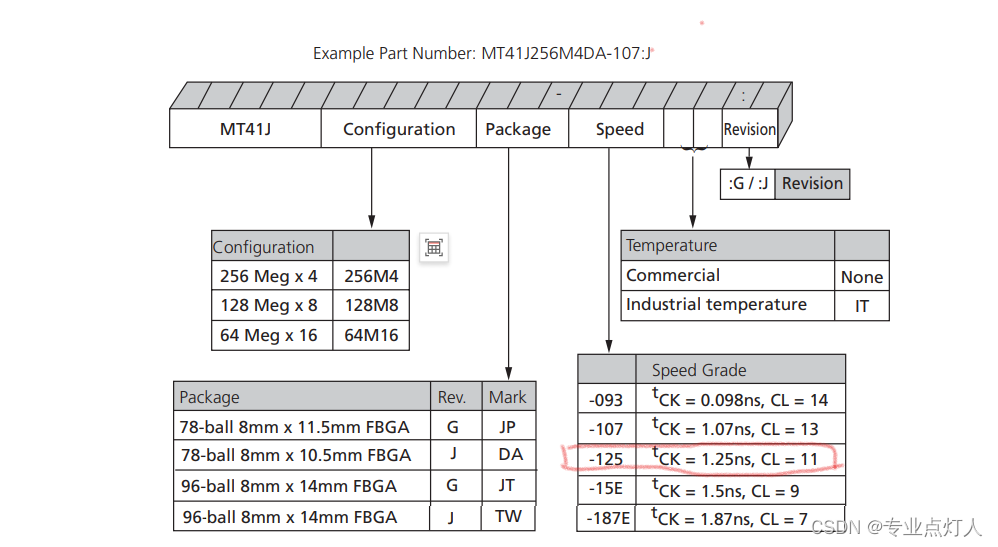

3.DDR3的命名信息

从DDR3的命名我们可以得出以下几点有用信息:

1.DDR3的传输数据端口位宽

2.DDR3支持的最大的时钟频率

3.DDR3传输的数据带宽

以MT41J128M16DA-125为例(选整数方便后面计算)

DDR3最大的工作时钟频率:列图中的-125 tck=1.25ns 1/1.25ns=800Mhz 即最大工作时钟频率大约为800Mhz

数据带宽:800M * 16bit * 2(双边沿触发)

二、时钟

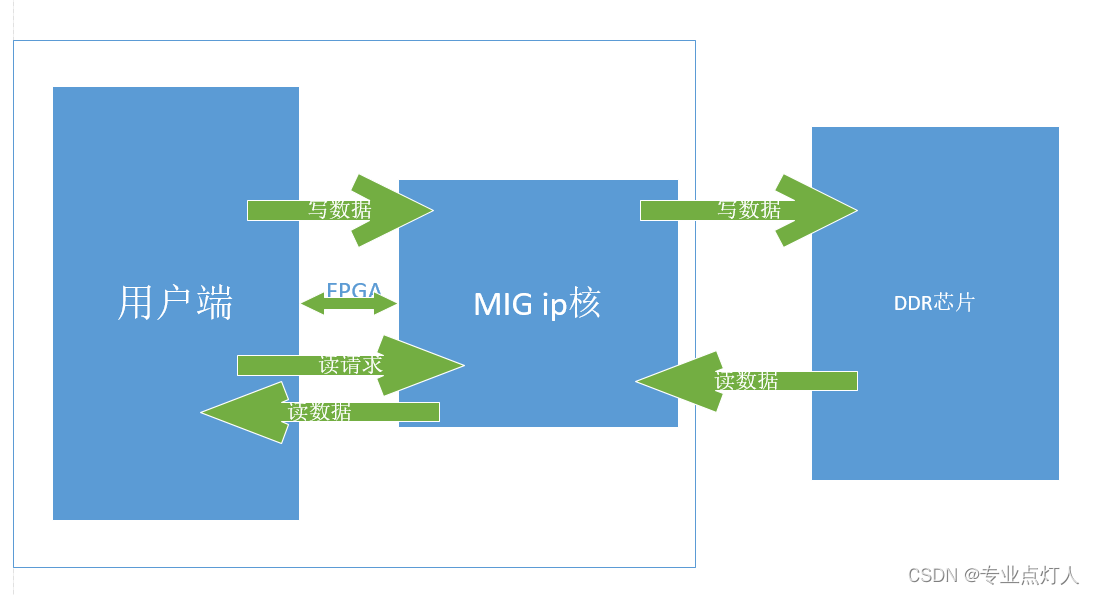

MIG ip核: 工作时钟sys_clk ,参考时钟ref_clk

ddr3芯片 : 差分工作时钟(由sys_clk通过pll输出的)

用户端: 用户时钟ui_clk(由sys_clk通过pll输出的)

DDR3芯片工作时钟与用户端时钟有一个比例关系:

DDR3芯片工作的频率:用户端时钟频率为4:1或者2:1当DDR3芯片工作的时钟为800M时候,比例只能为4:1。

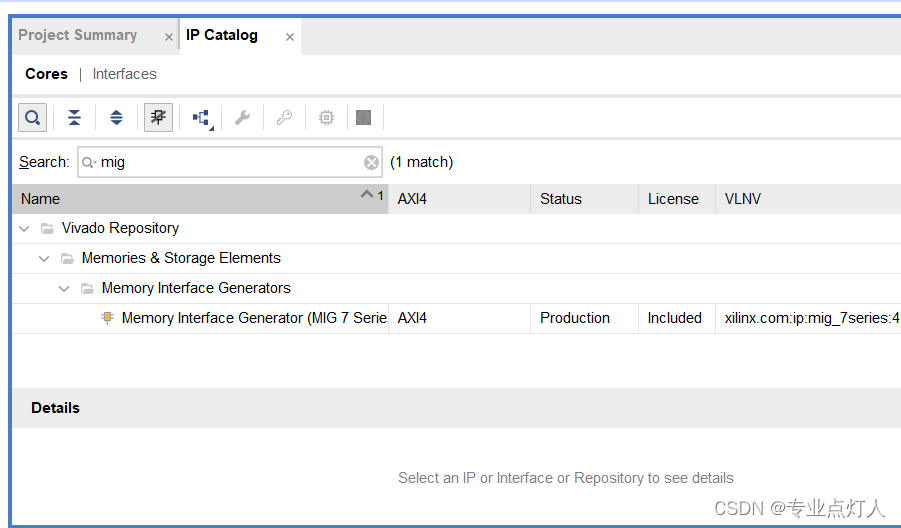

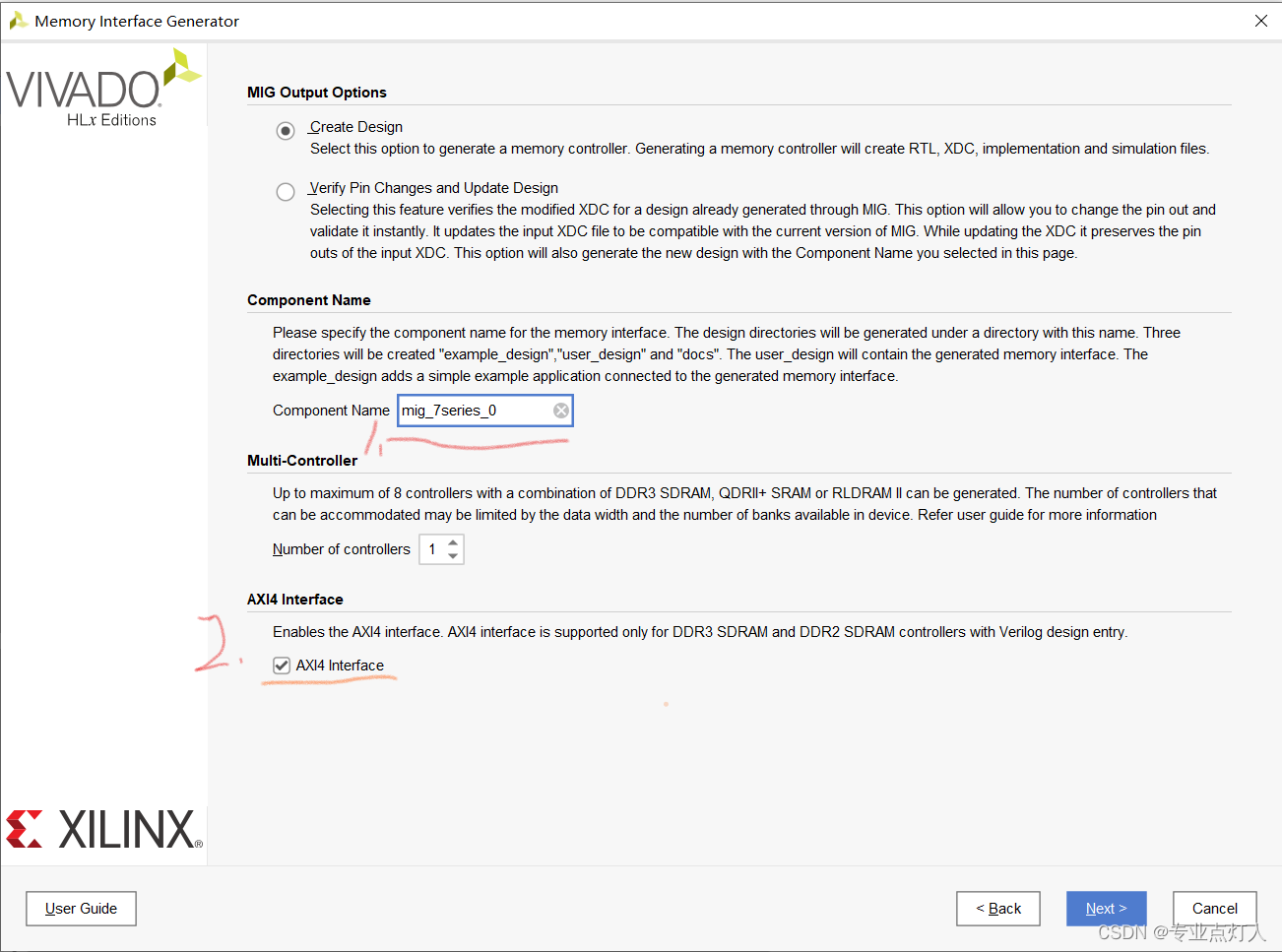

三 MIG核配置

next

1.为ddr3 ip核的名字,根据项目名称进行修改

2.选择AXI4 接口

next

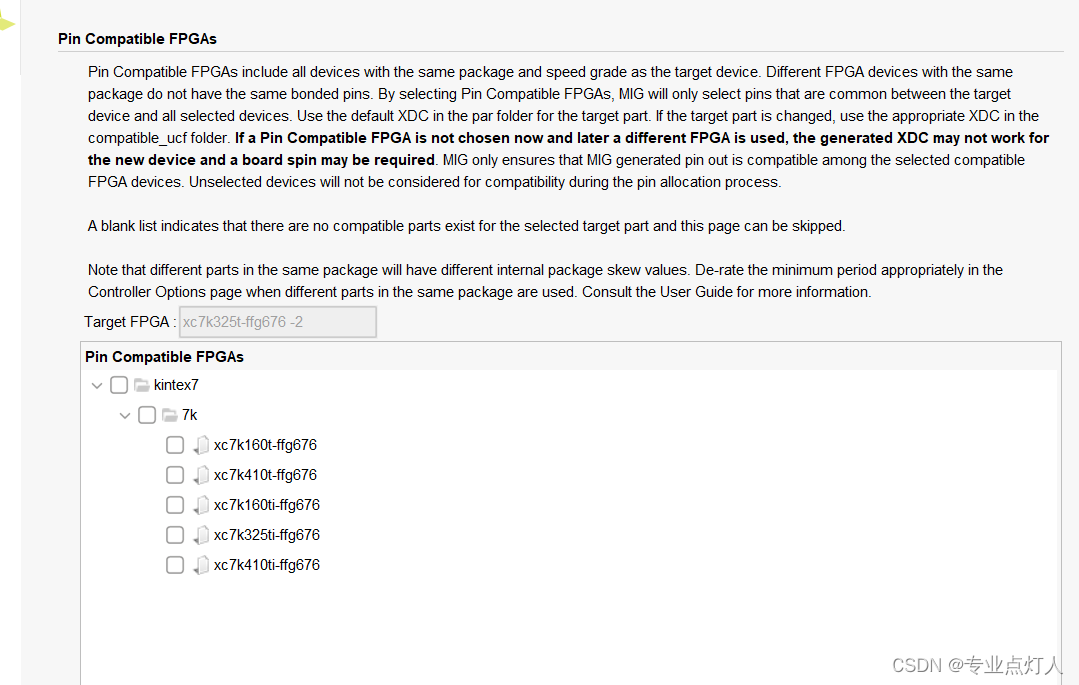

此页面选择兼容的芯片型号,可根据情况选择,此处我们不勾选。

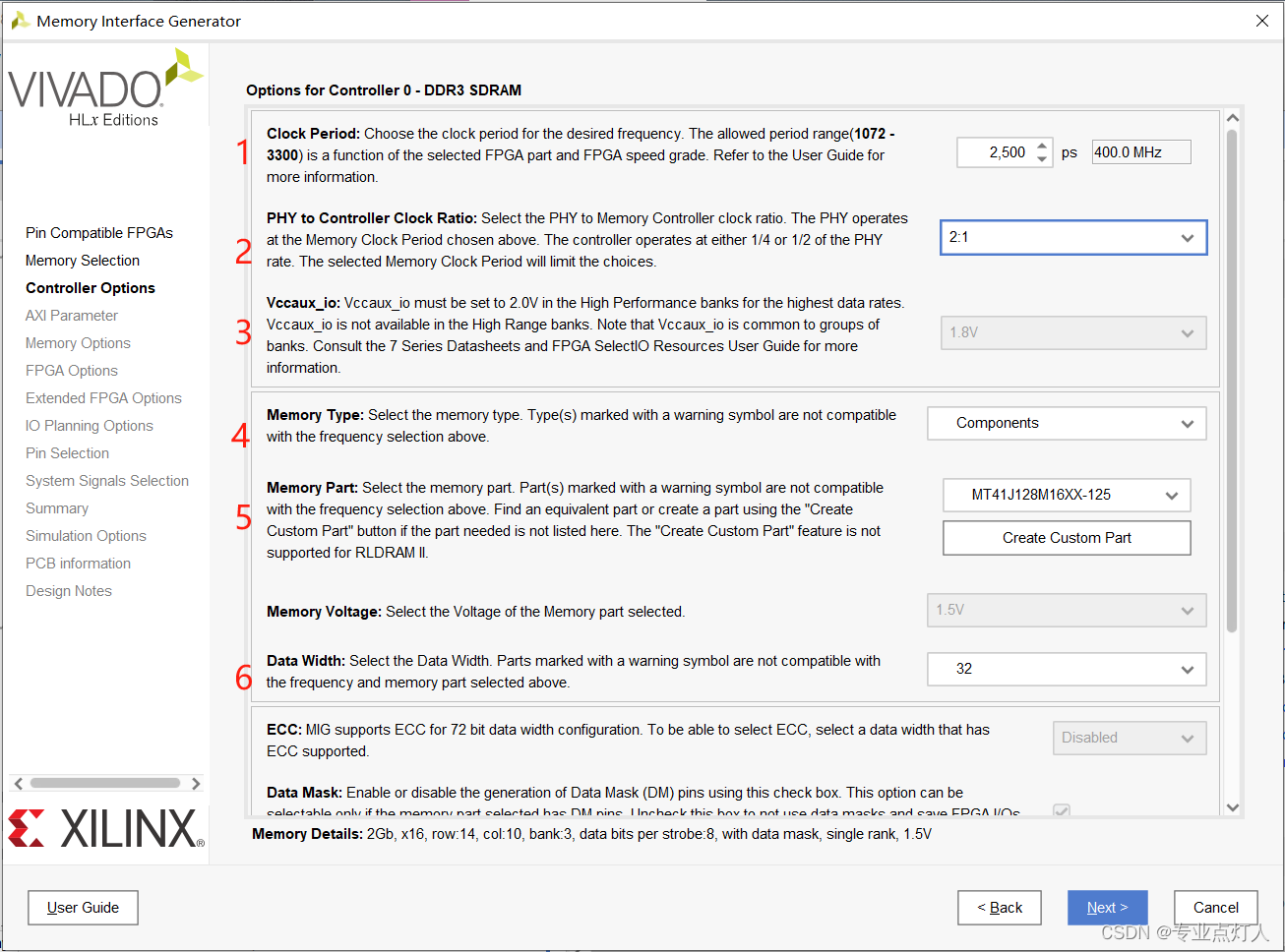

next

1.DDR3物理芯片的工作时钟,由MIG IP核通过PLL生产时钟输出,这个参数的范围和 FPGA 的芯片类型以及具体类型的速度等级有关,此处最高为800Mhz。

2.DDR3物理芯片工作时钟和用户端工作时钟之比,当选择400Mhz时,比例可以为4:1也可以为2:1。此处我们选择2:1,即用户时钟为200Mhz

3.DDR3工作电压默认无法修改

4.DDR3的类型一般默认即可

5.DDR3的型号 这里只有镁光公司的 其他的公司的芯片型号也是和镁光对标的,自行上网查询。

6.DDR3 的数据位宽(如图中芯片型号MT41J128M16xx-125,如果是板子是一个ddr3芯片则数据位宽为16,两个ddr3芯片数据位宽即为32),本硬件为两块ddr3芯片,所以选32。

其他的选项保持默认即可。

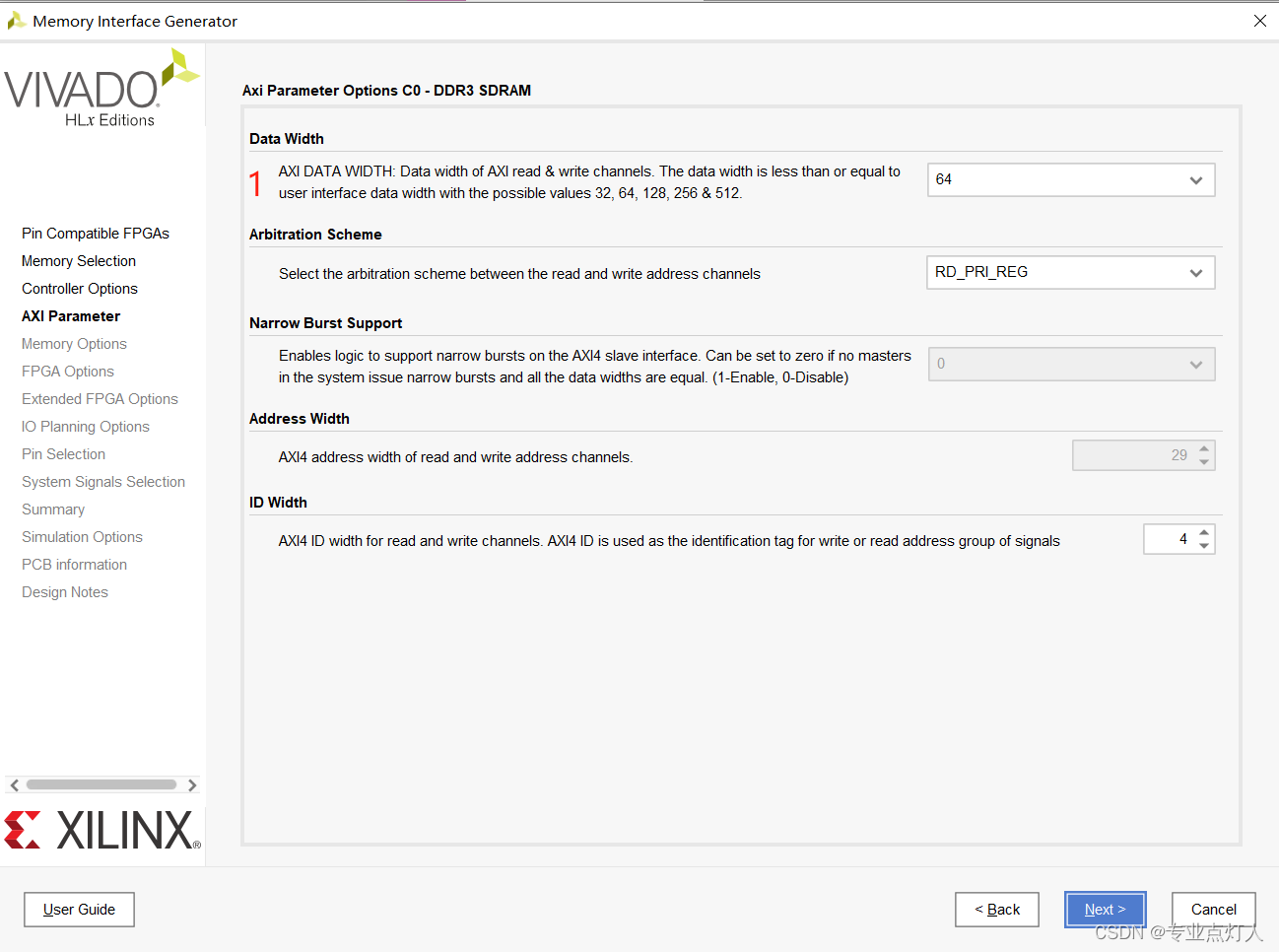

next

1.选择用户端口 AXI4 数据位宽,因为笔者封装 AXI 的代码采用了 64 位,因此

这里选择 64,如果位宽不一致,需要修改封装的代码。(即读写位宽,因为ddr3 存储器物理上不能同时写与读,而 axi4是可同时读与写的协议,因此我们为用户端口的读与写各自分配物理带宽的 1 半,该设计比较合理,如果用户端带宽大于物理端,会产生数据错误,本设计为读与写各自分配一半

带宽,那么读与写同时进行操作,总带宽也只是达到物理带宽,避免了数据错误。在进行

高速设计时,需要考虑到数据带宽)400322=200642带宽相等。

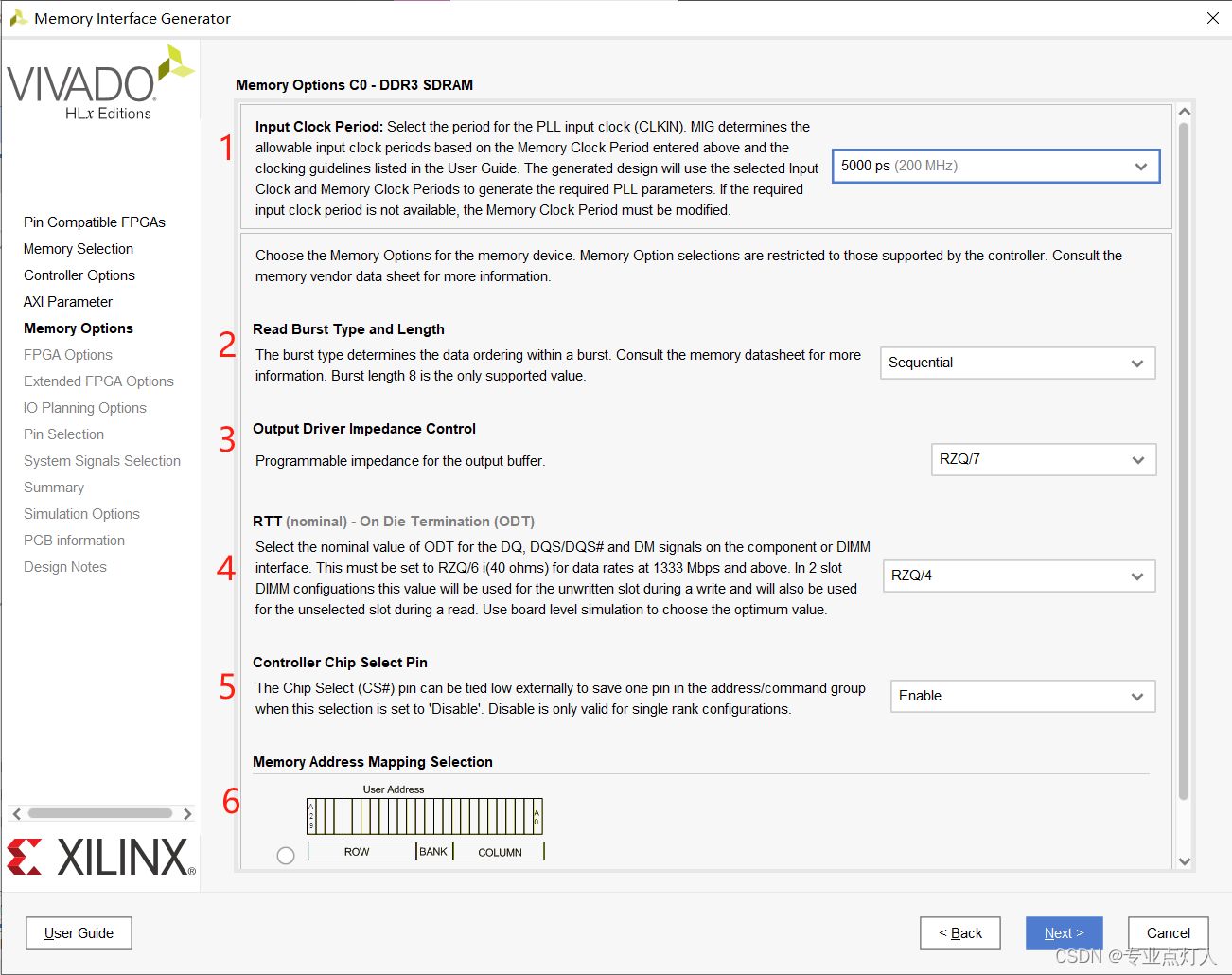

next

1.MIG IP核系统输入时钟,改时钟由FPGA程序内部产生(一般通过pll ip核产生)本次实验选择200MHz

2.突发类型选择,突发类型有顺序突发和交叉突发两种,本实验选择顺序突发(Sequential)

3.Output Driver Impdance Control:输出阻抗控制。本实验选择 RZQ/7。

4.RTT:终结电阻,可进行动态控制。本次实验选择 RZQ/4。

5.Controller Chip Select Pin:片选管脚引出使能。本实验选择 enable,表示把片选信号cs#引出来,由外部控制。

6.BANK_ROW_COLUMN:寻址方式选择。本实验选择第二种,即 BANK-ROWCOLUMN 的形式,这是一种最常规的 DDR3 寻址方式,即要指定某个地址,先指定bank,再指定行,最后指定列,这样就确定了一个具体地址。一般来说这样寻址方式有利于降低功耗,但是读写性能(效率)上不如“ROW_BANK_COLUMN”。

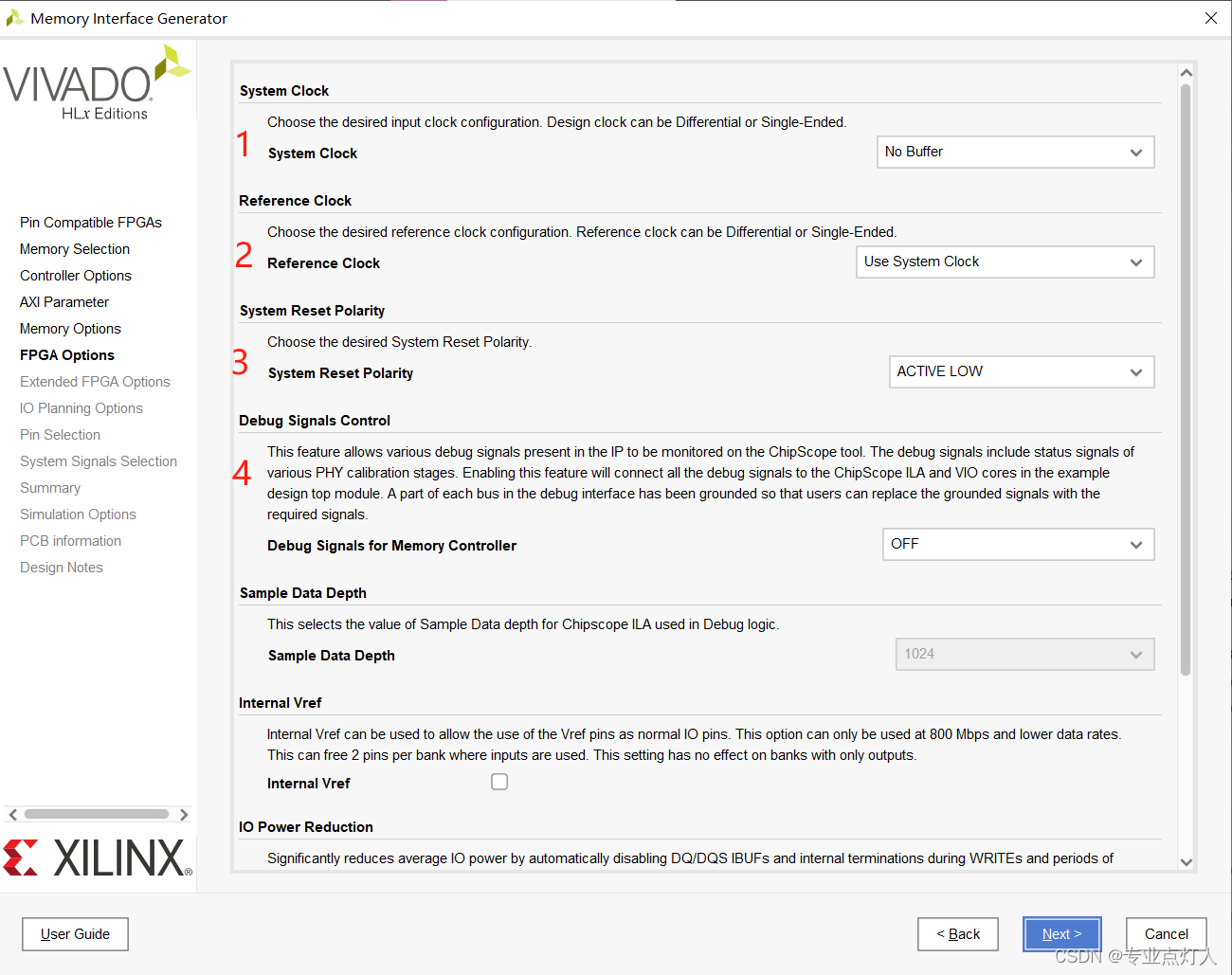

next

1.MIG IP核时钟输入类型 当输入时钟是通过晶振时钟经过pll生产时 选择no buffer (pll产生的时钟一般叫内部时钟)

当外部晶振输入的时钟直接给到MIG ip核 如果是差分的就选differential,如果是单端的就选single_Ended.

2.参考时钟类型:(一般默认为200Mhz) 当系统时钟为200Mhz时。选use system clock, 外部输入时选其他选项,和选MIG IP核时钟输入类型规则类似。

3.System Reset Polarity:复位有效电平选择。本实验选择“ACTIVE LOW”低电平有效。

4.Debug Signals Control:该选项用于控制 MIG IP 核是否把一些调试信号引出来,它会自动添加到ILA,这些信号包括一些 DDR3 芯片的校准状态信息。本实验选择选择“OFF”,不需要让 IP 核生产各种调试信号

no buffer 就是MIG IP核内部没有例化IBUF原语

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?