前言

采用分层次方法设计,先设计一个一位的全加器,然后在顶层调用4个1位的全加器。

一、verilog

1 仿真代码

代码如下:

module adder(a,b,ci,sum,co

);

input [3:0] a;

input[3:0]b;

input ci;

output[3:0] sum;

output[3:0] co;

wire[3:0] count;

add u0(a[0],b[0],ci,sum[0],count[0]);

add u1(a[1],b[1],count[0],sum[1],count[1]);

add u2(a[2],b[2],count[1],sum[2],count[2]);

add u3(a[3],b[3],count[2],sum[3],count[3]);

assign co = count[3];

endmodule

module add(input a ,input b, input ci,output sum,output count);

assign sum=(a^b)^ci;

assign count=(a&b)|(b&ci)|(a&ci);

endmodule

2.测试文件

代码如下:

module tb_adder(

);

reg [3:0] a,b;

reg ci;

wire [3:0] sum,co;

always #20 ci=~ci;

initial

begin

a=4'b0000;b = 4'b0000;ci=0;

repeat(16)

#20 a=a+1;

end

initial

begin

a=4'b0000;b = 4'b0000; ci=0;

repeat(16)

#20 b=b+1;

end

adder tb_adder(

.a(a),

.b(b),

.ci(ci),

.sum(sum),

.co(co)

);

endmodule

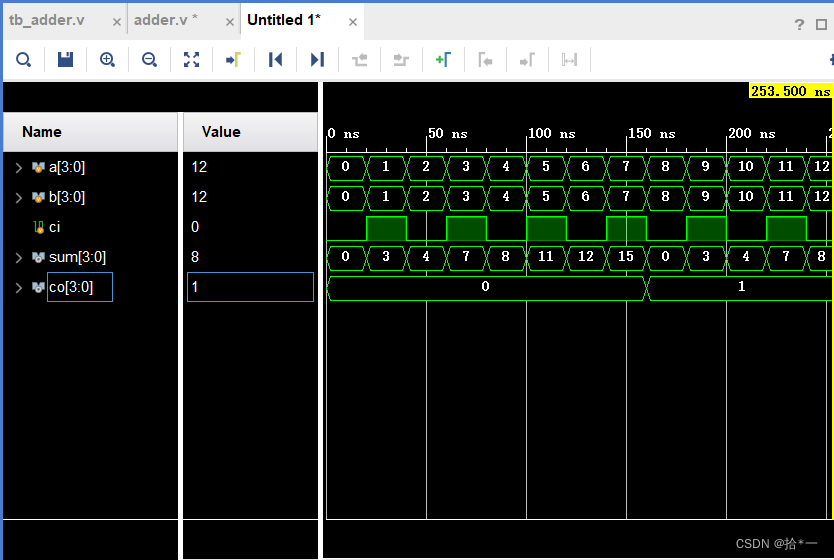

二仿真结果

本文仿真代码参考康华光的《电子技术基础》。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?