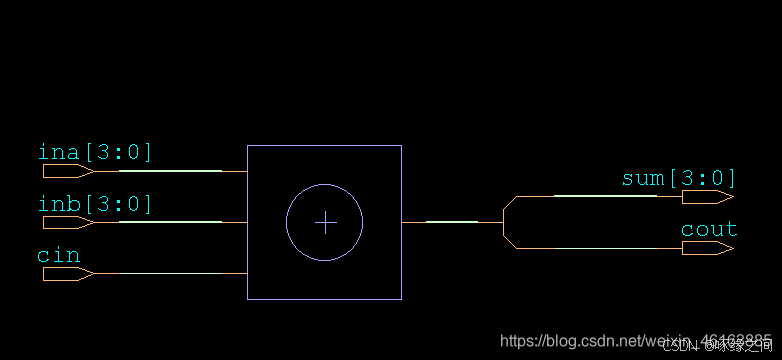

前言

1. 4位全加器代码

module ad4 (cout,sum,ina,inb,cin);

input [3:0] ina,inb;

input cin;

output [3:0] sum;

output cout;

assign {cout,sum} = ina + inb + cin;

endmodule

1.1 代码分析

这段代码是一个简单的 4位加法器 的 Verilog 实现。它使用了 Verilog 的 assign 语句来完成加法操作,并将结果分为两个部分:进位输出 (cout) 和 和输出 (sum)。

1.1.1模块定义

module ad4 (cout, sum, ina, inb, cin);

- ad4 是模块的名称。

- cout:输出信号,表示加法运算的最高位进位。

- sum:输出信号,表示加法运算的结果(4位)。

- ina:4位输入信号,表示加法运算的第一个操作数。

- inb:4位输入信号,表示加法运算的第二个操作数。

- cin:输入信号,表示加法运算的初始进位(通常用于链式加法器的低位进位输入)。

1.1.2 输入/输出声明

input [3:0] ina, inb; // 4-bit input signals

input cin; // 1-bit input carry

output [3:0] sum; // 4-bit output sum

output cout; // 1-bit output carry

- [3:0] 表示信号是 4 位宽的。

- ina 和 inb 是两个 4 位宽的输入信号。

- cin 是一个 1 位宽的输入信号,表示初始进位。

- sum 是一个 4 位宽的输出信号,表示加法结果的低 4 位。

- cout 是一个 1 位宽的输出信号,表示加法结果的最高位进位。

1.1.3 核心逻辑

assign {cout, sum} = ina + inb + cin;

- assign 是 Verilog 中的连续赋值语句,用于将表达式的结果赋值给指定的信号。

- {cout, sum} 是一个 5 位宽的信号拼接(concatenation),其中:

- cout 是最高位(第 5 位)。

- sum 是低 4 位。

- ina + inb + cin 表示将两个 4 位输入信号和一个 1 位进位信号相加,结果是一个 5 位宽的信号。

- 如果 ina 和 inb 的最大值是 1111(即 15),加上 cin 的最大值 1,结果最大为 1111 + 1111 + 1 = 11111(即 31)。

- 因此,加法结果需要 5 位来表示。

2. 验证环境

`timescale 1ns/1ps

module tb ()

reg [3:0] ina,inb;

reg cin;

wire [3:0] sum;

wire cout;

integer i,j;

always #5 cin = ~cin;

initial

begin

ina = 0;

inb = 0;

cin = 0;

for (i = 1; i<16;i=i+1)

#10 ina = i;

end

initial

begin

for (j=1;j<16;j=j+1)

#10 inb = j;

end

initial

begin

$monitor($time,,,"%d + %d +%b = {%b,%d}",ina,inb,cin,cout,sum);

#200;

$finish;

end

//print waneform

initial begin

$fsdbDumpfile ("ad4,fsdb);

$fsdbDumpvars(0,tb);

end

ad4 dut (

.ina (ina),

.inb (inb),

.sum (sum),

.cin (cin),

.cout (cout)

);

endmodule

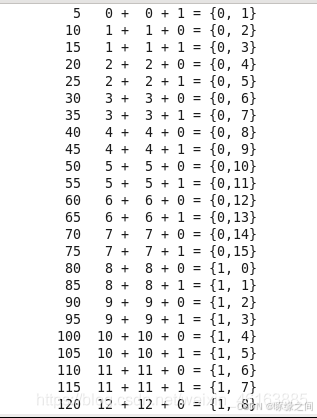

3. 验证结果

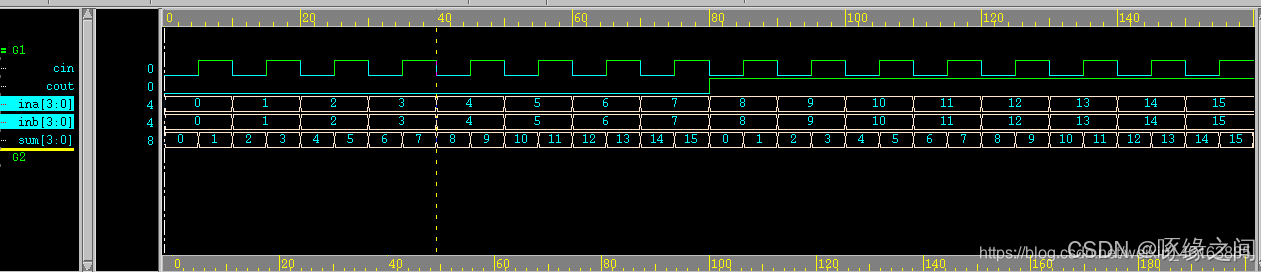

4. 验证波形

本文介绍了一个4位全加器的Verilog代码实现,通过使用输入和输出端口,展示了如何进行位级运算的加法操作,并通过测试模块验证了全加器的功能正确性。

本文介绍了一个4位全加器的Verilog代码实现,通过使用输入和输出端口,展示了如何进行位级运算的加法操作,并通过测试模块验证了全加器的功能正确性。

5307

5307

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?