文章目录

【 1. 简介 】

- STM32F4xx 系列一般都有 3 个 ADC,这些 ADC 可以独立使用,也可以使用双重/三重模式(提高采样率)。

- STM32F4 的 ADC 最大的转换速率为 2.4Mhz ,也就是转换时间为 0.41us(在 ADCCLK=36M,采样周期为 3 个 ADC 时钟下得到),不要让 ADC 的时钟超过 36M,否则将导致结果准确度下降 。

- 12位 逐次逼近型,可配置 12位、10位、8位、6位分辨率

- 输入范围:VREF- ≤ VIN ≤ VREF+

- A/D 转换可以单次、连续、扫描或间断模式执行。

- 规则通道 转换器件可产生 DMA请求

- 模拟看门狗特性可以 检测输入电压是否超过了用户自定义的阈值上下限

- 19 个通道,可测量 16 个外部源(复用通道)、 2 个内部源和 Vbat 通道的信号

- ADC结果储存在一个 左对齐/右对齐 的16位数据寄存器中

- STM32F407ZGT6 包含有 3 个 ADC。

【 2. 通道 】

- 有 19 个通道,可测量 16 个外部源、 2 个内部源和 Vbat 通道的信号 。

- 可以将转换分为两组:规则转换 和 注入转换, 规则通道相当于你正常运行的程序,而注入通道呢,就相当于中断 。在你程序正常执行的时候,中断是可以打断你的执行的。同这个类似,注入通道的转换可以打断规则通道的转换, 在注入通道被转换完成之后,规则通道才得以继续转换。

通过一个形象的例子可以说明: 假如你在家里的院子内放了 5 个温度探头,室内放了 3 个温度探头; 你需要时刻监视室外温度即可,但偶尔你想看看室内的温度;因此你可以使用规则通道组循环扫描室外的 5 个探头并显示 AD 转换结果,当你想看室内温度时,通过一个按钮启动注入转换组(3 个室内探头)并暂时显示室内温度,当你放开这个按钮后,系统又会回到规则通道组继续检测室外温度。从系统设计上,测量并显示室内温度的过程中断了测量并显示室外温度的过程,但程序设计上可以在初始化阶段分别设置好不同的转换组,系统运行中不必再变更循环转换的配置,从而达到两个任务互不干扰和快速切换的结果。可以设想一下,如果没有规则组和注入组的划分,当你按下按钮后,需要从新配置 AD 循环扫描的通道,然后在释放按钮后需再次配置 AD 循环扫描的通道。

- 每个组包含一个转换序列,该序列可按任意顺序在任意通道上完成 ,例如,可按以下顺序对序列进行转换: ADC_IN3、ADC_IN8、 ADC_IN2、 ADC_IN2、 ADC_IN0、 ADC_IN2、 ADC_IN2、 ADC_IN15。

- 一个规则转换组最多由 16 个转换构成 。必须在 ADC_SQRx 寄存器中选择转换序列的规则通道及其顺序,规则转换组中的转换总数必须写入 ADC_SQR1 寄存器中的 L[3:0] 位。

- 一个注入转换组最多由 4 个转换构成 。必须在 ADC_JSQR 寄存器中选择转换序列的注入通道及其顺序,注入转换组中的转换总数必须写入 ADC_JSQR 寄存器中的 L[1:0] 位。

- STM32F4 其 ADC 的规则通道组最多包含 16 个转换,而注入通道组最多包含 4 个通道。

- 如果在转换期间修改 ADC_SQRx 或 ADC_JSQR 寄存器,将复位当前转换并向 ADC 发送一个新的启动脉冲,以转换新选择的组。

- 温度传感器、 VREFINT 和 VBAT 内部通道

- 对于 STM32F40x 和 STM32F41x 器件,温度传感器内部连接到通道 ADC1_IN16。内部参考电压 VREFINT 连接到 ADC1_IN17。

- 对于 STM23F42x 和 STM32F43x 器件,温度传感器内部连接到与 VBAT 共用的通道ADC1_IN18,一次只能选择一个转换(温度传感器或 VBAT)。同时设置了温度传感器和 VBAT 转换时,将只进行 VBAT 转换。内部参考电压 VREFINT 连接到 ADC1_IN17。

- VBAT 通道连接到通道 ADC1_IN18,该通道也可转换为注入通道或规则通道。

- 注意: 温度传感器、VREFINT 和 VBAT 通道只在主 ADC1 外设上可用。

【 3. 单次转换模式 】

在单次转换模式下, ADC 执行一次转换

-

CONT 位为 0 时,可通过以下方式启动此模式

- 将 ADC_CR2 寄存器中的 SWSTART 位置 1(仅适用于规则通道)

- 将 JSWSTART 位置 1(适用于注入通道)

- 外部触发(适用于规则通道或注入通道)

-

完成所选通道的转换之后

- 如果转换了规则通道

- 转换数据存储在 16 位 ADC_DR 寄存器中

- EOC(转换结束)标志置 1

- EOCIE 位置 1 时将产生中断

- 如果转换了注入通道

- 转换数据存储在 16 位 ADC_JDR1 寄存器中

- JEOC(注入转换结束)标志置 1

- JEOCIE 位置 1 时将产生中断

-

然后, ADC 停止。

【 4. 连续转换模式 】

在连续转换模式下, ADC 结束一个转换后立即启动一个新的转换

- CONT 位为 1 时,可通过外部触发或将 ADC_CR2 寄存器中的 SWSTRT 位置 1 来启动此模式(仅适用于规则通道)。

- 每次转换之后:

- 如果转换了规则通道组

- 上次转换的数据存储在 16 位 ADC_DR 寄存器中

- EOC(转换结束)标志置 1

- EOCIE 位置 1 时将产生中断

- 注意: 无法连续转换注入通道。连续模式下唯一的例外情况是,注入通道配置为在规则通道之后自动转换(使用 JAUTO 位)。

【 5. 模拟看门狗 】

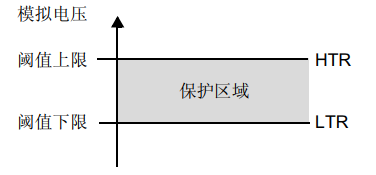

- 如果 ADC 转换的模拟电压低于阈值下限或高于阈值上限,则 AWD 模拟看门狗 状态位会置1 。

- 这些阈值在 ADC_HTR 和 ADC_LTR 16 位寄存器的 12 个最低有效位中进行 阈值设定 。

- 可以使用 ADC_CR1 寄存器中的 AWDIE 位 使能中断。

- 阈值与 ADC_CR2 寄存器中的 ALIGN 位的所选对齐方式无关,在对齐之前,会将模拟电压与阈值上限和下限进行比较。

- 表 49 介绍了应如何配置 ADC_CR1 寄存器才能在一个或多个通道上使能模拟看门狗。

【 6. 扫描模式 】

此模式用于 扫描一组模拟通道

- 通过将 ADC_CR1 寄存器中的 SCAN 位置 1 来选择扫描模式。将此位置 1 后, ADC 会扫描在 ADC_SQRx 寄存器(对于规则通道)或 ADC_JSQR 寄存器(对于注入通道)中选择的所有通道。为组中的每个通道都执行一次转换,每次转换结束后,会自动转换该组中的下一个通道。

- 如果将 CONT 位置 1,规则通道转换不会在组中最后一个所选通道处停止,而是再次从第一个所选通道继续转换 。

- 如果将 DMA 位置 1 ,则在每次规则通道转换之后,均使用直接存储器访问 (DMA) 控制器将转换自规则通道组的数据(存储在 ADC_DR 寄存器中)传输到 SRAM。

- 在以下情况下, ADC_SR 寄存器中的 EOC 位置 1:

- 如果 EOCS 位清零,在每个规则组序列转换结束时

- 如果 EOCS 位置 1,在每个规则通道转换结束时

从注入通道转换的数据始终存储在 ADC_JDRx 寄存器中。

【 7. 注入通道管理 】

触发注入

要使用触发注入,必须将 ADC_CR1 寄存器中的 JAUTO 位清零。

- 通过外部触发或将 ADC_CR2 寄存器中的 SWSTART 位置 1 来启动规则通道组转换。

- 如果在规则通道组转换期间出现外部注入触发或者 JSWSTART 位置 1,则当前的转换会复位,并且注入通道序列会切换为单次扫描模式。

- 然后,规则通道组的规则转换会从上次中断的规则转换处恢复。

- 如果在注入转换期间出现规则事件,注入转换不会中断,但在注入序列结束时会执行规则序列。

注意: 使用触发注入时,必须确保触发事件之间的间隔长于注入序列。例如,如果序列长度为 30 个ADC 时钟周期(即,采样时间为 3 个时钟周期的两次转换),则触发事件的最小间隔不能小于 31 个 ADC 时钟周期。

自动注入

如果将 JAUTO 位置 1,则注入组中的通道会在规则组通道之后自动转换。

- 这可用于转换最多由 20 个转换构成的序列,这些转换在 ADC_SQRx 和 ADC_JSQR 寄存器中编程。

- 在此模式下,必须禁止注入通道上的外部触发。

- 如果 CONT 位和 JAUTO 位均已置 1,则在转换规则通道之后会继续转换注入通道。

注意: 不能同时使用自动注入和不连续采样模式

【 8. 不连续采样模式 】

规则组

-

可将 ADC_CR1 寄存器中的 DISCEN 位置 1 来使能此模式。

-

该模式可用于转换含有 n (n≤8)个转换的短序列,该短序列是在 ADC_SQRx 寄存器中选择的转换序列的一部分,可通过写入 ADC_CR1 寄存器中的 DISCNUM[2:0] 位来指定 n 的值。

-

出现外部触发时,将启动在 ADC_SQRx 寄存器中选择的接下来 n 个转换,直到序列中的所有转换均完成为止。通过 ADC_SQR1 寄存器中的 L[3:0] 位定义总序列长度。

示例:

n = 3,要转换的通道 = 0、 1、 2、 3、 6、 7、 9、 10

第 1 次触发:转换序列 0、 1、 2

第 2 次触发:转换序列 3、 6、 7

第 3 次触发:转换序列 9、 10 并生成 EOC 事件

第 4 次触发:转换序列 0、 1、 2

注意: 在不连续采样模式下转换规则组时,不会出现翻转。 转换完所有子组后,下一个触发信号将启动第一个子组的转换 。在上述示例中,第 4 次触发重新转换了第 1 个子组中的通道 0、 1 和 2。

注入组

- 可将 ADC_CR1 寄存器中的 JDISCEN 位置 1 来使能此模式。

- 在出现外部触发事件之后,可使用该模式逐通道转换在 ADC_JSQR 寄存器中选择的序列。

- 出现外部触发时,将启动在 ADC_JSQR 寄存器中选择的下一个通道转换,直到序列中的所有转换均完成为止。通过 ADC_JSQR 寄存器中的 JL[1:0] 位定义总序列长度。

示例:

n = 1,要转换的通道 = 1、 2、 3

第 1 次触发:转换通道 1

第 2 次触发:转换通道 2

第 3 次触发:转换通道 3 并生成 EOC 和 JEOC 事件

第 4 次触发:通道 1

注意: 转换完所有注入通道后,下一个触发信号将启动第一个注入通道的转换 。在上述示例中,第 4 次触发重新转换了第 1 个注入通道。 不能同时使用自动注入和不连续采样模式。不得同时为规则组和注入组设置不连续采样模式,只能针对一个组使能不连续采样模式 。

【 9. 数据对齐 】

- ADC_CR2 寄存器中的 ALIGN 位用于选择转换后存储的数据的对齐方式,可选择左对齐和

右对齐两种方式。 - 注入通道组的转换数据将减去 ADC_JOFRx 寄存器中写入的用户自定义偏移量,因此结果可

以是一个负值。 SEXT 位表示扩展的符号值。 - 对于规则组中的通道,不会减去任何偏移量,因此只有十二个位有效。

- 特例:采用左对齐时,数据基于半字进行对齐,除了分辨率设置为 6 位时。分辨率设置为 6 位

时,数据基于字节进行对齐。

【 10. 可独立设置各通道采样时间 】

- ADC 会在数个 ADCCLK时钟周期(可设定)内对输入电压进行采样 ,可使用 ADC_SMPR1 和 ADC_SMPR2 寄存器中的 SMP[2:0] 位修改周期数。

- 每个通道均可以使用不同的采样时间进行采样。

总转换时间的计算公式如下:

总 转 换 时 间 T c o n v = 采 样 时 间 + 12 个 A D C C L K 周 期 总转换时间 T_{conv} = 采样时间 + 12 个ADCCLK周期 总转换时间Tconv=采样时间+12个ADCCLK周期

示例:

ADCCLK = 30 MHz 且采样时间 = 3 个周期时:

Tconv = 3 + 12 = 15 个周期 = 15* (1/30M) = 0.5 μs( APB2 为 60 MHz 时)

【 11. 外部触发转换和触发极性 】

- 可以通过外部事件(例如,定时器捕获、 EXTI 中断线)触发转换 。

- 可以实时更改外部触发的极性 。如果 EXTEN[1:0] 控制位(对于行规转换)或 JEXTEN[1:0] 位(对于注入转换)不等于 “0b00” ,则外部事件能够以所选极性触发转换。 表 50 提供了 EXTEN[1:0] 和 JEXTEN[1:0] 值与触发极性之间的对应关系。

- 外部触发事件选择:EXTSEL[3:0] 和 JEXTSEL[3:0] 控制位用于从 16 个可能事件中选择可触发规则组转换和注入组转换的事件。

- 可通过将 ADC_CR2 寄存器中的 SWSTART(对于规则转换)或 JSWSTART(对于注入转换)位置 1 来产生 软件源触发事件。

- 可通过注入触发中断规则组转换。

- 可以实时更改触发选择。不过,当更改触发选择时,会在 1 个 APB 时钟周期的时间范围内禁止触发检测,这是为了避免在转换期间出现意外检测。

【 12. 快速转换模式 】

- 可通过降低 ADC 分辨率来执行快速转换 。

- RES 位用于选择数据寄存器中可用的位数,每种分辨率的最小转换时间 如下:

12 位: 3 + 12 = 15 ADCCLK 周期

10 位: 3 + 10 = 13 ADCCLK 周期

8 位: 3 + 8 = 11 ADCCLK 周期

6 位: 3 + 6 = 9 ADCCLK 周期

【 13. 数据管理 】

使用 DMA

- 多通道转换时DMA起到的作用:由于规则通道组只有一个数据寄存器,因此,对于多个规则通道的转换,使用 DMA 非常有帮助,因为这样可以避免丢失在下一次写入之前还未被读出的 ADC_DR 寄存器中的数据。

- 在使能 DMA 模式的情况下( ADC_CR2 寄存器中的 DMA 位置 1) ,每完成规则通道组中的一个通道转换后,都会生成一个 DMA 请求 。这样便可将转换的数据从 ADC_DR 寄存器传输到用软件选择的目标位置。

- 溢出错误的影响和解决方法:如果数据丢失(溢出),则会将 ADC_SR 寄存器中的 OVR 位置 1 并生成一个中断(如果 OVRIE 使能位已置 1)。随后会禁止 DMA 传输并且不再接受 DMA 请求。在这种情况下,如果生成 DMA 请求,则会中止正在进行的规则转换并忽略之后的规则触发。随后需要 将所使用的 DMA 流中的 OVR 标志和 DMAEN 位清零,并重新初始化 DMA 和 ADC,以将需要的转换通道数据传输到正确的存储器单元。只有这样,才能恢复转换并再次使能数据传输。注入通道转换不会受到溢出错误的影响。

- 在 DMA 模式下,当 OVR = 1 时,传送完最后一个有效数据后会阻止 DMA 请求,这意味着传输到 RAM 的所有数据均被视为有效。

- 在最后一次 DMA 传输( DMA 控制器的 DMA_SxRTR 寄存器中配置的传输次数)结束时:

- 如果将 ADC_CR2 寄存器中的 DDS 位清零,则不会向 DMA 控制器发出新的 DMA 请求(这可避免产生溢出错误)。不过,硬件不会将 DMA 位清零,必须将该位写入 0 然后写入 1 才能启动新的传输。

- 如果将 DDS 位置 1,则可继续生成请求。从而允许在双缓冲区循环模式下配置 DMA。

- 在 使用 DMA 时将 ADC 从 OVR 状态中恢复,请按以下步骤操作

- 重新初始化 DMA(调整目标地址和 NDTR 计数器)

- 将 ADC_SR 寄存器中的 ADC OVR 位清零

- 触发 ADC 以开始转换。

在不使用DMA的情况下管理转换序列

- 如果转换过程足够慢,则可使用软件来处理转换序列。在这种情况下,必须将 ADC_CR2 寄存器中的 EOCS 位置 1,才能使 EOC 状态位在每次转换结束时置 1,而不仅是在序列结束时置 1。当 EOCS = 1 时,会自动使能溢出检测。因此,每当转换结束时, EOC 都会置 1,并且可以读取 ADC_DR 寄存器。

- 溢出管理与使用 DMA 时的管理相同。

- 要在 EOCS 位置 1 时将 ADC 从 OVR 状态中恢复,请按以下步骤操作:

- 将 ADC_SR 寄存器中的 ADC OVR 位清零

- 触发 ADC 以开始转换。

在不使用DMA和溢出检测的情况下进行转换

ADC 在转换一个或多个通道时不是每次都读取数据的情况下,这可能会很有用(例如,存在模拟看门狗时)。为此,必须禁止 DMA (DMA = 0) 并且仅在序列结束 (EOCS = 0) 时才将EOC 位置 1。在此配置中,溢出检测已禁止。

【 14. 多重ADC模式 】

- 在具有两个或更多 ADC 的器件中,可使用双重(具有两个 ADC)和三重(具有三个 ADC)ADC 模式

- 尽管 ADC2 和 ADC3 上存在外部触发,但它们并未显示在此图中。

- 在双重 ADC 模式下,不存在 ADC3 从器件部分。ADC 通用数据寄存器 (ADC_CDR) 包含 ADC1 和 ADC2 的规则转换数据。使用全部32 个寄存器位。

- 在三重 ADC 模式下, ADC 通用数据寄存器 (ADC_CDR) 包含 ADC1、 ADC2 和 ADC3 的规则转换数据。按照所选的存储顺序使用全部 32 个寄存器位。

- 在多重 ADC 模式下,通过 ADC1 主器件到 ADC2 和 ADC3 从器件的交替触发或同时触发来启动转换,具体取决于 ADC_CCR 寄存器中的 MULTI[4:0] 位所选的模式。

- 在多重 ADC 模式下,配置外部事件触发转换时,应用必须设置为仅主器件触发而禁止从器件触发 ,以防止出现意外触发而启动不需要的从转换。

- 可实现以下的多重ADC模式:

- 注入同时模式

- 规则同时模式

- 交替模式

- 交替触发模式

- 注入同时模式 + 规则同时模式

- 规则同时模式 + 交替触发模式

- 在多重 ADC 模式下,可在多模式数据寄存器 (ADC_CDR) 中读取转换的数据。可在多模式状态寄存器 (ADC_CSR) 中读取状态位

多重 ADC 下的 DMA 模式

在多重 ADC 模式下,可将 DMA 配置为使用三种不同的模式来传输转换的数据。在所有情况下,要使用的 DMA 流均连接到 ADC:

-

DMA 模式 1: 每发出一个 DMA 请求(一个数据项可用),就会传输一个表示 ADC 转换的数据项的半字 。

- DMA 模式 1 用于 三重规则同时模式 。

- 在双重 ADC 模式下,发出第一个请求时传输 ADC1 的数据,发出第二个请求时传输 ADC2 的数据,依次类推。

- 在三重 ADC 模式下,发出第一个请求时传输 ADC1 的数据,发出第二个请求时传输ADC2 的数据,发出第三个请求时传输 ADC3 的数据;重复此序列。因此 DMA 首先传输 ADC1 的数据,随后传输 ADC2 的数据,再传输 ADC3 的数据,依次类推。

-

示例:

三重规则同时模式:生成 3 个连续的 DMA 请求(每个请求对应一个转换数据项)

第 1 个请求: ADC_CDR[31:0] = ADC1_DR[15:0]

第 2 个请求: ADC_CDR[31:0] = ADC2_DR[15:0]

第 3 个请求: ADC_CDR[31:0] = ADC3_DR[15:0]

第 4 个请求: ADC_CDR[31:0] = ADC1_DR[15:0]

-

DMA 模式 2: 每发送一个 DMA 请求(两个数据项可用),就会以字的形式传输表示两个 ADC 转换数据项的两个半字(半字就是16位) 。

- DMA 模式 2 用于 交替模式和规则同时模式(仅适用于双重 ADC 模式) 。

- 在双重 ADC 模式下,发出第一个请求时会传输 ADC2 和 ADC1 的数据( ADC2 数据占用高位半字, ADC1 数据占用低位半字),依此类推。

- 在三重 ADC 模式下,将生成三个 DMA 请求:发出第一个请求时,会传输 ADC2和 ADC1 的数据( ADC2 数据占用高位半字, ADC1 数据占用低位半字)。发出第二个请求时,会传输 ADC1 和 ADC3 的数据( ADC1 数据占用高位半字, ADC3数据占用低位半字)。发出第三个请求时,会传输 ADC3 和 ADC2 的数据( ADC3 数据占用高位半字, ADC2 数据占用低位半字),依此类推。

示例:

a) 双重交替模式:每当有 2 个数据项可用时,就会生成一个 DMA 请求:

第 1 个请求: ADC_CDR[31:0] = ADC2_DR[15:0] | ADC1_DR[15:0]

第 2 个请求: ADC_CDR[31:0] = ADC2_DR[15:0] | ADC1_DR[15:0]

b) 三重交替模式:每当有 2 个数据项可用时,就会生成一个 DMA 请求

第 1 个请求: ADC_CDR[31:0] = ADC2_DR[15:0] | ADC1_DR[15:0]

第 2 个请求: ADC_CDR[31:0] = ADC1_DR[15:0] | ADC3_DR[15:0]

第 3 个请求: ADC_CDR[31:0] = ADC3_DR[15:0] | ADC2_DR[15:0]

第 4 个请求: ADC_CDR[31:0] = ADC2_DR[15:0] | ADC1_DR[15:0] -

DMA 模式 3: 此模式与 DMA 模式 2 相似,唯一的区别是:在这种模式下, 每发送一个 DMA 请求(两个数据项可用),就会以半字的形式传输表示两个 ADC 转换数据项的两个字节 ,此模式下的数据传输顺序与 DMA 模式 2 相似。

- DMA 模式 3 用于 分辨率为 6 位和 8 位时的交替模式 。

-

示例:

a) 双重交替模式:每当有 2 个数据项可用时,就会生成一个 DMA 请求

第 1 个请求: ADC_CDR[15:0] = ADC2_DR[7:0] | ADC1_DR[7:0]

第 2 个请求: ADC_CDR[15:0] = ADC2_DR[7:0] | ADC1_DR[7:0]

b) 三重交替模式:每当有 2 个数据项可用时,就会生成一个 DMA 请求

第 1 个请求: ADC_CDR[15:0] = ADC2_DR[7:0] | ADC1_DR7:0]

第 2 个请求: ADC_CDR[15:0] = ADC1_DR[7:0] | ADC3_DR[15:0]

第 3 个请求: ADC_CDR[15:0] = ADC3_DR[7:0] | ADC2_DR[7:0]

第 4 个请求: ADC_CDR[15:0] = ADC2_DR[7:0] | ADC1_DR7:0]

-

溢出检测:

- 如果在其中一个相关的 ADC(双重和三重模式下的 ADC1 和 ADC2,仅有三重模式时的 ADC3)上检测到溢出,则不再发出 DMA 请求,以确保传输到 RAM 的所有数据都有效。

- 对于与某个 ADC 对应的 EOC 位,有时可能会因为此 ADC 的数据寄存器包含有效数据而保持置 1 。

注入同时模式

规则同时模式

交替模式

此模式只能用于规则组(通常为一个通道)。外部触发源来自 ADC1 的规则通道多路复用器。

双重 ADC 模式

-

出现外部触发之后:

- ADC1 立即启动

- 经过几个 ADC 时钟周期延迟后 ADC2 启动

-

交替模式下 2 个转换之间的最小延迟通过 ADC_CCR 寄存器中的 DELAY 位进行配置。但是,如果某个 ADC 的互补 ADC 仍在对其输入进行采样,则该 ADC 无法启动转换(在给定时间内,只有一个 ADC 能够对输入信号采样)。在这种情况下:

延 迟 时 间 = 采 样 时 间 + 2 个 A D C 时 钟 周 期 延迟时间=采样时间 + 2 个ADC 时钟周期 延迟时间=采样时间+2个ADC时钟周期例如:如果两个 ADC 的 DELAY = 5 个时钟周期,且采样时间为 15 个时钟周期,则 ADC1 和 ADC2 之间的转换延迟为 17 个时钟周期。

-

如果 ADC1 和 ADC2 上的 CONT 位均置 1,则这两个 ADC 所选规则通道会连续进行转换。

-

如果转换序列中断(例如 DMA 传输结束时),则必须首先通过在独立模式下进行配置来将多重 ADC 定序器复位(位 DUAL[4:0] = 00000),然后才可以对交替模式进行编程。

-

ADC2 生成一个 EOC 中断之后(如果已通过 EOCIE 位使能),会生成一个 32 位 DMA 传输请求(如果 ADC_CCR 寄存器中的 DMA[1:0] 位等于 0b10)。此请求首先会将存储在ADC_CDR 32 位寄存器高位半字中的 ADC2 转换数据传输到 SRAM,然后将存储在寄存器低位半字中的 ADC1 转换数据传输到 SRAM。

三重 ADC 模式

-

出现外部触发之后:

- ADC1 立即启动

- 经过几个 ADC 时钟周期延迟后 ADC2 启动

- 在 ADC2 转换经过几个 ADC 时钟周期的延迟后 ADC3 启动

-

交替模式下 2 个转换之间的最小延迟通过 ADC_CCR 寄存器中的 DELAY 位进行配置。但是,如果某个 ADC 的互补 ADC 仍在对其输入进行采样,则该 ADC 无法启动转换( 在给定时间内,只有一个 ADC 能够对输入信号采样 )。在这种情况下:

延 迟 时 间 = 采 样 时 间 + 2 个 A D C 时 钟 周 期 延迟时间=采样时间 + 2 个ADC 时钟周期 延迟时间=采样时间+2个ADC时钟周期例如:如果这三个 ADC 的 DELAY = 5 个时钟周期,且采样时间为 15 个时钟周期,则 ADC1、 ADC2 和 ADC3 之间的转换延迟为 17 个时钟周期。

-

如果 ADC1、 ADC2 和 ADC3 上的 CONT 位均置 1,则这些 ADC 所选规则通道会连续进行转换。

-

如果转换序列中断(例如 DMA 传输结束时),则必须首先通过在独立模式下进行配置来将多重 ADC 定序器复位(位 DUAL[4:0] = 00000),然后才可以对交替模式进行编程。

-

在此模式下,每当出现 2 个可用数据项时,就会生成一个 DMA 传输请求(如果 ADC_CCR 寄存器中的 DMA[1:0] 位等于 0b10)。此请求首先会将存储在 ADC_CDR 32 位寄存器低位半字中的第一批转换数据传输到 SRAM,然后将存储在 ADC_CDR 高位半字中的第二批转换数据传输到 SRAM。具体顺序如下:

- 第 1 个请求: ADC_CDR[31:0] = ADC2_DR[15:0] | ADC1_DR[15:0]

- 第 2 个请求: ADC_CDR[31:0] = ADC1_DR[15:0] | ADC3_DR[15:0]

- 第 3 个请求: ADC_CDR[31:0] = ADC3_DR[15:0] | ADC2_DR[15:0]

- 第 4 个请求: ADC_CDR[31:0] = ADC2_DR[15:0] | ADC1_DR[15:0], …

交替触发模式

混合型规则/注入同时模式

规则同时+交替触发组合模式

【 15. 温度传感器 】

-----不常用,待定更新-----

【 16. 电池充电监测 】

-----不常用,待定更新-----

【 17. ADC 中断 】

- 当模拟看门狗状态位和溢出状态位分别置 1 时,规则组和注入组在转换结束时可能会产生中断。可以使用单独的中断使能位以实现灵活性。

- ADC_SR 寄存器中存在另外两个标志,但这两个标志不存在中断相关性:

- JSTRT(开始转换注入组的通道)

- STRT(开始转换规则组的通道)

【 18. 寄存器 】

状态寄存器 ADC_SR

- 位 31:6 保留,必须保持复位值

- 位 5 OVR: 溢出 (Overrun)

数据丢失时,硬件将该位置 1(在单一模式或双重/三重模式下)。但需要通过软件清零。溢出检测仅在 DMA = 1 或 EOCS = 1 时使能。

0:未发生溢出

1:发生溢出- 位 4 STRT: 规则通道开始标志 (Regular channel start flag)

规则通道转换开始时,硬件将该位置 1。但需要通过软件清零。

0:未开始规则通道转换

1:已开始规则通道转换- 位 3 JSTRT: 注入通道开始标志 (Injected channel start flag)

注入组转换开始时,硬件将该位置 1。但需要通过软件清零。

0:未开始注入组转换

1:已开始注入组转换- 位 2 JEOC: 注入通道转换结束 (Injected channel end of conversion)

组内所有注入通道转换结束时,硬件将该位置 1。但需要通过软件清零。

0:转换未完成

1:转换已完成- 位 1 EOC: 规则通道转换结束 (Regular channel end of conversion)

规则组通道转换结束后,硬件将该位置 1。通过软件或通过读取 ADC_DR 寄存器将该位清零。

0:转换未完成 (EOCS=0) 或转换序列未完成 (EOCS=1)

1:转换已完成 (EOCS=0) 或转换序列已完成 (EOCS=1)- 位 0 AWD: 模拟看门狗标志 (Analog watchdog flag)

当转换电压超过在 ADC_LTR 和 ADC_HTR 寄存器中编程的值时,硬件将该位置 1。但需要通过软件清零。

0:未发生模拟看门狗事件

1:发生模拟看门狗事件

控制寄存器 ADC_CR1、ADC_CR2

- 位31:27保留,必须保持复位值

- 位26 OVRIE:溢出中断使能(Overrun interrupt enable)

通过软件将该位置1和清零可使能/禁止溢出中断。

0:禁止溢出中断

1:使能溢出中断。OVR位置1时产生中断。- 位25:24 RES[1:0]:分辨率(Resolution)

通过软件写入这些位可选择转换的分辨率。

00:12位( 15 ADCCLK周期>

01: 10位( 13 ADCCLK周期>

10:8位( 11 ADCCLK周期>

11:6位(9 ADCCLK周期)- 位23 AWDEN:规则通道上的模拟看门狗使能(Analog watchdog enable on regular channels)

此位由软件置1和清零。

0:在规则通道上禁止模拟看门狗

1:在规则通道上使能模拟看门狗- 位22JAWDEN:注入通道上的模拟看门狗使能(Analog watchdog enable on injected channels)

此位由软件置1和清零。

0:在注入通道上禁止模拟看门狗

1:在注入通道上使能模拟看门狗- 位.21:16 保留,必须保持复位值

- 位15:13 DISCNUM[2:0]:不连续采样模式通道计数(Discontinuous mode channel count)

软件将写入这些位,用于定义在接收到外部触发后于不连续采样模式下转换的规则通道数。

000:1个通道

001:2个通道

…

111:8个通道- 位12 JDISCEN:注入通道的不连续采样模式(Discontinuous mode on injected channels)

通过软件将该位置1和清零可使能/禁止注入通道的不连续采样模式。

0:禁止注入通道的不连续采样模式

1:使能注入通道的不连续采样模式- 位11 DISCEN:规则通道的不连续采样模式(Discontinuous mode on regular channels)

通过软件将该位置1和清零可使能/禁止规则通道的不连续采样模式。

0:禁止规则通道的不连续采样模式

1:使能规则通道的不连续采样模式- 位10 JAUTO:注入组自动转换(Automatic injected group conversion)

通过软件将该位置1和清零可在规则组转换后分别使能/禁止注入组自动转换。

0:禁止注入组自动转换

1:使能注入组自动转换- 位9 AWDSGL:在扫描模式下使能单一通道上的看门狗(Enable the watchdog on a single channel in scan mode)

通过软件将该位置1和清零可分别使能/禁止通过AWDCH[4:0]位确定的通道上的模拟看门狗。

0:在所有通道上使能模拟看门狗

1:在单一通道上使能模拟看门狗- 位8 SCAN:扫描模式(Scan mode)

通过软件将该位置1和清零可使能/禁止扫描模式。在扫描模式下,转换通过ADC_SQRx或ADC_JSQRx寄存器选择的输入。

0:禁止扫描模式

1:使能扫描模式

注意: EOCIE位置1时将生成EOC中断:如果EOCS位清零,在每个规则组序列转换结束时;如果EOCS位置1,在每个规则通道转换结束时。

注意:JEOCIE位置1时,JEOC中断仅在最后一个通道转换结束时生成。- 位7 JEOCIE:注入通道的中断使能(Interrupt enable for injected channels)

通过软件将该位置1和清零可使能/禁止注入通道的转换结束中断。

0:禁止JEOC中断

1:使能JEoC中断。

JEOC位置1时产生中断。- 位6 AWDIE:模拟看门狗中断使能(Analog watchdog interrupt enable)

通过软件将该位置1和清零可使能/禁止模拟看门狗中断。

0:禁止模拟看门狗中断

1:使能模拟看门狗中断- 位5 EOCIE:EOC中断使能(Interrupt enable for EOC)

通过软件将该位置1和清零可使能/禁止转换结束中断。

0:禁止EOC中断

1:使能EOC中断

EOC位置1时产生中断。- 位4:0 AWDCH[4:0]:模拟看门狗通道选择位(Analog watchdog channel select bits)

这些位将由软件置1和清零。它们用于选择由模拟看门狗监控的输入通道。

00000:ADC模拟输入通道0

00001:ADC模拟输入通道1

…

01111:ADC模拟输入通道15

10000:ADC模拟输入通道16

10001:ADC模拟输入通道17

10010:ADC模拟输入通道18

保留其它值

- 位31保留,必须保持复位值

- 位30 SWSTART:开始转换规则通道(Start conversion of regular channels)

通过软件将该位置1可开始转换,而硬件会在转换开始后将该位清零。我们每次转换(单次转换模式下)都需要向该位写1。

0:复位状态

1:开始转换规则通道

注意:该位只能在ADON= 1时置1,否则不会启动转换。- 位29:28 EXTEN:规则通道的外部触发使能(External trigger enable for regular channels)

通过软件将这些位置1和清零可选择外部触发极性和使能规则组的触发。

00:禁止触发检测

01:上升沿上的触发检测

10:下降沿上的触发检测

11:上升沿和下降沿上的触发检测- 位.27:24 EXTSEL[3:0]:为规则组选择外部事件(External event select for regular group)

这些位可选择用于触发规则组转换的外部事件。

0000:定时器1 CC1事件

0001:定时器1 CC2事件

0010:定时器1 CC3事件

0011:定时器2 CC2事件

0100:定时器2 CC3事件

0101:定时器2 CC4事件

0110:定时器2 TRGO事件

0111:定时器3 CC1事件

1000:定时器3 TRGO事件

1001:定时器4 CC4事件

1010:定时器5 CC1事件

1011:定时器5 cC2事件

1111:EXTI线11- 位23 保留,必须保持复位值

- 位22JswSTART:开始转换注入通道(Start conversion of injected channels)

转换开始后,软件将该位置1,而硬件将该位清零。

0:复位状态

1:开始转换注入通道

注意:该位只能在ADON= 1时置1,否则不会启动转换。- 位21:20 JEXTEN:注入通道的外部触发使能(External trigger enable for injected channels)

通过软件将这些位置1和清零可选择外部触发极性和使能注入组的触发。

00:禁止触发检测

01:上升沿上的触发检测

10:下降沿上的触发检测

11:上升沿和下降沿上的触发检测- 位19:16 JEXTSEL[3:0]:为注入组选择外部事件(External event select for injected group)

这些位可选择用于触发注入组转换的外部事件。

0000:定时器1 CC4事件

0001:定时器1 TRGO事件

0010:定时器2 CC1事件

0011:定时器2 TRGO事件

0100:定时器3 CC2事件

0101:定时器3 CC4事件

0110:定时器4 CC1事件

0111:定时器4 CC2事件

1000:定时器4 CC3事件

1001:定时器4 TRGO事件

1010:定时器5 CC4事件

1011:定时器5 TRGO事件

1100:定时器8 CC2事件

1101:定时器8 CC3事件

1110:定时器8 CC4事件

1111:EXTI线15- 位15:12保留,必须保持复位值。

- 位11 ALIGN:数据对齐(Data alignment)

此位由软件置1和清零。请参见图38和图 39。

0:右对齐

1:左对齐- 位10 EOCS:结束转换选择(End of conversion selection)

此位由软件置1和清零。

0:在每个规则转换序列结束时将EOC位置1。溢出检测仅在DMA=1时使能。

1:在每个规则转换结束时将EOC位置1。使能溢出检测。- 位9 DDS:DMA 禁止选择(对于单一ADC模式)(DMA disable selection (for single ADC mode))

此位由软件置1和清零。

0:最后一次传输后不发出新的 DMA请求(在DMA 控制器中进行配置)

1:只要发生数据转换且DMA = 1,便会发出DAM请求- 位8 DMA:直接存储器访问模式(对于单一ADC模式)(Direct memory access mode (for single ADC mode))

此位由软件置1和清零。有关详细信息,请参见DMA控制器一章。

0:禁止DMA模式

1:使能DMA模式- 位7:2保留,必须保持复位值。

- 位1CONT:连续转换(Continuous conversion)

此位由软件置1和清零。该位置1时,转换将持续进行,直到该位清零。

0:单次转换模式

1:连续转换模式- 位0 ADON:A/D转换器开启/关闭(A/D Converter ON /OFF)

此位由软件置1和清零。

可通过将 ADON 位置 1 来为 ADC 供电,首次将 ADON 位置 1 时,会将 ADC 从掉电模式中唤醒。

将 ADON 位清零来停止转换并使 ADC 进入掉电模式,在此模式下, ADC 几乎不耗电(只有几 μA)。

0:禁止ADC转换并转至掉电模式

1:使能ADC

采样时间寄存器 ADC_SMPR1、ADC_SMPR2

- 位 31:27 保留,必须保持复位值。

- 位 26:0 SMPx[2:0]: 通道 X 采样时间选择 (Channel x sampling time selection)

通过软件写入这些位可分别为各个通道选择采样时间。在采样周期期间,通道选择位必须保持不变。

000: 3 个周期

001: 15 个周期

010: 28 个周期

011: 56 个周期

100: 84 个周期

101: 112 个周期

110: 144 个周期

111: 480 个周期

- 位 31:30 保留,必须保持复位值。

- 位 29:0 SMPx[2:0]: 通道 X 采样时间选择 (Channel x sampling time selection)

通过软件写入这些位可分别为各个通道选择采样时间。在采样周期期间,通道选择位必须保

持不变。

000: 3 个周期

001: 15 个周期

010: 28 个周期

011: 56 个周期

100: 84 个周期

101: 112 个周期

110: 144 个周期

111: 480 个周期

注入通道偏移寄存器 ADC_JOFRx (x=1…4)

- 位 31:12 保留,必须保持复位值

- 位 11:0 JOFFSETx[11:0]: 注入通道 X 的数据偏移 (Data offset for injected channel x)

通过软件写入这些位可定义在转换注入通道时从原始转换数据中减去的偏移量。可从ADC_JDRx 寄存器中读取转换结果。

看门狗阈值寄存器 ADC_HTR、ADC_LTR

- 位 31:12 保留,必须保持复位值

- 位 11:0 HT[11:0]: 模拟看门狗高阈值 (Analog watchdog higher threshold)

通过软件写入这些位可为模拟看门狗定义高阈值。

- 位 31:12 保留,必须保持复位值

- 位 11:0 LT[11:0]: 模拟看门狗低阈值 (Analog watchdog lower threshold)

通过软件写入这些位可为模拟看门狗定义低阈值。

规则序列寄存器 ADC_SQR1、ADC_SQR2、ADC_SQR3

- 位 31:24 保留,必须保持复位值

- 位 23:20 L[3:0]: 规则通道序列长度 (Regular channel sequence length)

通过软件写入这些位可定义规则通道转换序列中的转换总数。

0000: 1 次转换

0001: 2 次转换

…

1111: 16 次转换- 位 19:15 SQ16[4:0]: 规则序列中的第十六次转换 (16th conversion in regular sequence)

通过软件写入这些位,并将通道编号 (0…18) 分配为转换序列中的第十六次转换。- 位 14:10 SQ15[4:0]: 规则序列中的第十五次转换 (15th conversion in regular sequence)

- 位 9:5 SQ14[4:0]: 规则序列中的第十四次转换 (14th conversion in regular sequence)

- 位 4:0 SQ13[4:0]: 规则序列中的第十三次转换 (13th conversion in regular sequence)

- 位 31:30 保留,必须保持复位值

- 位 29:26 SQ12[4:0]: 规则序列中的第十二次转换 (12th conversion in regular sequence)

通过软件写入这些位,并将通道编号 (0…18) 分配为序列中的第十二次转换。- 位 24:20 SQ11[4:0]: 规则序列中的第十一次转换 (11th conversion in regular sequence)

- 位 19:15 SQ10[4:0]: 规则序列中的第十次转换 (10th conversion in regular sequence)

- 位 14:10 SQ9[4:0]: 规则序列中的第九次转换 (9th conversion in regular sequence)

- 位 9:5 SQ8[4:0]: 规则序列中的第八次转换 (8th conversion in regular sequence)

- 位 4:0 SQ7[4:0]: 规则序列中的第七次转换 (7th conversion in regular sequence)

- 位 31:30 保留,必须保持复位值

- 位 29:25 SQ6[4:0]: 规则序列中的第六次转换 (6th conversion in regular sequence)

通过软件写入这些位,并将通道编号 (0…18) 分配为序列中的第六次转换。- 位 24:20 SQ5[4:0]: 规则序列中的第五次转换 (5th conversion in regular sequence)

- 位 19:15 SQ4[4:0]: 规则序列中的第四次转换 (4th conversion in regular sequence)

- 位 14:10 SQ3[4:0]: 规则序列中的第三次转换 (3rd conversion in regular sequence)

- 位 9:5 SQ2[4:0]: 规则序列中的第二次转换 (2nd conversion in regular sequence)

- 位 4:0 SQ1[4:0]: 规则序列中的第一次转换 (1st conversion in regular sequence)

注入序列寄存器 ADC_JDRx

- 位 31:22 保留,必须保持复位值

- 位 21:20 JL[1:0]: 注入序列长度 (Injected sequence length)

通过软件写入这些位可定义注入通道转换序列中的转换总数。

00: 1 次转换

01: 2 次转换

10: 3 次转换

11: 4 次转换- 位 19:15 JSQ4[4:0]: 注入序列中的第四次转换 (4th conversion in injected sequence)

(当 JL[1:0] = 3 时,请参见下方的注释)

通过软件写入这些位,并将通道编号 (0…18) 分配为序列中的第四次转换。- 位 14:10 JSQ3[4:0]: 注入序列中的第三次转换 (3rd conversion in injected sequence)

(当 JL[1:0] = 3 时,请参见下方的注释)- 位 9:5 JSQ2[4:0]: 注入序列中的第二次转换 (2nd conversion in injected sequence)

(当 JL[1:0] = 3 时,请参见下方的注释)- 位 4:0 JSQ1[4:0]: 注入序列中的第一次转换 (1st conversion in injected sequence)

(当 JL[1:0] = 3 时,请参见下方的注释)- 注意

当 JL[1:0] = 3(定序器中有 4 次注入转换)时, ADC 将按以下顺序转换通道: JSQ1[4:0]、JSQ2[4:0]、 JSQ3[4:0] 和 JSQ4[4:0]。

当 JL = 2(定序器中有 3 次注入转换)时, ADC 将按以下顺序转换通道: JSQ2[4:0]、JSQ3[4:0] 和 JSQ4[4:0]。

当 JL = 1(定序器中有 2 次注入转换)时, ADC 转换通道的顺序为:先是 JSQ3[4:0],而后是JSQ4[4:0]。

当 JL = 0(定序器中有 1 次注入转换)时, ADC 将仅转换 JSQ4[4:0] 通道。

规则数据寄存器 ADC_DR

- 位 31:16 保留,必须保持复位值

- 位 15:0 DATA[15:0]: 规则数据 (Regular data)

这些位为只读。它们包括来自规则通道的转换结果。数据有左对齐和右对齐两种方式。

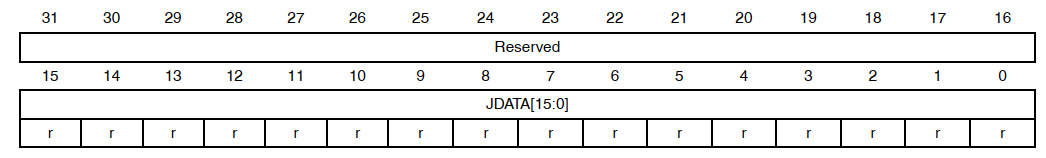

注入数据寄存器 ADC_JSQR

- 位 31:16 保留,必须保持复位值。

- 位 15:0 JDATA[15:0]: 注入数据 (Injected data)

这些位为只读。它们包括来自注入通道 X 的转换结果。 数据有左对齐和右对齐两种方式。

通用状态寄存器 ADC_CSR

- 位 31:22 保留,必须保持复位值

- 位 21 OVR3: ADC3 的溢出标志 (Overrun flag of ADC3)

该位是 ADC3_SR 寄存器中 OVR 位的副本。- 位 20 STRT3: ADC3 的规则通道开始标志 (Regular channel Start flag of ADC3)

该位是 ADC3_SR 寄存器中 STRT 位的副本。- 位 19 JSTRT3: ADC3 的注入通道开始标志 (Injected channel Start flag of ADC3)

该位是 ADC3_SR 寄存器中 JSTRT 位的副本。- 位 18 JEOC3: ADC3 的注入通道转换结束 (Injected channel end of conversion of ADC3)

该位是 ADC3_SR 寄存器中 JEOC 位的副本。- 位 17 EOC3: ADC3 的转换结束 (End of conversion of ADC3)

该位是 ADC3_SR 寄存器中 EOC 位的副本。- 位 16 AWD3: ADC3 的模拟看门狗标志 (Analog watchdog flag of ADC3)

该位是 ADC3_SR 寄存器中 AWD 位的副本。- 位 15:14 保留,必须保持复位值

- 位 13 OVR2: ADC2 的溢出标志 (Overrun flag of ADC2)

该位是 ADC2_SR 寄存器中 OVR 位的副本。- 位 12 STRT2: ADC2 的规则通道开始标志 (Regular channel Start flag of ADC2)

该位是 ADC2_SR 寄存器中 STRT 位的副本。- 位 11 JSTRT2: ADC2 的注入通道开始标志 (Injected channel Start flag of ADC2)

该位是 ADC2_SR 寄存器中 JSTRT 位的副本。- 位 10 JEOC2: ADC2 的注入通道转换结束 (Injected channel end of conversion of ADC2)

该位是 ADC2_SR 寄存器中 JEOC 位的副本。- 位 9 EOC2: ADC2 转换结束 (End of conversion of ADC2)

该位是 ADC2_SR 寄存器中 EOC 位的副本。- 位 8 AWD2: ADC2 的模拟看门狗标志 (Analog watchdog flag of ADC2)

该位是 ADC2_SR 寄存器中 AWD 位的副本。- 位 7:6 保留,必须保持复位值

- 位 5 OVR1: ADC1 的溢出标志 (Overrun flag of ADC1)

该位是 ADC1_SR 寄存器中 OVR 位的副本。- 位 4 STRT1: ADC1 的规则通道开始标志 (Regular channel Start flag of ADC1)

该位是 ADC1_SR 寄存器中 STRT 位的副本。- 位 3 JSTRT1: ADC1 的注入通道开始标志 (Injected channel Start flag of ADC1)

该位是 ADC1_SR 寄存器中 JSTRT 位的副本。- 位 2 JEOC1: ADC1 的注入通道转换结束 (Injected channel end of conversion of ADC1)

该位是 ADC1_SR 寄存器中 JEOC 位的副本。- 位 1 EOC1: ADC1 的转换结束 (End of conversion of ADC1)

该位是 ADC1_SR 寄存器中 EOC 位的副本。- 位 0 AWD1: ADC1 的模拟看门狗标志 (Analog watchdog flag of ADC1)

该位是 ADC1_SR 寄存器中 AWD 位的副本。

通用控制寄存器 ADC_CCR

- 位31:24保留,必须保持复位值

- 位23 TSVREFE:温度传感器和VREFINT使能(Temperature sensor and VREFINT enable)

通过软件将该位置1和清零可使能/禁止温度传感器和VREFINT通道。

0:禁止温度传感器和VREFINT通道

1:使能温度传感器和VREFINT通道

对于STM32F42x 和STM32F43x 器件,当TSVREFE位置1时必须禁止VBATE。两个位同时置1时,仅进行VBAT转换。- 位22 VBATE:VBAT使能(VBAT enable)

通过软件将该位置1和清零可使能/禁止 VBAT通道。

0:禁止VBAT通道

1:使能VBT通道- 位21:18 保留,必须保持复位值

- 位17:16ADCPRE:ADC预分频器(ADCprescaler)

由软件置1和清零,以选择ADC的时钟频率。该时钟为所有ADC所共用。

00:PCLK2:2分频

01:PCLK2:4分频

10: PCLK2:6分频

11: PCLK2:8分频- 位15:14 DMA:直接存储器访问模式(对于多个ADC模式)(Direct memory access mode for multi ADC mode)

此位由软件置1和清零。有关详细信息,请参见DMA控制器一节。

00:禁止 DMA模式

01:使能DMA模式1(依次2/3半字-1、2、3依次进行)

10:使能DMA模式2(成对2/3半字-2和1、1和3、3和2依次进行)

11:使能DMA模式3(成对2/3字节-2和1、1和3、3和2依次进行)- 位13 DDS:DMA禁止选择(对于多个ADC模式)(DMA disable selection (for multi-ADC mode))

此位由软件置1和清零。

0:最后一次传输后不发出新的DMA请求(在DMA 控制器中进行配置)DMA位不通过硬件清零,但必须在生成新的DMA请求前,通过软件清零并设置为需要的模式。

1:只要数据发生转换且DMA = 01、10或11,便会发出 DMA请求。- 位12保留,必须保持复位值。

- 位11:8 DELAY:2个采样阶段之间的延迟(Delay between 2 sampling phases)

由软件置1和清零。这些位在双重或三重交错模式下使用。

0000: 5 * TADCCLK

0001: 6 * TADCCLK

0010: 7 * TADCCLK

…

1111:20 * TADCCLK- 位7:5 保留,必须保持复位值

- 位4:0 MULTI[4:0]:多重ADC模式选择(Multi ADC mode selection)

通过软件写入这些位可选择操作模式,所有ADC均独立。

00000:独立模式

00001到01001:双重模式,ADC1和ADC2一起工作,ADC3独立

00001:规则同时+注入同时组合模式

00010:规则同时+交替触发组合模式

00011:Reserved

00101:仅注入同时模式

00110:仅规则同时模式仅交错模式

01001:仅交替触发模式

10001到11001:三重模式:ADC1、ADC2和 ADC3一起工作

10001:规则同时+注入同时组合模式

10010:规则同时+交替触发组合模式

10011: Reserved

10101:仅注入同时模式

10110:仅规则同时模式仅交错模式

仅交错模式

11001:仅交替触发模式

其它所有组合均需保留且不允许编程

在多重模式下,更改通道配置会生成中止,进而导致同步丢失。建议在更改配置前禁用多重ADC模式。

适用于双重和三重模式的ADC通用规则数据寄存器 ADC_CDR

- 位 31:16 DATA2[15:0]: 规则转换对中的第二个数据项 (2nd data item of a pair of regular conversions)

在双重模式下,这些位包含 ADC2 的规则数据。请参见双重 ADC 模式。

在三重模式下,这些位还可以包含 ADC2、 ADC1 和 ADC3 的规则数据。请参见三重 ADC

模式。- 位 15:0 DATA1[15:0]:规则转换对中的第一个数据项 (1st data item of a pair of regular conversions)

在双重模式下,这些位包含 ADC1 的规则数据。请参见双重 ADC 模式。

在三重模式下,这些位还可以包含 ADC1、 ADC3 和 ADC2 的规则数据。请参见三重 ADC

模式。

【 19. 例程 】

//adc.c

#include "adc.h"

#include "delay.h"

//初始化ADC

void Adc_Init(void)

{

GPIO_InitTypeDef GPIO_InitStructure;

ADC_CommonInitTypeDef ADC_CommonInitStructure;

ADC_InitTypeDef ADC_InitStructure;

RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_GPIOA, ENABLE);//使能GPIOA时钟

RCC_APB2PeriphClockCmd(RCC_APB2Periph_ADC1, ENABLE); //使能ADC1时钟

//先初始化ADC1通道5 IO口

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_5;//PA5 通道5

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AN;//模拟输入

GPIO_InitStructure.GPIO_PuPd = GPIO_PuPd_NOPULL ;//不带上下拉

GPIO_Init(GPIOA, &GPIO_InitStructure);//初始化

RCC_APB2PeriphResetCmd(RCC_APB2Periph_ADC1,ENABLE); //ADC1复位

RCC_APB2PeriphResetCmd(RCC_APB2Periph_ADC1,DISABLE); //复位结束

ADC_CommonInitStructure.ADC_Mode = ADC_Mode_Independent;//独立模式

ADC_CommonInitStructure.ADC_TwoSamplingDelay = ADC_TwoSamplingDelay_5Cycles;//两个采样阶段之间的延迟5个时钟

ADC_CommonInitStructure.ADC_DMAAccessMode = ADC_DMAAccessMode_Disabled; //DMA失能

ADC_CommonInitStructure.ADC_Prescaler = ADC_Prescaler_Div4;//预分频4分频。ADCCLK=PCLK2/4=84(APB2)/4=21Mhz,ADC时钟最好不要超过36Mhz

ADC_CommonInit(&ADC_CommonInitStructure);//初始化

ADC_InitStructure.ADC_Resolution = ADC_Resolution_12b;//12位模式

ADC_InitStructure.ADC_ScanConvMode = DISABLE;//非扫描模式

ADC_InitStructure.ADC_ContinuousConvMode = DISABLE;//关闭连续转换

ADC_InitStructure.ADC_ExternalTrigConvEdge = ADC_ExternalTrigConvEdge_None;//禁止触发检测,使用软件触发

ADC_InitStructure.ADC_DataAlign = ADC_DataAlign_Right;//右对齐

ADC_InitStructure.ADC_NbrOfConversion = 1;//1个转换在规则序列中 也就是只转换规则序列1

ADC_Init(ADC1, &ADC_InitStructure);//ADC初始化

ADC_Cmd(ADC1, ENABLE);//开启AD转换器

}

//获得ADC值

//ch: @ref ADC_channels

//通道值 0~16取值范围为:ADC_Channel_0~ADC_Channel_16

//返回值:转换结果

u16 Get_Adc(u8 ch)

{

//设置指定ADC的规则组通道,一个序列,采样时间

ADC_RegularChannelConfig(ADC1, ch, 1, ADC_SampleTime_480Cycles ); //ADC1,ADC通道,480个周期,提高采样时间可以提高精确度

ADC_SoftwareStartConv(ADC1); //使能指定的ADC1的软件转换启动功能

while(!ADC_GetFlagStatus(ADC1, ADC_FLAG_EOC ));//等待转换结束

return ADC_GetConversionValue(ADC1); //返回最近一次ADC1规则组的转换结果

}

//获取通道ch的转换值,取times次,然后平均

//ch:通道编号

//times:获取次数

//返回值:通道ch的times次转换结果平均值

u16 Get_Adc_Average(u8 ch,u8 times)

{

u32 temp_val=0;

u8 t;

for(t=0;t<times;t++)

{

temp_val+=Get_Adc(ch);

delay_ms(5);

}

return temp_val/times;

}

//main.c

#include "sys.h"

#include "delay.h"

#include "usart.h"

#include "lcd.h"

#include "adc.h"

int main(void)

{

u16 adcx;

float temp;

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_2);//设置系统中断优先级分组2

delay_init(168); //初始化延时函数

uart_init(115200); //初始化串口波特率为115200

LCD_Init(); //初始化LCD接口

Adc_Init(); //初始化ADC

POINT_COLOR=RED;

LCD_ShowString(30,70,200,16,16,"ADC TEST");

POINT_COLOR=BLUE;//设置字体为蓝色

LCD_ShowString(30,130,200,16,16,"ADC1_CH5_VAL:");

LCD_ShowString(30,150,200,16,16,"ADC1_CH5_VOL:0.000V"); //先在固定位置显示小数点

while(1)

{

adcx=Get_Adc_Average(ADC_Channel_5,20);//获取通道5的转换值,20次取平均

LCD_ShowxNum(134,130,adcx,4,16,0); //显示ADCC采样后的原始值

temp=(float)adcx*(3.3/4096); //获取计算后的带小数的实际电压值,比如3.1111

adcx=temp; //赋值整数部分给adcx变量,因为adcx为u16整形

LCD_ShowxNum(134,150,adcx,1,16,0); //显示电压值的整数部分,3.1111的话,这里就是显示3

temp-=adcx; //把已经显示的整数部分去掉,留下小数部分,比如3.1111-3=0.1111

temp*=1000; //小数部分乘以1000,例如:0.1111就转换为111.1,相当于保留三位小数。

LCD_ShowxNum(150,150,temp,3,16,0X80); //显示小数部分(前面转换为了整形显示),这里显示的就是111.

delay_ms(250);

}

}

3874

3874

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?