输入序列连续的序列检测

描述

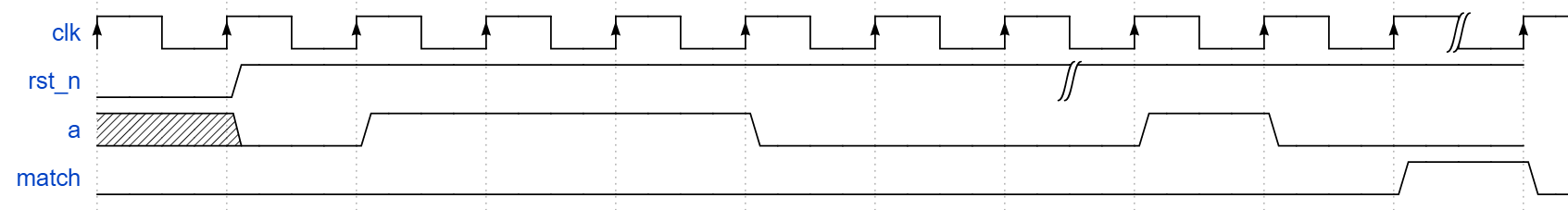

请编写一个序列检测模块,检测输入信号a是否满足01110001序列,当信号满足该序列,给出指示信号match。

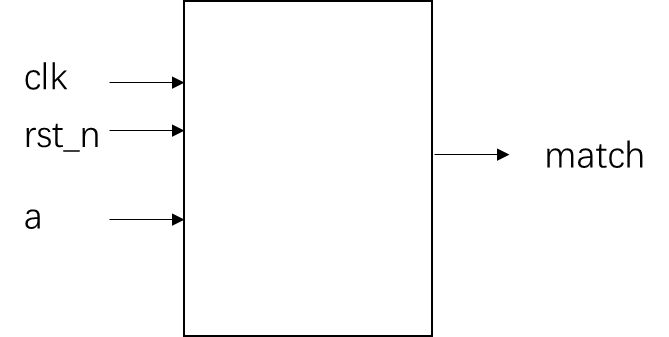

模块的接口信号图如下:

模块的时序图如下:

请使用Verilog HDL实现以上功能,并编写testbench验证模块的功能

输入描述:

clk:系统时钟信号

rst_n:异步复位信号,低电平有效

a:单比特信号,待检测的数据

输出描述:

match:当输入信号a满足目标序列,该信号为1,其余时刻该信号为0

解题思路

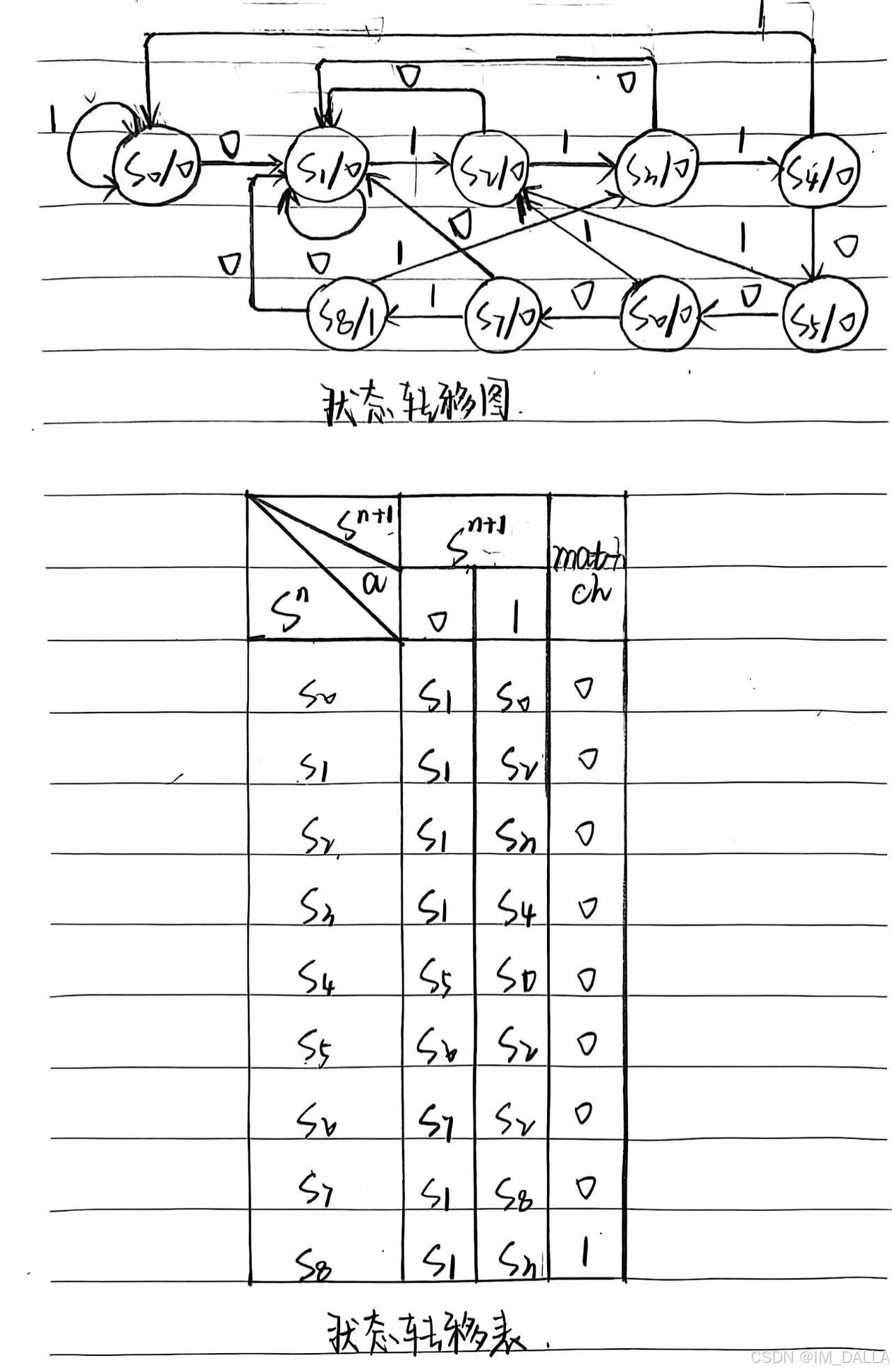

思路一:经典有限状态机三段式

可设置以下状态:

IDLE(S0):初始状态,表示电路还没有收到任何一个有效数值;

S1:表示电路收到一个有效的“0”;

S2:表示电路收到两个有效的“01”;

S3:表示电路收到三个有效的“011”;

S4:表示电路收到四个有效的“0111”;

S5:表示电路收到五个有效的“01110”;

S6:表示电路收到六个有效的“011100”;

S7:表示电路收到七个有效的“0111000”;

S8:表示电路收到七个有效的“01110001”;

根据输出表述,“当输入信号a满足目标序列时,match信号为1,”因此可画出如下所示的状态转移图和状态转移表;

格雷码的相关知识

Gray码也称为循环码,其最基本的特性是任何相邻的两组代码中,仅有一位数码不同,因而又称为单位距离码。减少了产生毛刺和一些暂态的可能。

Gray码的编码方式有多种,典型的格雷码如下所示:

| 十进制数 | 二进制码 | Gray码 | ||||||

| B3 | B2 | B1 | B0 | G3 | G2 | G | ||

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1453

1453

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?