STM32时钟树及时钟配置方法

时钟系统是CPU的脉搏,就像人的心脏一样,所以时钟系统十分的重要。由于STM32本身十分复杂,不像简单的51单片机一个时钟系统就可以解决问题,而且STM32的外设十分的多,但是不是所有的外设都需要系统时钟这么高的频率。同一个电路,时钟越快功耗越大,抗干扰能力越弱,较为复杂的MCU都采用的多时钟源的方式解决问题。

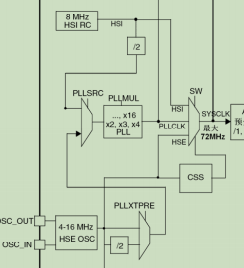

时钟系统框图

STM32 有5个时钟源:HSI、HSE、LSI、LSE、PLL。

①、HSI是高速内部时钟,RC振荡器,频率为8MHz,精度不高。

②、HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

③、LSI是低速内部时钟,RC振荡器,频率为40kHz,提供低功耗时钟。至独立看门狗

④、LSE是低速外部时钟,接频率为32.768kHz的石英晶体RTC

⑤、PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。倍频可选择为2~16倍,但是其输出频率最大不得超72MHz。

1. 系统时钟SYSCLK可来源于三个时钟源

①、HSI振荡器时钟,2分频后经过选择器做PLL时钟源

②、HSE振荡器时钟,可经过两个选择器做PLL时钟源,也可以先2分频后再经过两个选择器,频率范围为4MHz~16MHz。

③、PLL时钟,倍频后可作系统时钟,倍频系数可为2~16,最大不超过72MHZ

STM32可以选择一个时钟信号输出到MCO脚(PA8)上,可以选择为PLL输出的2分频、HSI、HSE、或者系统时钟。

任何一个外设在使用之前,必须首先使能其相应的时钟。

STM32S时钟配置方法

可通过系统架构查看外设挂在哪个时钟下

这里总结一下 SystemInit()函数中设置的系统时钟SYSCLK(系统时钟) =72MHz

AHB 总线时钟(使用 SYSCLK) =72MHz

APB1 总线时钟(PCLK1) =36MHz

APB2 总线时钟(PCLK2) =72MHz

PLL 时钟 =72MHz

我们系统默认宏定义是 72MHz:在system_stm32f10x.c的开头进行了宏定义

5332

5332

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?